adf4116/adf4117/adf4118

–

9

–

rev. 0

第一 涉及 spur

–

dBc

–

60

–

80

–

90

–

70

温度

–

C

0 20406080100

V

DD

= 3v

V

P

= 5v

–

100

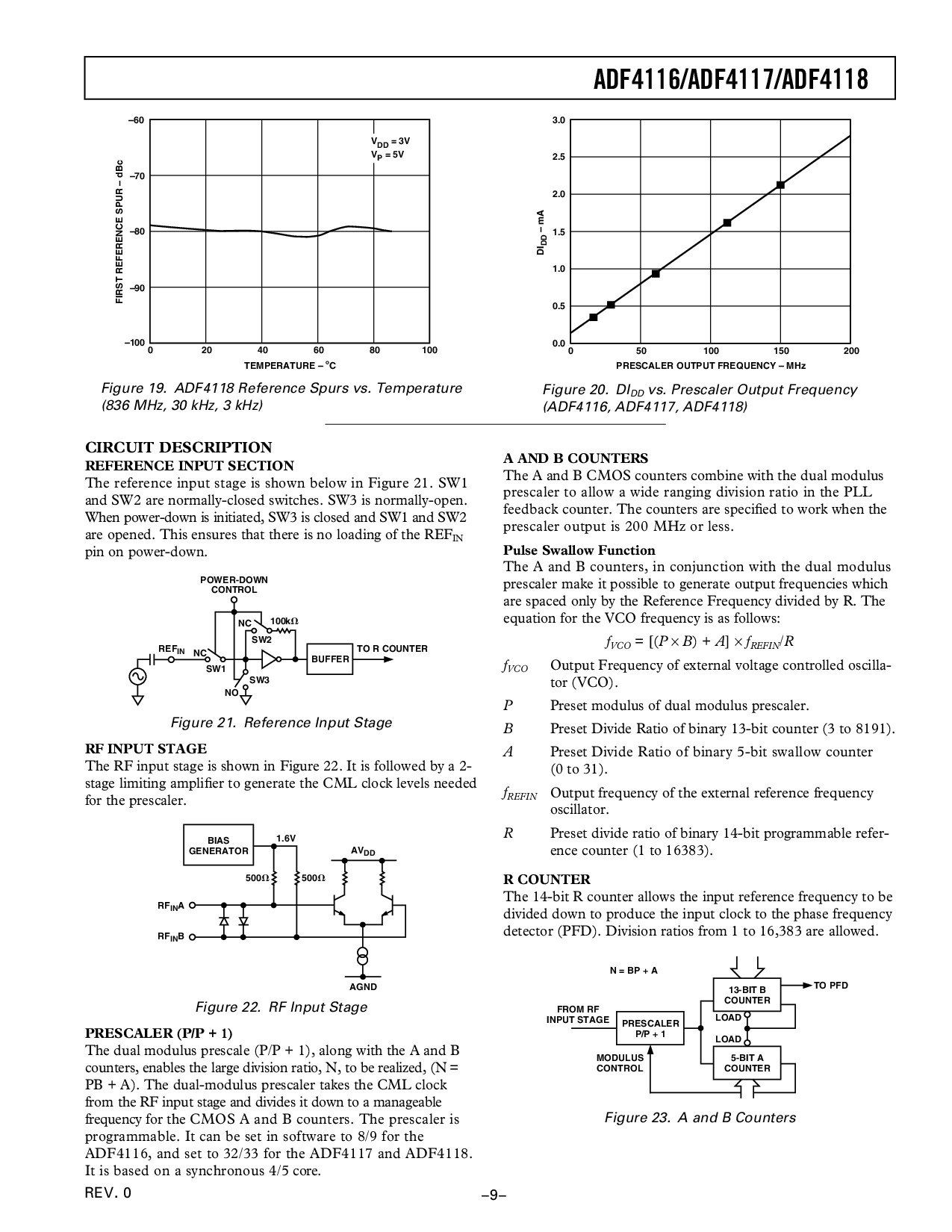

图示 19. adf4118 涉及 spurs vs. 温度

(836 mhz, 30 khz, 3 khz)

电路 描述

涉及 输入 部分

这 涉及 输入 平台 是 显示 在下 在 图示 21. sw1

和 sw2 是 正常情况下-关闭 switches. sw3 是 正常情况下-打开.

当 电源-向下 是 initiated, sw3 是 关闭 和 sw1 和 sw2

是 opened. 这个 确保 那 那里 是 非 加载 的 这 ref

在

管脚 在 电源-向下.

缓存区

至 r 计数器

REF

在

100k

NC

SW2

SW3

非

NC

SW1

电源-向下

控制

图示 21. 涉及 输入 平台

rf 输入 平台

这 rf 输入 平台 是 显示 在 图示 22. 它 是 followed 用 一个 2-

平台 限制的 amplifier 至 发生 这 cml 时钟 水平 需要

为 这 预分频器.

AV

DD

AGND

500

500

1.6v

偏差

发生器

RF

在

一个

RF

在

B

图示 22. rf 输入 平台

预分频器 (p/p + 1)

这 双 modulus prescale (p/p + 1), along 和 这 一个 和 b

counters, 使能 这 大 分隔 比率, n, 至 是 认识到, (n =

铅 + 一个). 这 双-modulus 预分频器 takes 这 cml 时钟

从这 rf 输入 平台 和 divides 它 向下 至 一个 manageable

频率为 这cmos 一个 和 b counters. 这 预分频器 是

可编程序的. 它 能 是 设置 在 软件 至 8/9 为 这

adf4116, 和 设置 至 32/33 为 这 adf4117 和 adf4118.

它 是 为基础 在 一个 同步的 4/5核心.

一个 和 b counters

这 一个 和 b cmos counters 联合的 和 这 双 modulus

预分频器 至 准许 一个 宽 ranging 分隔 比率 在 这 pll

feedback 计数器. 这 counters 是 specified 至 工作 当 这

预分频器 输出 是 200 mhz 或者 较少.

脉冲波 swallow 函数

这 一个 和 b counters, 在 conjunction 和 这 双 modulus

预分频器 制造 它 可能 至 发生 输出 发生率 这个

是 排列 仅有的 用 这 涉及 频率 分隔 用 r. 这

等式 为 这 vco 频率 是 作 跟随:

f

VCO

= [(

P

×

B

) +

一个

]

×

f

REFIN

/

R

f

VCO

输出 频率 的 外部 电压 控制 oscilla-

tor (vco).

P

preset modulus 的 双 modulus 预分频器.

B

preset 分隔 比率 的 二进制的 13-位 计数器 (3 至 8191).

一个

preset divide 比率 的 二进制的 5-位 swallow 计数器

(0 至 31).

f

REFIN

输出 频率 的 这 外部 涉及 频率

振荡器.

R

preset 分隔 比率 的 二进制的 14-位 可编程序的 谈及-

ence 计数器 (1 至 16383).

r 计数器

这 14-位 r 计数器 准许 这 输入 涉及 频率 至 是

分隔 向下 至 生产 这 输入 时钟 至 这 阶段 频率

探测器 (pfd). 分隔 ratios 从 1 至 16,383 是 允许.

13-位 b

计数器

5-位 一个

计数器

预分频器

p/p + 1

从 rf

输入 平台

MODULUS

控制

n = bp + 一个

加载

加载

至 pfd

图示 23. 一个 和 b counters

0

DI

DD

–

毫安

0.0

预分频器 输出 频率

–

MHz

50 100 150 200

0.5

1.0

1.5

2.0

2.5

3.0

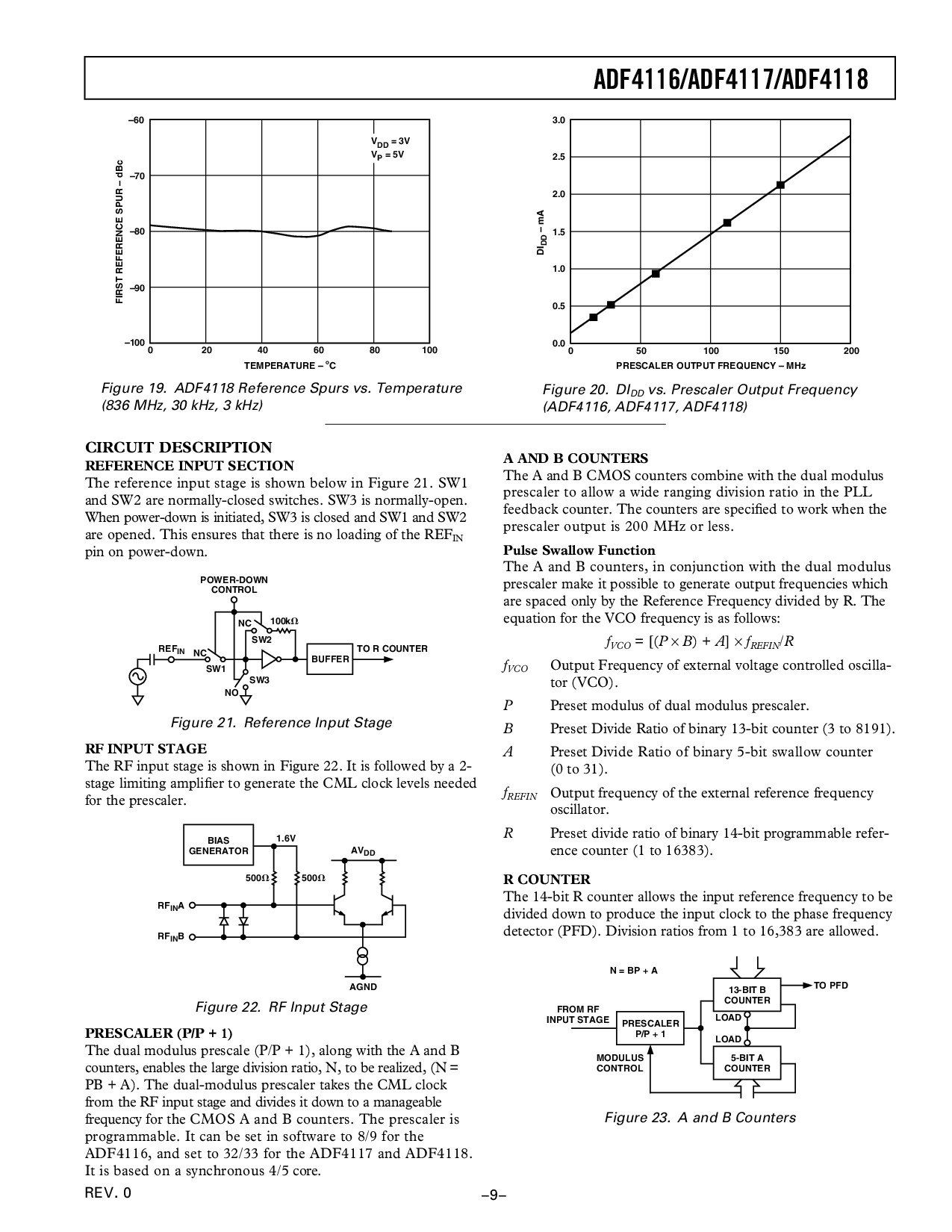

图示 20. DI

DD

vs. 预分频器 输出 频率

(adf4116, adf4117, adf4118)