IS42S16100C1

ISSI

®

6

整体的 硅 解决方案, 公司 — www.issi.com —

1-800-379-4774

rev. 一个

07/21/04

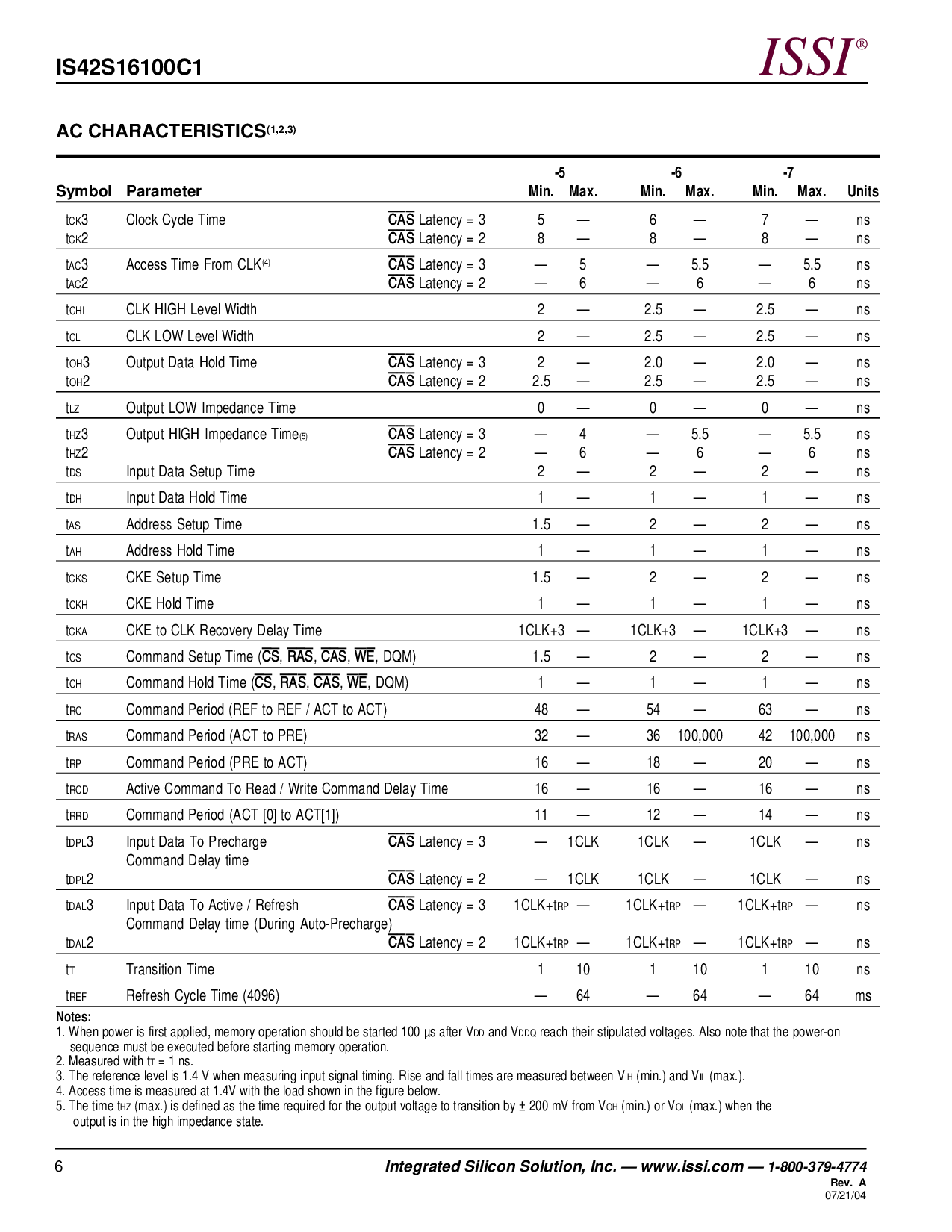

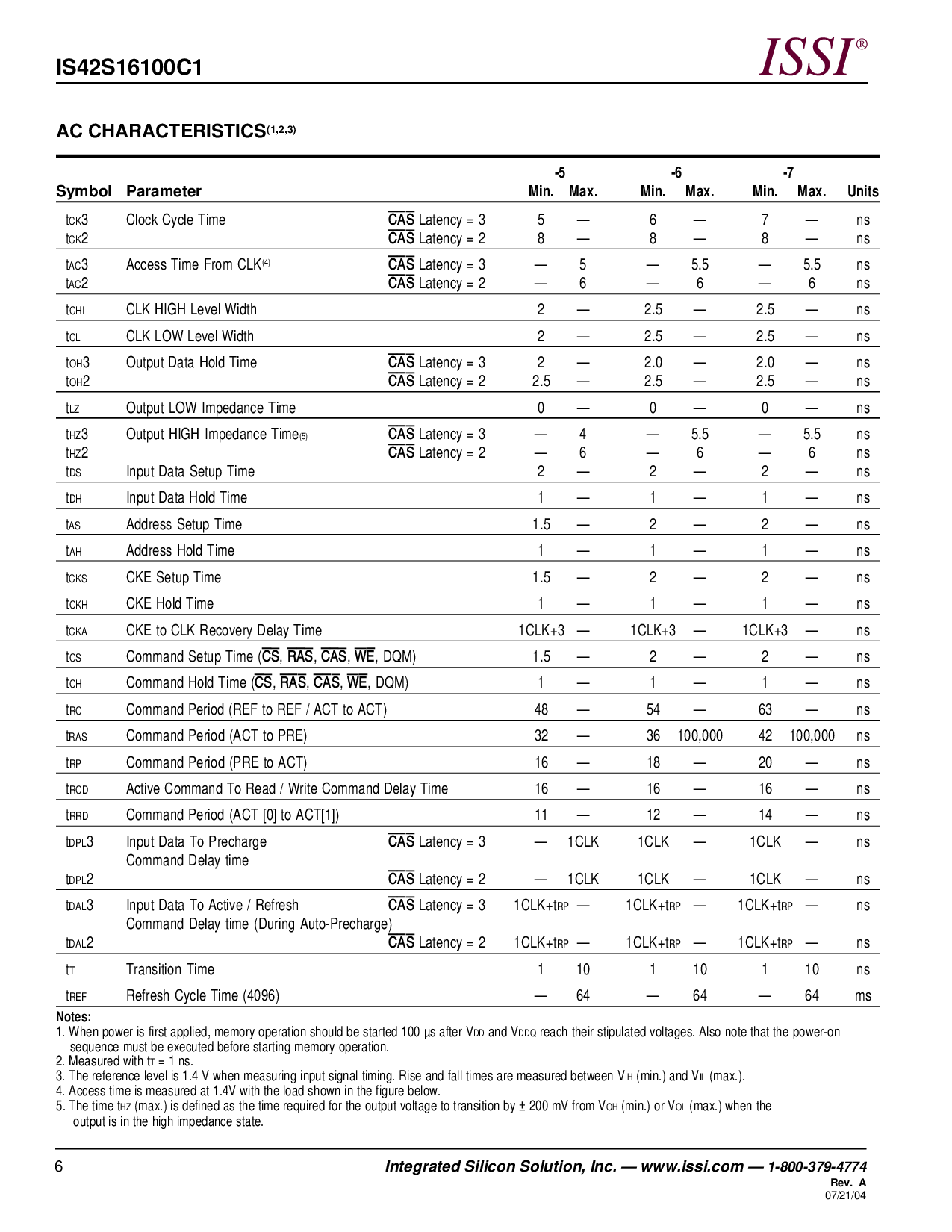

交流 特性

(1,2,3)

-5 -6 -7

标识 参数

最小值 最大值 最小值 最大值 最小值 最大值 单位

t

CK

3 时钟 循环 时间

CAS

latency = 3 5 — 6 — 7 — ns

t

CK

2

CAS

latency = 2 8 — 8 — 8 — ns

t

交流

3 进入 时间 从 clk

(4)

CAS

latency = 3 — 5 — 5.5 — 5.5 ns

t

交流

2

CAS

latency = 2 — 6 — 6 — 6 ns

t

CHI

clk 高 水平的 宽度 2 — 2.5 — 2.5 — ns

t

CL

clk 低 水平的 宽度 2 — 2.5 — 2.5 — ns

t

OH

3 输出 数据 支撑 时间

CAS

latency = 3 2 — 2.0 — 2.0 — ns

t

OH

2

CAS

latency = 2 2.5 — 2.5 — 2.5 — ns

t

LZ

输出 低 阻抗 时间 0 — 0 — 0 — ns

t

HZ

3 输出 高 阻抗 时间

(5)

CAS

latency = 3 — 4 — 5.5 — 5.5 ns

t

HZ

2

CAS

latency = 2 — 6 — 6 — 6 ns

t

DS

输入 数据 建制 时间 2 — 2 — 2 — ns

t

DH

输入 数据 支撑 时间 1 — 1 — 1 — ns

t

作

地址 建制 时间 1.5 — 2 — 2 — ns

t

AH

地址 支撑 时间 1 — 1 — 1 — ns

t

CKS

cke 建制 时间 1.5 — 2 — 2 — ns

t

CKH

cke 支撑 时间 1 — 1 — 1 — ns

t

CKA

cke 至 clk 恢复 延迟时间 1CLK+3 — 1CLK+3 — 1CLK+3 — ns

t

CS

command 建制 时间 (

CS

,

RAS

,

CAS

,

我们

, dqm) 1.5 — 2 — 2 — ns

t

CH

command 支撑 时间 (

CS

,

RAS

,

CAS

,

我们

, dqm) 1 — 1 — 1 — ns

t

RC

command 时期 (ref 至 ref / act 至 act) 48 — 54 — 63 — ns

t

RAS

command 时期 (act 至 前) 32 — 36 100,000 42 100,000 ns

t

RP

command 时期 (前 至 act) 16 — 18 — 20 — ns

t

RCD

起作用的 command 至 读 / 写 command 延迟 时间 16 — 16 — 16 — ns

t

RRD

command 时期 (act [0] 至 act[1]) 11 — 12 — 14 — ns

t

DPL

3 输入 数据 至 precharge

CAS

latency = 3 — 1CLK 1CLK — 1CLK — ns

command 延迟 时间

t

DPL

2

CAS

latency = 2 — 1CLK 1CLK — 1CLK — ns

t

DAL

3 输入 数据 至 起作用的 / refresh

CAS

latency =3 1CLK+t

RP

— 1CLK+t

RP

— 1CLK+t

RP

—ns

command 延迟 时间 (在 自动-precharge)

t

DAL

2

CAS

latency =2 1CLK+t

RP

— 1CLK+t

RP

— 1CLK+t

RP

—ns

t

T

转变 时间 1 10 1 10 1 10 ns

t

REF

refresh 循环 时间 (4096) — 64 — 64 — 64 ms

注释:

1. 当 电源 是 第一 应用, 记忆 运作 应当 是 started 100 µs 之后 v

DD

和 v

DDQ

reach 它们的 stipulated 电压. 也 便条 那 这 电源-在

sequence 必须 是 executed 在之前 开始 记忆 运作.

2. 量过的 和 t

T

= 1 ns.

3. 这 涉及 水平的 是 1.4 v 当 测量 输入 信号 定时. 上升 和 下降 时间 是 量过的 在 v

IH

(最小值.) 和 v

IL

(最大值.).

4. 进入 时间 是 量过的 在 1.4v 和 这 加载 显示 在 这 图示 在下.

5. 这 时间 t

HZ

(最大值.) 是 定义 作 这 时间 必需的 为 这 输出 电压 至 转变 用 ± 200 mv 从 v

OH

(最小值.) 或者 v

OL

(最大值.) 当 这

输出 是 在 这 高 阻抗 状态.