coolrunner-ii cpld 家族

ds090 (v2.5) 六月 28, 2005

www.xilinx.com

9

产品 规格

R

CoolCLOCK

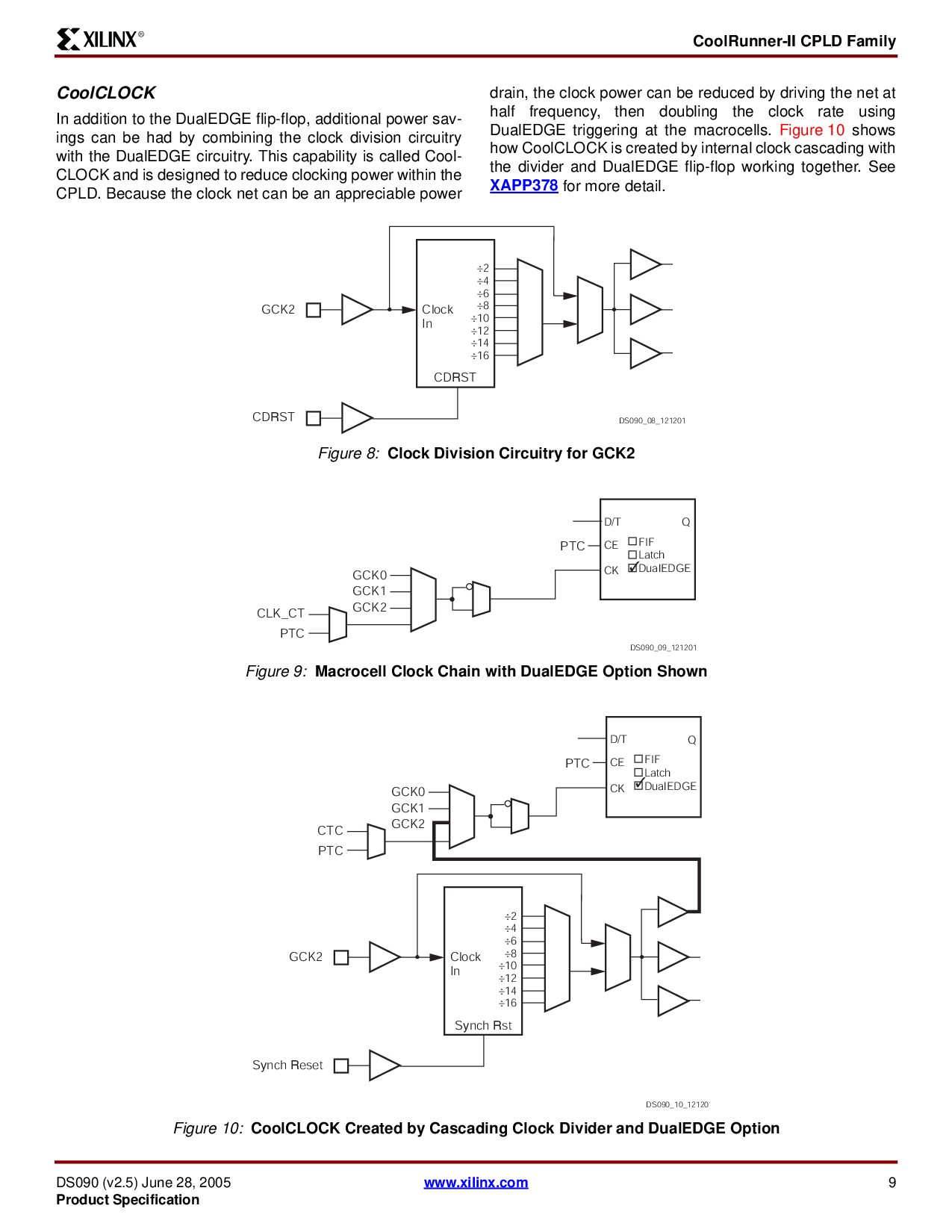

在 增加 至 这 dualedge flip-flop, 额外的 电源 sav-

ings 能 是 had 用 结合 这 时钟 分隔 电路系统

和 这 dualedge 电路系统. 这个 能力 是 called cool-

时钟 和 是 设计 至 减少 clocking 电源 在里面 这

cpld. 因为 这 时钟 网 能 是 一个 appreciable 电源

流, 这 时钟 电源 能 是 减少 用 驱动 这 网 在

half 频率, 然后 doubling 这 时钟 比率 使用

dualedge triggering 在 这 macrocells.图示 10显示

如何 coolclock 是 创建 用 内部的 时钟 cascading 和

这 分隔物 和 dualedge flip-flop working 一起. 看

XAPP378

为 更多 detail.

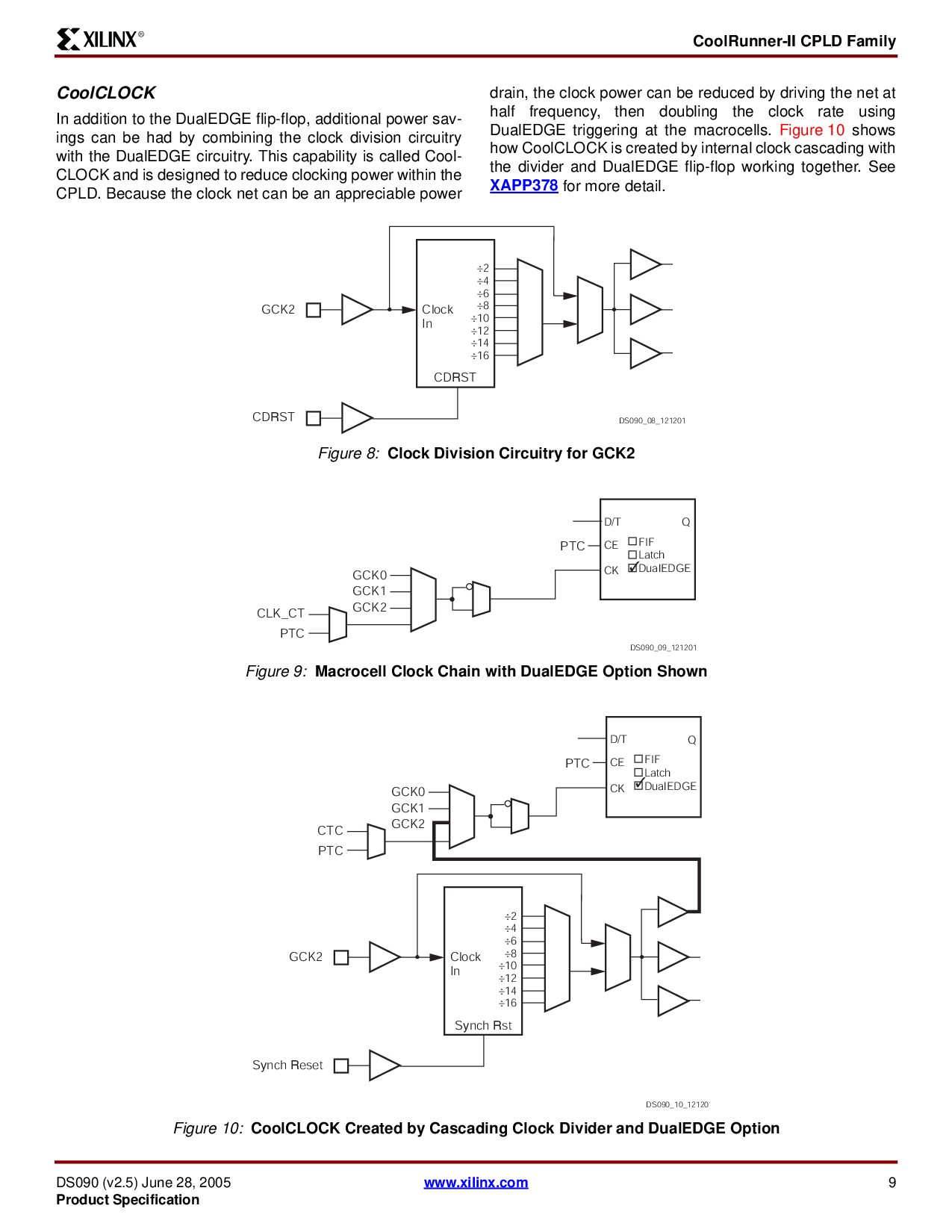

图示 8:

时钟 分隔 电路系统 为 gck2

图示 9:

macrocell 时钟 chain 和 dualedge 选项 显示

图示 10:

coolclock 创建 用 cascading clock 分隔物 和 dualedge 选项

ds090_08_121201

时钟

在

÷

2

÷

4

÷

6

÷

8

÷

10

÷

12

÷

14

÷

16

GCK2

CDRST

CDRST

GCK0

GCK1

GCK2

clk_ct

PTC

PTC

ds090_09_121201

d/t

CE

CK

FIF

获得

DualEDGE

Q

✓

GCK0

GCK1

GCK2

CTC

PTC

PTC

ds090_10_121201

d/t

CE

CK

FIF

获得

DualEDGE

Q

时钟

在

÷

2

÷

4

÷

6

÷

8

÷

10

÷

12

÷

14

÷

16

GCK2

synch 重置

synch rst

✓