–13–rev. 一个

adsp-21161n

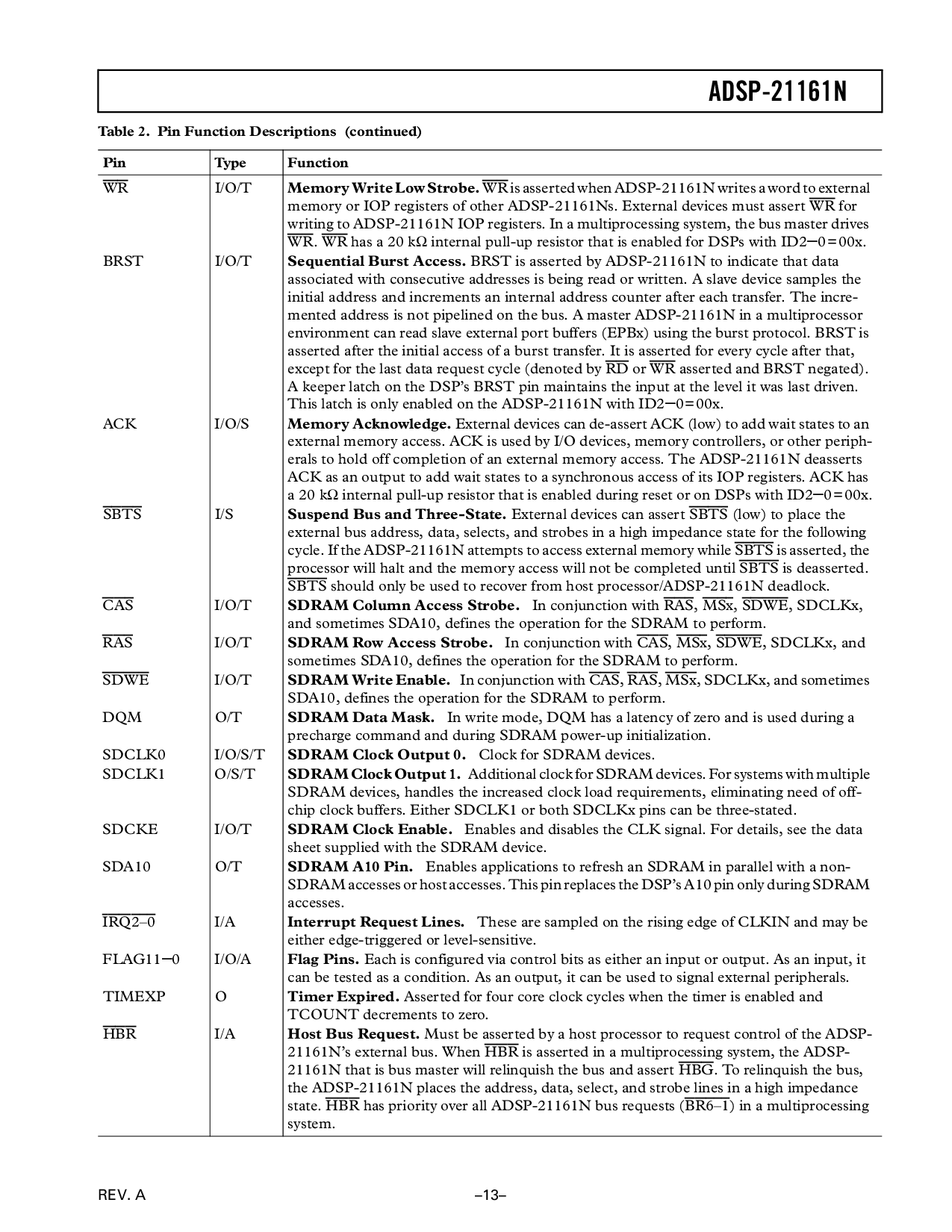

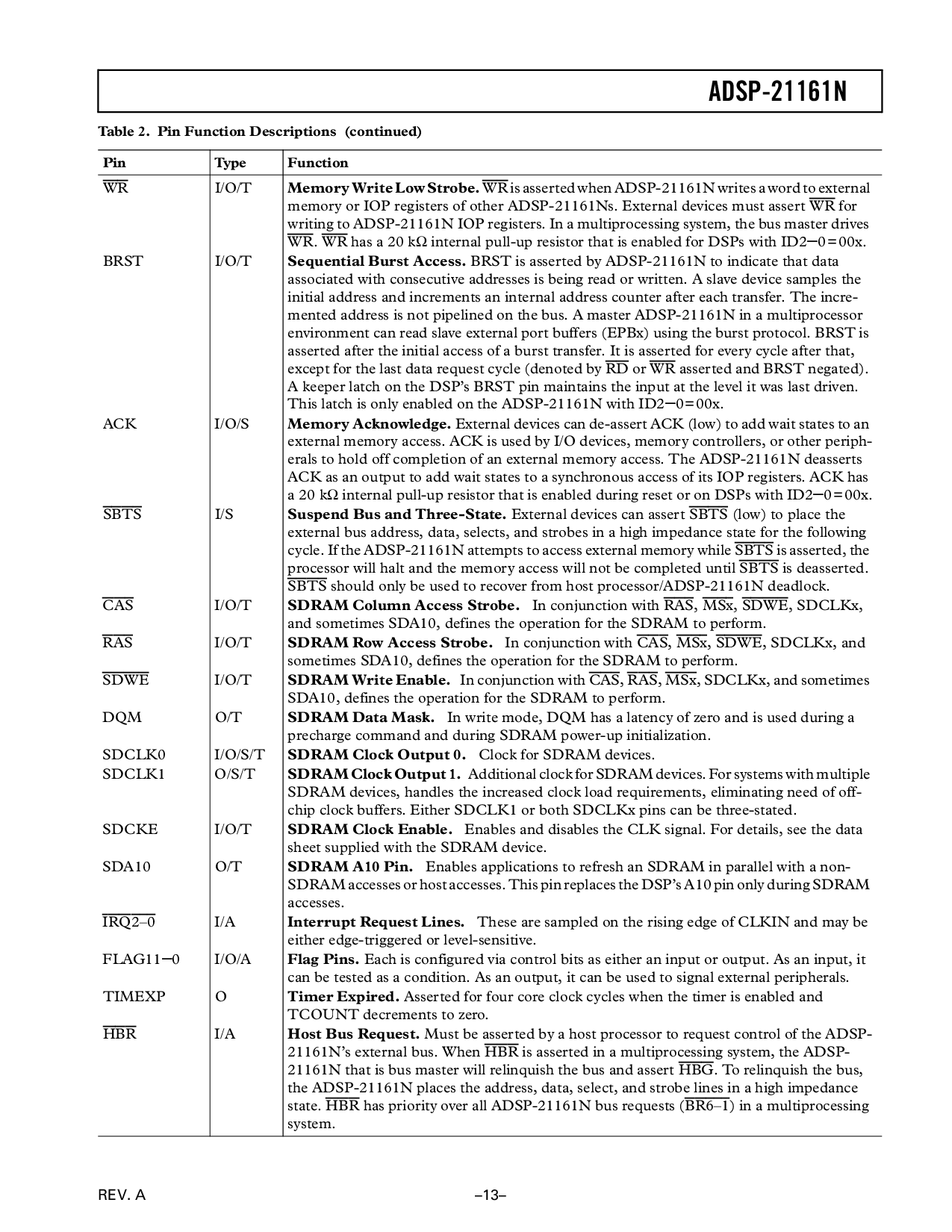

WR

i/o/t

记忆 写 低 strobe.

WR

是 asserted 当 adsp-21161n写 一个 文字 至 外部

记忆 或者 iop 寄存器 的 其它 adsp-21161ns. 外部 设备 必须 assert

WR

为

writing 至 adsp-21161n iop 寄存器. 在 一个 multiprocessing 系统, the 总线 主控 驱动

WR

.

WR

有 一个 20 k

Ω

内部的 拉-向上 电阻 那 是 使能 为 dsps 和 id2

–

0=00x.

BRST i/o/t

sequential burst 进入.

brst 是 asserted 用 adsp-21161n 至 表明 那 数据

有关联的 和 consecutive addresses 是 正在 读 或者 写. 一个 从动装置 设备 样本 这

最初的 地址 和 increments 一个 内部的 地址 counter 之后 各自 转移. 这 incre-

mented 地址 是 不 pipelined 在 这 总线. 一个 主控 adsp-21161n 在 一个 multiprocessor

环境 能 读 从动装置 外部 端口 buffers (epbx) 使用 这 burst 协议. brst 是

asserted 之后 这 initial 进入 的 一个 burst 转移. 它 是 asserted 为 每 循环 之后 那,

除了 为 这 last 数据 request 循环 (denoted 用

RD

或者

WR

asserted 和 brst negated).

一个 keeper 获得 在 这 dsp’s brst 管脚 维持s 这 输入 在 这 水平的 它 是 last 驱动.

这个 获得 是 仅有的 使能在 这 adsp-21161n 和 id2

–

0=00x.

ACK i/o/s

记忆 acknowledge.

外部 设备 能 de-assert ack(低) 至 增加 wait states 至 一个

外部 记忆 进入. ack 是 使用 用 i/o设备, memory 控制者, 或者 其它 periph-

erals 至 支撑 止 completion的 一个 外部 memory 进入. 这 adsp-21161n deasserts

ack 作 一个 输出 至 增加 wait states 至 一个 synchronous 进入 的 它的 iop 寄存器. ack 有

一个 20 k

Ω

internal 拉-向上 电阻 那 是 使能 在 重置 或者 在 dsps 和 id2

–

0=00x.

SBTS

i/s

suspend 总线 和 三-状态.

外部 设备 能 assert

SBTS

(低) 至 放置 这

外部 总线 地址, 数据, 选择, 和 strobes 在 一个 高 阻抗 状态 为 这 下列的

循环. 如果 这 adsp-21161n attempts至 进入 外部 记忆 当

SBTS

是 asserted, 这

处理器 将 halt 和 这 记忆进入 将 不 是 完成 直到

SBTS

是 deasserted.

SBTS

应当 仅有的 是 使用 至 recover from host 处理器/adsp-21161n deadlock.

CAS

i/o/t

sdram column 进入 strobe.

在 conjunction 和

RAS

,

MSx

,

SDWE

, sdclkx,

和 sometimes sda10, 定义 这 运作 为 这 sdram 至 执行.

RAS

i/o/t

sdram 行 进入 strobe.

在 conjunction 和

CAS

,

MSx

,

SDWE

, sdclkx, 和

sometimes sda10, 定义 这 运作 为 这 sdram 至 执行.

SDWE

i/o/t

sdram 写 使能.

在 conjunction 和

CAS

,

RAS

,

MSx

, sdclkx, 和 sometimes

sda10, 定义 这 运作 为 这 sdram 至 执行.

DQM o/t

sdram 数据 掩饰.

在 写 模式, dqm 有 一个 latency 的 零 和 是 使用 在 一个

precharge command 和 在 sdram 电源-向上 initialization.

SDCLK0 i/o/s/t

sdram 时钟 输出 0.

时钟 为 sdram 设备.

SDCLK1 o/s/t

sdram 时钟 输出 1.

额外的 时钟 为 sdram 设备. 为 系统 和 多样的

sdram 设备, handles 这 增加 时钟 load (所需的)东西, eliminating 需要 的 止-

碎片 时钟 缓存区. 也 sdclk1 或者 both sdclkx 管脚 can 是 三-陈述.

SDCKE i/o/t

sdram 时钟 使能.

使能 和 使不能运转 这 clk 信号. 为 详细信息, 看 这 数据

薄板 有提供的 和这 sdram 设备.

SDA10 o/t

sdram a10 管脚.

使能 产品 至 refresh 一个 sdram 在 并行的 和 一个 非-

sdram accesses 或者 hostaccesses. 这个 管脚 替代 这dsp’s a10 管脚 仅有的 在 sdram

accesses.

IRQ2–0

i/一个

中断 要求 线条.

这些 是 抽样 在 这 rising 边缘 的 clkin 和 将 是

也 边缘-triggered 或者 水平的-敏感的.

FLAG11

–

0 i/o/一个

标记 管脚.

各自 是 配置 通过 内容rol 位 作 也 一个 输入 或者 输出. 作 一个 输入, 它

能 是 测试 作 一个 情况.作 一个 输出, 它 能 是 使用至 信号 外部 peripherals.

TIMEXP O

计时器 expired.

asserted 为 四 核心 时钟 cycles 当 这 计时器 是 使能 和

tcount decrements 至 零.

HBR

i/一个

host 总线 要求.

必须 是 asserted 用 一个 host 处理器 至 要求 控制 的 这 adsp-

21161n’s 外部 总线. 当

HBR

是 asserted 在 一个 multiprocessing 系统, 这 adsp-

21161n 那 是 总线 主控 将 relinquish 这 总线 和 assert

HBG

. 至 relinquish 这 总线,

这 adsp-21161n places 这 地址, 数据, select, 和 strobe 线条 在 一个 高 阻抗

状态.

HBR

有 priority 在 所有 adsp-21161n 总线 requests (

BR6–1

) 在 一个 multiprocessing

系统.

表格 2. 管脚 函数 描述 (持续)

管脚 类型 函数