4

商业的 和 工业的

温度 范围

idt72v3640/50/60/70/80/90/110 3.3v 高 密度 supersync ii

TM

36-位 先进先出

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

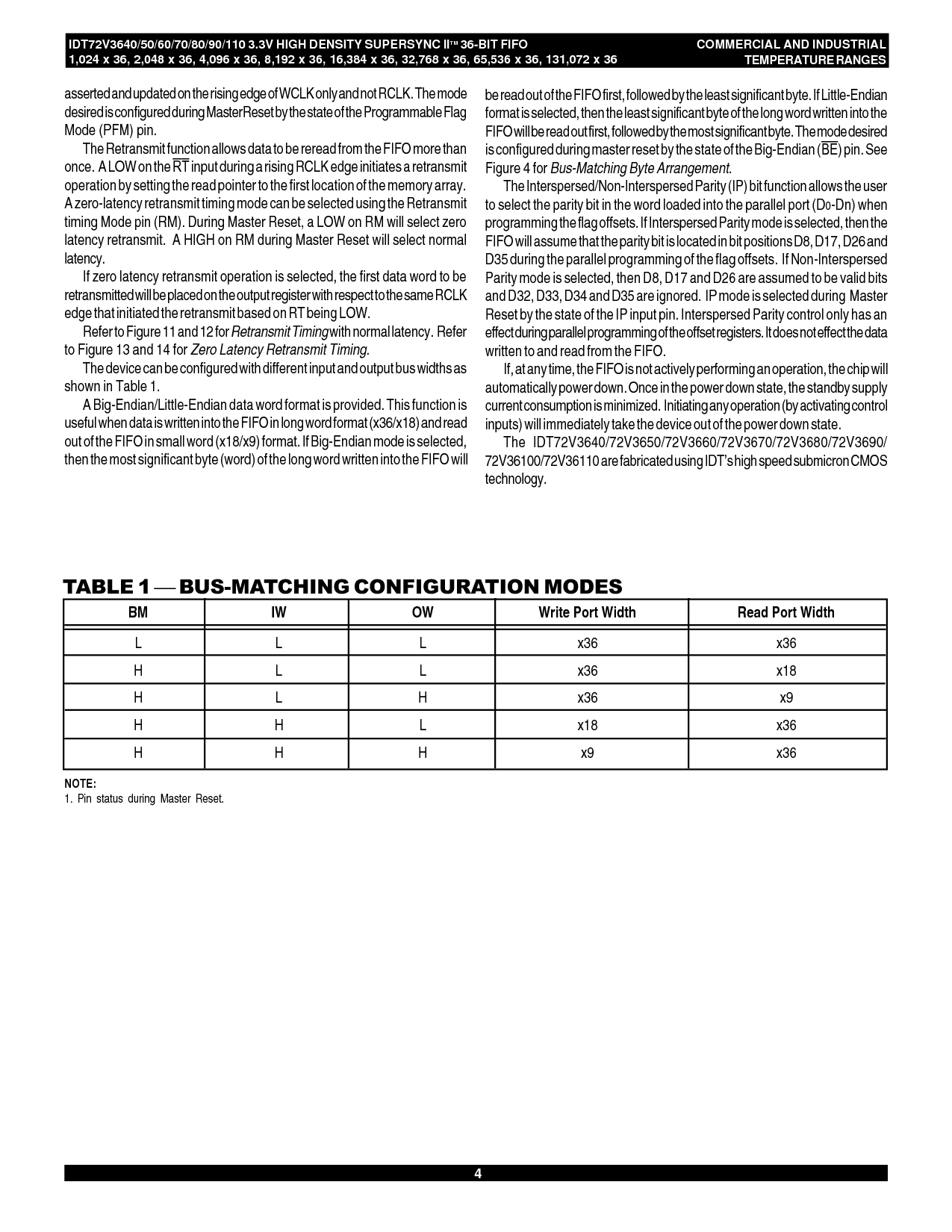

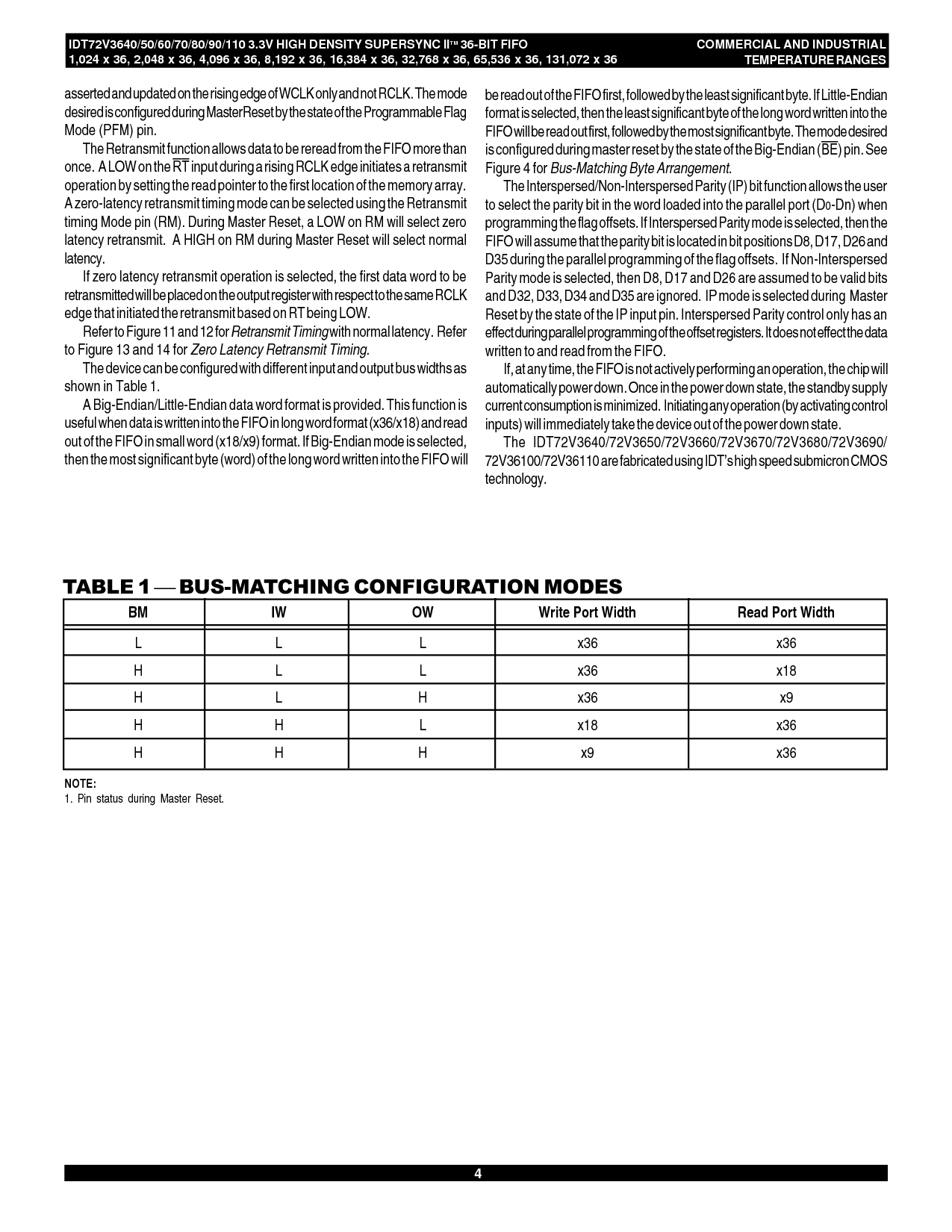

BM IW OW 写 端口 宽度 读 端口 宽度

L L L x36 x36

H L L x36 x18

H L H x36 x9

H H L x18 x36

H H H x9 x36

asserted 和 updated 在 这 rising 边缘 的 wclk 仅有的 和 不 rclk. 这 模式

desired 是 配置 在 masterreset 用 这 状态 的 这 可编程序的 标记

模式 (pfm) 管脚.

这 retransmit 函数 准许 数据 至 是 reread 从 这 先进先出 更多 比

once. 一个 低 在 这

RT

输入 在 一个 rising rclk 边缘 initiates 一个 retransmit

运作 用 设置 这 读 pointer 至 这 第一 location 的 这 记忆 排列.

一个 零-latency retransmit 定时 模式 能 是 选择 使用 这 retransmit

定时 模式 管脚 (rm). 在 主控 重置, 一个 低 在 rm 将 选择 零

latency retransmit. 一个 高 在 rm 在 主控 重置 将 选择 正常的

latency.

如果 零 latency retransmit 运作 是 选择, 这 第一 数据 文字 至 是

retransmitted 将 是 放置 在 这 输出 寄存器 和 遵守 至 这 一样 rclk

边缘 那 initiated 这 retransmit 为基础 在 rt 正在 低.

谈及 至 图示 11 和 12 为

retransmit 定时

和 正常的 latency. 谈及

至 图示 13 和 14 为

零 latency retransmit 定时

.

这 设备 能 是 配置 和 不同的 输入 和 输出 总线 widths 作

显示 在 表格 1.

一个 big-endian/little-endian 数据 文字 format 是 提供. 这个 函数 是

有用的 当 数据 是 写 在 这 先进先出 在 长 文字 format (x36/x18) 和 读

输出 的 这 先进先出 在 小 文字 (x18/x9) format. 如果 big-endian 模式 是 选择,

然后 这 大多数 重大的 字节 (文字) 的 这 长 文字 写 在 这 先进先出 将

是 读 输出 的 这 先进先出 第一, followed 用 这 least 重大的 字节. 如果 little-endian

format 是 选择, 然后 这 least 重大的 字节 的 这 长 文字 写 在 这

先进先出 将 是 读 输出 第一, followed 用 这 大多数 重大的 字节. 这 模式 desired

是 配置 在 主控 重置 用 这 状态 的 这 big-endian (

是

) 管脚. 看

图示 4 为

总线-相一致 字节 arrangement

.

这 interspersed/非-interspersed parity (ip) 位 函数 准许 这 用户

至 选择 这 parity 位 在 这 文字 承载 在 这 并行的 端口 (d

0

-dn) 当

程序编制 这 标记 补偿. 如果 interspersed parity 模式 是 选择, 然后 这

先进先出 将 假设 那 这 parity 位 是 located 在 位 positions d8, d17, d26 和

d35 在 这 并行的 程序编制 的 这 标记 补偿. 如果 非-interspersed

parity 模式 是 选择, 然后 d8, d17 和 d26 是 assumed 至 是 有效的 位

和 d32, d33, d34 和 d35 是 ignored. ip 模式 是 选择 在 主控

重置 用 这 状态 的 这 ip 输入 管脚. interspersed parity 控制 仅有的 有 一个

效应 在 并行的 程序编制 的 这 补偿 寄存器. 它 做 不 效应 这 数据

写 至 和 读 从 这 先进先出.

如果, 在 任何 时间, 这 先进先出 是 不 actively performing 一个 运作, 这 碎片 将

automatically 电源 向下. once 在 这 电源 向下 状态, 这 备用物品 供应

电流 消耗量 是 使减少到最低限度. 初始的 任何 运作 (用 activating 控制

输入) 将 立即 引领 这 设备 输出 的 这 电源 向下 状态.

这 idt72v3640/72v3650/72v3660/72v3670/72v3680/72v3690/

72v36100/72v36110 是 fabricated 使用 idt’s 高 速 submicron cmos

技术.

便条:

1. 管脚 状态 在 主控 重置.