8

fn9134.1

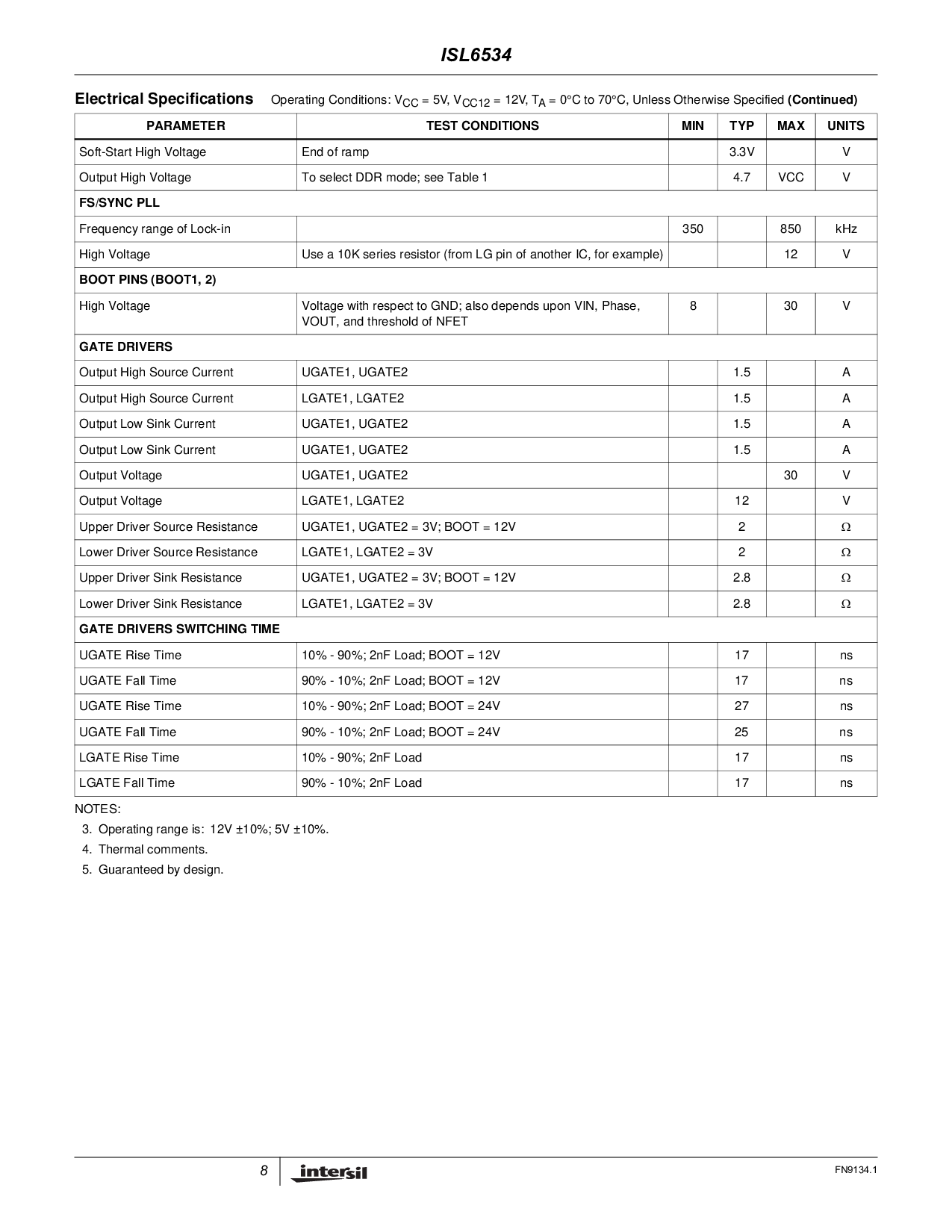

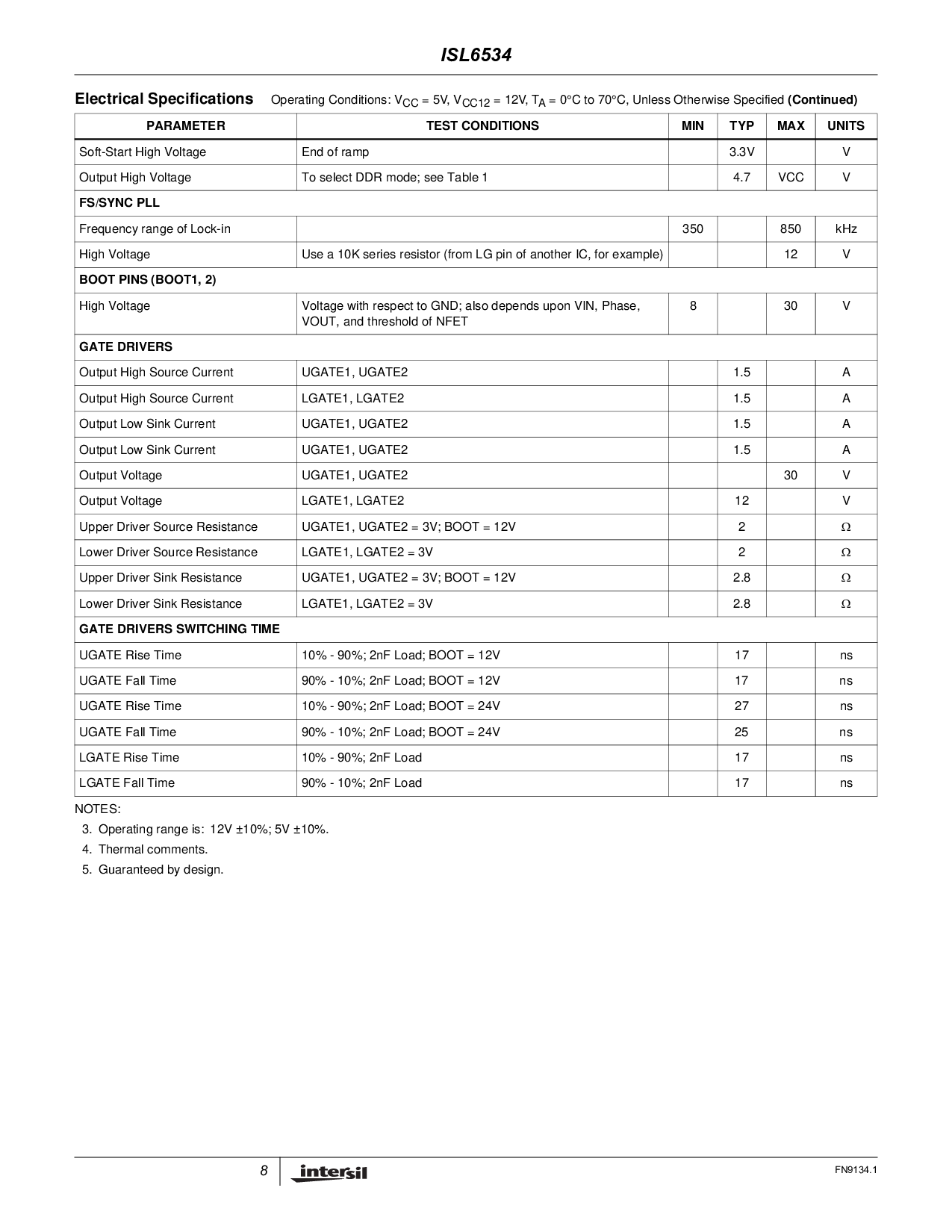

软-开始 高 电压 终止 的 ramp 3.3v V

输出 高 电压 至 选择 ddr 模式; 看 表格 1 4.7 VCC V

fs/同步 pll

频率 范围 的 锁-在 350 850 kHz

高 电压 使用 一个 10k 序列 电阻 (从 lg 管脚 的 另一 ic, 为 例子) 12 V

激励 管脚 (boot1, 2)

高 电压 电压 和 遵守 至 地; 也 取决于 在之上 vin, 阶段,

vout, 和 门槛 的 nfet

830V

门 驱动器

输出 高 源 电流 ugate1, ugate2 1.5 一个

输出 高 源 电流 lgate1, lgate2 1.5 一个

输出 低 下沉 电流 ugate1, ugate2 1.5 一个

输出 低 下沉 电流 ugate1, ugate2 1.5 一个

输出 电压 ugate1, ugate2 30 V

输出 电压 lgate1, lgate2 12 V

upper 驱动器 源阻抗 ugate1, ugate2 = 3v; 激励 = 12v 2

Ω

更小的 驱动器 源 resistance lgate1, lgate2 = 3v 2

Ω

upper 驱动器 下沉 阻抗 UGATE1, ugate2 = 3v; 激励 = 12v 2.8

Ω

更小的 驱动器 下沉 阻抗 lgate1, lgate2 = 3v 2.8

Ω

门 驱动器 切换 时间

ugate 上升 时间 10% - 90%; 2nf 加载; 激励 = 12v 17 ns

ugate 下降 时间 90% - 10%; 2nf 加载; 激励 = 12v 17 ns

ugate 上升 时间 10% - 90%; 2nf 加载; 激励 = 24v 27 ns

ugate 下降 时间 90% - 10%; 2nf 加载; 激励 = 24v 25 ns

lgate 上升 时间 10% - 90%; 2nf 加载 17 ns

lgate 下降 时间 90% - 10%; 2nf 加载 17 ns

注释:

3. 运行 范围 是: 12v ±10%; 5v ±10%.

4. 热的 comments.

5. 有保证的 用 设计.

电的 规格

运行 情况: v

CC

= 5v, v

CC12

= 12v, t

一个

= 0°c 至 70°c, 除非 否则 指定

(持续)

参数 测试 情况 最小值 典型值 最大值 单位

ISL6534