AD9835

–3–rev. 0

定时 特性

(v

DD

= +5 v

5%; agnd = dgnd = 0 v, 除非 否则 指出)

限制 在

T

最小值

至 t

最大值

参数 (b 版本) 单位 测试 情况/comments

t

1

20 ns 最小值 mclk 时期

t

2

8 ns 最小值 mclk 高 持续时间

t

3

8 ns 最小值 mclk 低 持续时间

t

4

50 ns 最小值 sclk 时期

t

5

20 ns 最小值 sclk 高 持续时间

t

6

20 ns 最小值 sclk 低 持续时间

t

7

15 ns 最小值 fsync 至 sclk 下落 边缘 建制 时间

t

8

20 ns 最小值 fsync 至 sclk 支撑 时间

sclk – 5 ns 最大值

t

9

15 ns 最小值 数据 建制 时间

t

10

5 ns 最小值 数据 支撑 时间

t

11

8 ns 最小值 fselect, psel0, psel1 建制 时间 在之前 mclk rising 边缘

t

11A

1

8 ns 最小值 fselect, psel0, psel1 建制 时间 之后 mclk rising 边缘

注释

1

看 管脚 描述 部分.

有保证的 用 设计 但是 不 生产 测试.

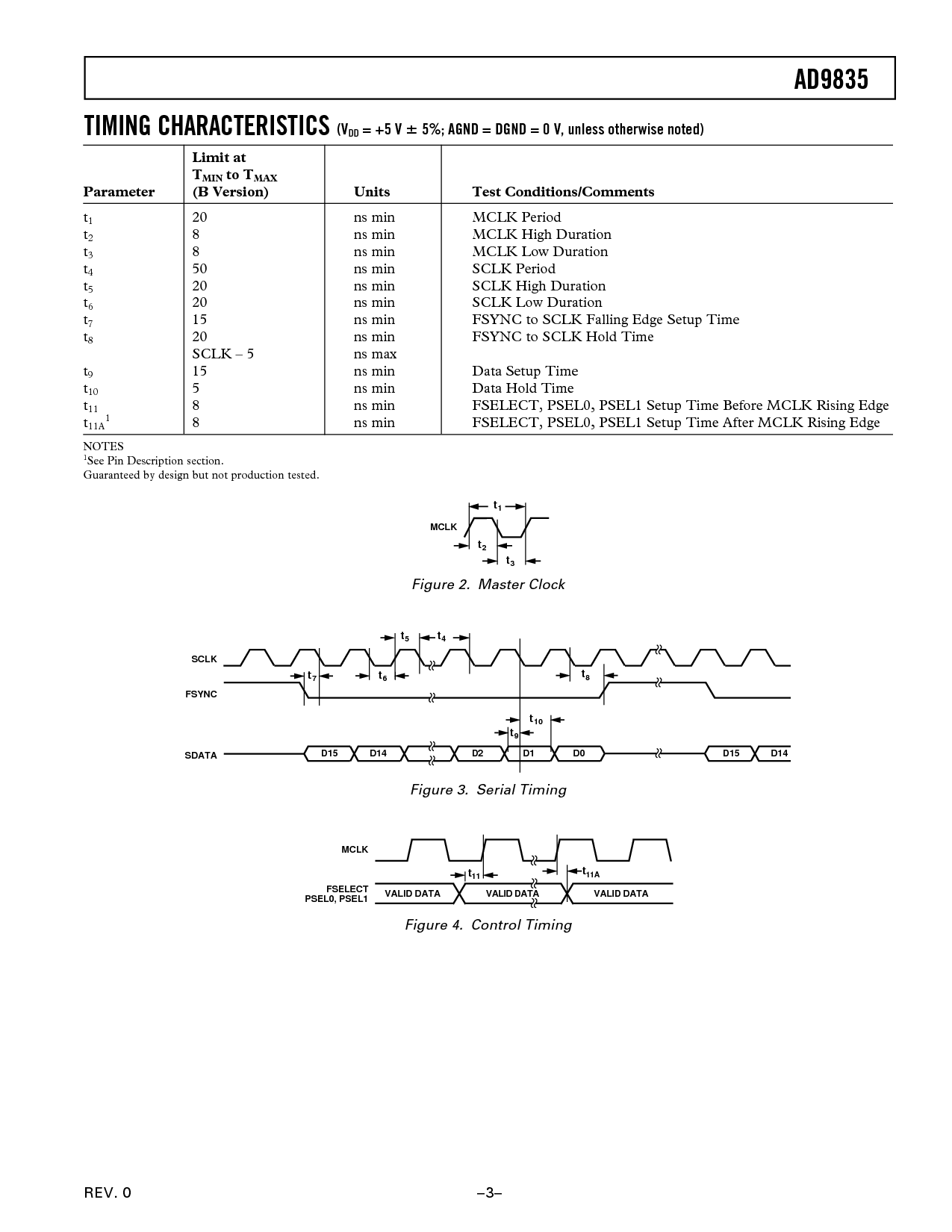

MCLK

t

2

t

1

t

3

图示 2. 主控 时钟

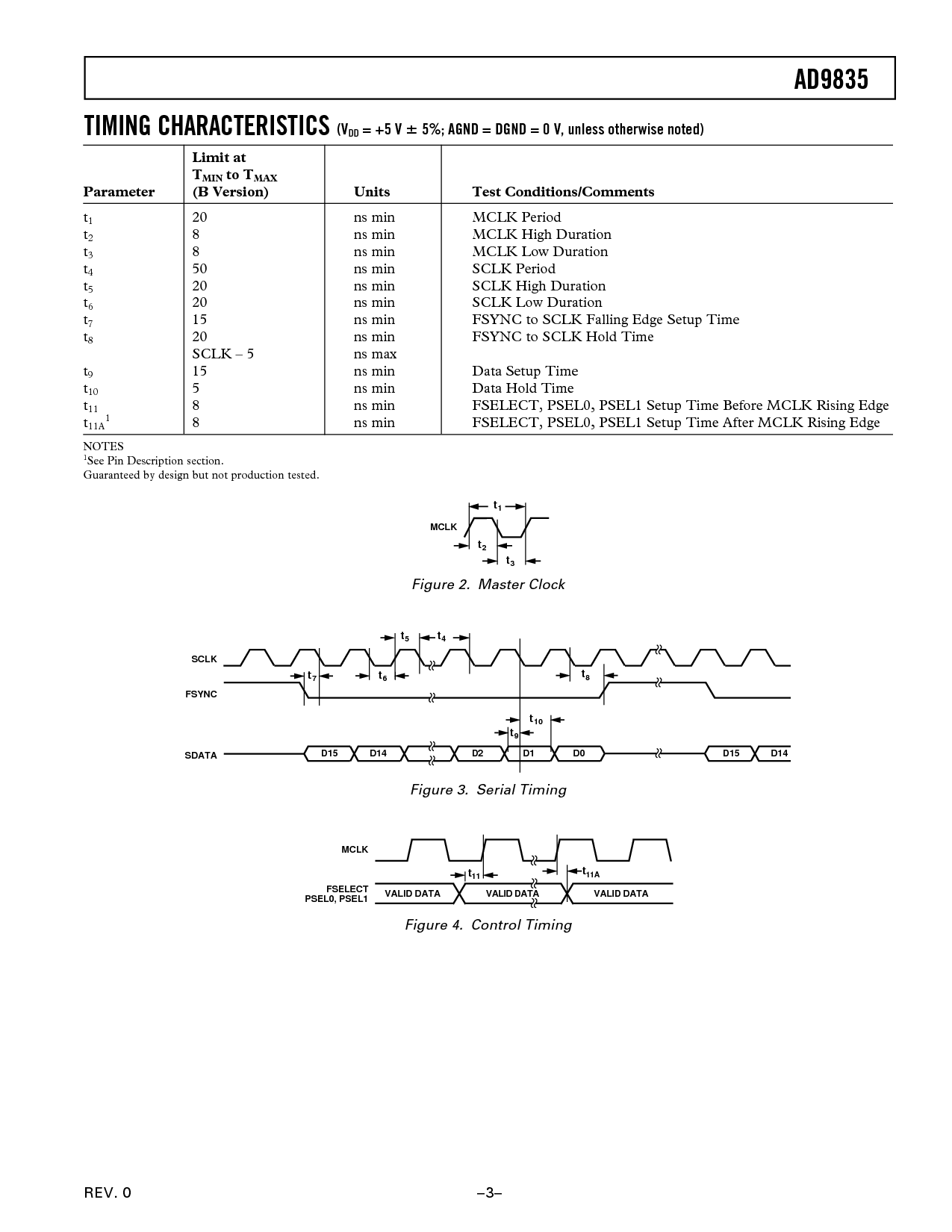

SCLK

FSYNC

SDATA

t

5

t

4

t

6

t

7

t

8

t

10

t

9

D15 D14 D2 D1 D0 D15 D14

图示 3. 串行 定时

t

11A

t

11

有效的 数据 有效的 数据 有效的 数据

MCLK

FSELECT

psel0, psel1

图示 4. 控制 定时