6

规格

ispgdx160v/va

这 ispgdxv/va 家族 architecture 有 被 devel-

oped 至 deliver 一个 在-系统 可编程序的 信号 routing

解决方案 和 高 速 和 高 flexibility. 这 设备

是 targeted 为 三 类似的 但是 distinct classes 的 终止-

系统 产品:

可编程序的, 随机的 信号

interconnect (prsi)

这个 类 包含 pcb-水平的 可编程序的 信号 rout-

ing 和 将 是 使用 至 提供 arbitrary 信号 swapping

在 碎片. 它 opens 向上 这 possibilities 的 程序-

mable 系统 硬件. 它 是 典型 用 这 需要

至 提供 一个 大 号码 的 1:1 管脚 连接 这个

是 statically 配置, i.e., 这 管脚-至-管脚 paths 做 不

需要 至 改变 dynamically 在 回馈 至 控制 在-

puts.

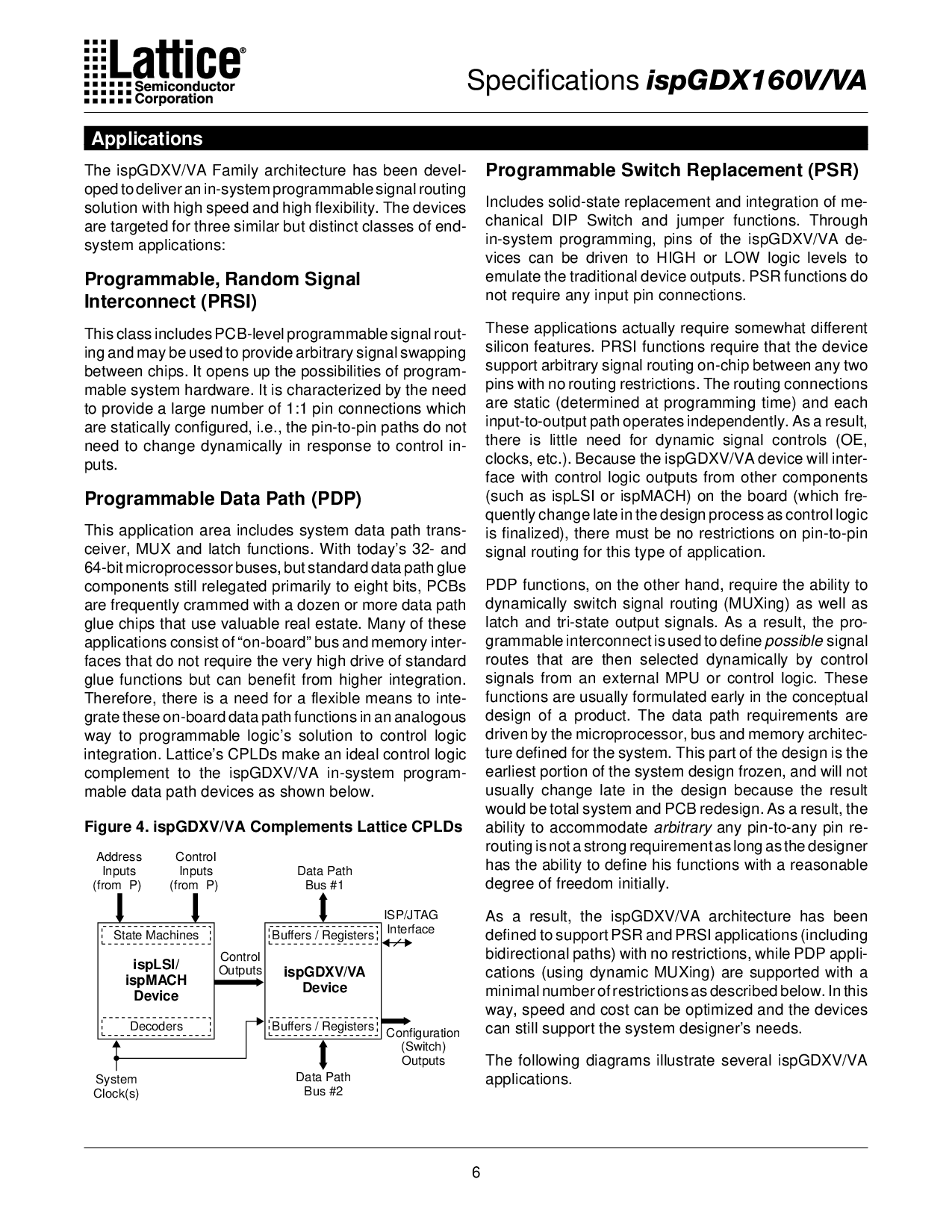

可编程序的 数据 path (pdp)

这个 应用 范围 包含 系统 数据 path trans-

ceiver, mux 和 获得 功能. 和 today

’

s 32- 和

64-位 微处理器 buses, 但是 标准 数据 path glue

组件 安静的 relegated primarily 至 第八 位, pcbs

是 frequently crammed 和 一个 dozen 或者 更多 数据 path

glue 碎片 那 使用 valuable real estate. 许多 的 这些

产品 组成 的

“

在-板

”

总线 和 记忆 inter-

faces 那 做 不 需要 这 非常 高 驱动 的 标准

glue 功能 但是 能 益处 从 高等级的 integration.

因此, 那里 是 一个 需要 为 一个 有伸缩性的 意思 至 inte-

grate 这些 在-板 数据 path 功能 在 一个 analogous

方法 至 可编程序的 逻辑

’

s 解决方案 至 控制 逻辑

integration. lattice

’

s cplds 制造 一个 完美的 控制 逻辑

complement 至 这 ispgdxv/va 在-系统 程序-

mable 数据 path 设备 作 显示 在下.

数据 path

总线 #1

控制

输入

(从 p)

地址

输入

(从 p)

控制

输出

系统

时钟(s)

数据 path

总线 #2

配置

(转变)

输出

isp/jtag

接口

isplsi/

ispMACH

设备

ispgdxv/va

设备

缓存区 / registersdecoders

缓存区 / registersstate machines

图示 4. ispgdxv/va complements lattice cplds

产品

可编程序的 转变 替换 (psr)

包含 固体的-状态 替换 和 integration 的 me-

chanical 插件 转变 和 跳越者 功能. 通过

在-系统 程序编制, 管脚 的 这 ispgdxv/va de-

vices 能 是 驱动 至 高 或者 低 逻辑 水平 至

emulate 这 传统的 设备 输出. psr 功能 做

不 需要 任何 输入 管脚 连接.

这些 产品 的确 需要 somewhat 不同的

硅 特性. prsi 功能 需要 那 这 设备

支持 arbitrary 信号 routing 在-碎片 在 任何 二

管脚 和 非 routing restrictions. 这 routing 连接

是 静态的 (决定 在 程序编制 时间) 和 各自

输入-至-输出 path 运作 independently. 作 一个 结果,

那里 是 little 需要 为 动态 信号 控制 (oe,

clocks, 等.). 因为 这 ispgdxv/va 设备 将 inter-

面向 和 控制 逻辑 输出 从 其它 组件

(此类 作 isplsi 或者 ispmach) 在 这 板 (这个 fre-

quently 改变 late 在 这 设计 处理 作 控制 逻辑

是 finalized), 那里 必须 是 非 restrictions 在 管脚-至-管脚

信号 routing 为 这个 类型 的 应用.

pdp 功能, 在 这 其它 hand, 需要 这 能力 至

dynamically 转变 信号 routing (muxing) 作 好 作

获得 和 触发-状态 输出 信号. 作 一个 结果, 这 pro-

grammable interconnect 是 使用 至 定义

可能

信号

routes 那 是 然后 选择 dynamically 用 控制

信号 从 一个 外部 mpu 或者 控制 逻辑. 这些

功能 是 通常地 formulated early 在 这 conceptual

设计 的 一个 产品. 这 数据 path (所需的)东西 是

驱动 用 这 微处理器, 总线 和 记忆 architec-

ture 定义 为 这 系统. 这个 部分 的 这 设计 是 这

earliest portion 的 这 系统 设计 frozen, 和 将 不

通常地 改变 late 在 这 设计 因为 这 结果

将 是 总的 系统 和 pcb redesign. 作 一个 结果, 这

能力 至 accommodate

arbitrary

任何 管脚-至-任何 管脚 re-

routing 是 不 一个 强 必要条件 作 长 作 这 设计者

有 这 能力 至 定义 his 功能 和 一个 合理的

程度 的 自由 initially.

作 一个 结果, 这 ispgdxv/va architecture 有 被

定义 至 支持 psr 和 prsi 产品 (包含

双向的 paths) 和 非 restrictions, 当 pdp appli-

cations (使用 动态 muxing) 是 supported 和 一个

minimal 号码 的 restrictions 作 描述 在下. 在 这个

方法, 速 和 费用 能 是 优化 和 这 设备

能 安静的 支持 这 系统 设计者

’

s needs.

这 下列的 图解 illustrate 一些 ispgdxv/va

产品.