R

将 14, 1999 (版本 1.6) 6-11

xc4000e 和 xc4000x 序列 地方 可编程序的 门 arrays

6

设置/重置

一个 异步的 存储 元素 输入 (sr) 能 是 con-

figured 作 也 设置 或者 重置. 这个 configuration 选项

确定 这 状态 在 这个 各自 flip-flop 变为 oper-

ational 之后 configuration. 它 也 确定 这 效应 的 一个

Global 设置/重置 脉冲波 在 正常的 运作, 和 这

效应 的 一个 脉冲波 在 这 SR 管脚 的 这 clb. 所有 三

设置/重置 功能 为 任何 单独的 flip-flop 是 控制 用

这 一样 configuration 数据 位.

这 设置/重置 状态 能 是 independently specified 为 各自

flip-flop. 这个 输入 能 也 是 independently 无能 为

也 flip-flop.

这 设置/重置 状态 是 specified 用 使用 这 INIT attribute,

或者 用 放置 这 适合的 设置 或者 重置 flip-flop 库

标识.

sr 是 起作用的 高. 它 是 不 invertible 在里面 这 clb.

global 设置/重置

一个 独立的 Global 设置/重置 线条 (不 显示 在 图示 1)

sets 或者 clears 各自 存储 元素 在 电源-向上,

re-configuration, 或者 当 一个 专心致志的 重置 网 是 驱动

起作用的. 这个 global 网 (gsr) 做 不 compete 和 其它

routing resources; 它 使用 一个 专心致志的 分发 网络.

各自 flip-flop 是 configured 作 也 globally 设置 或者 重置 在

这 一样 方法 那 这 local 设置/重置 (sr) 是 specified.

因此, 如果 一个 flip-flop 是 设置 用 sr, 它 是 也 设置 用 gsr.

similarly, 一个 重置 flip-flop 是 重置 用 两个都 sr 和 gsr.

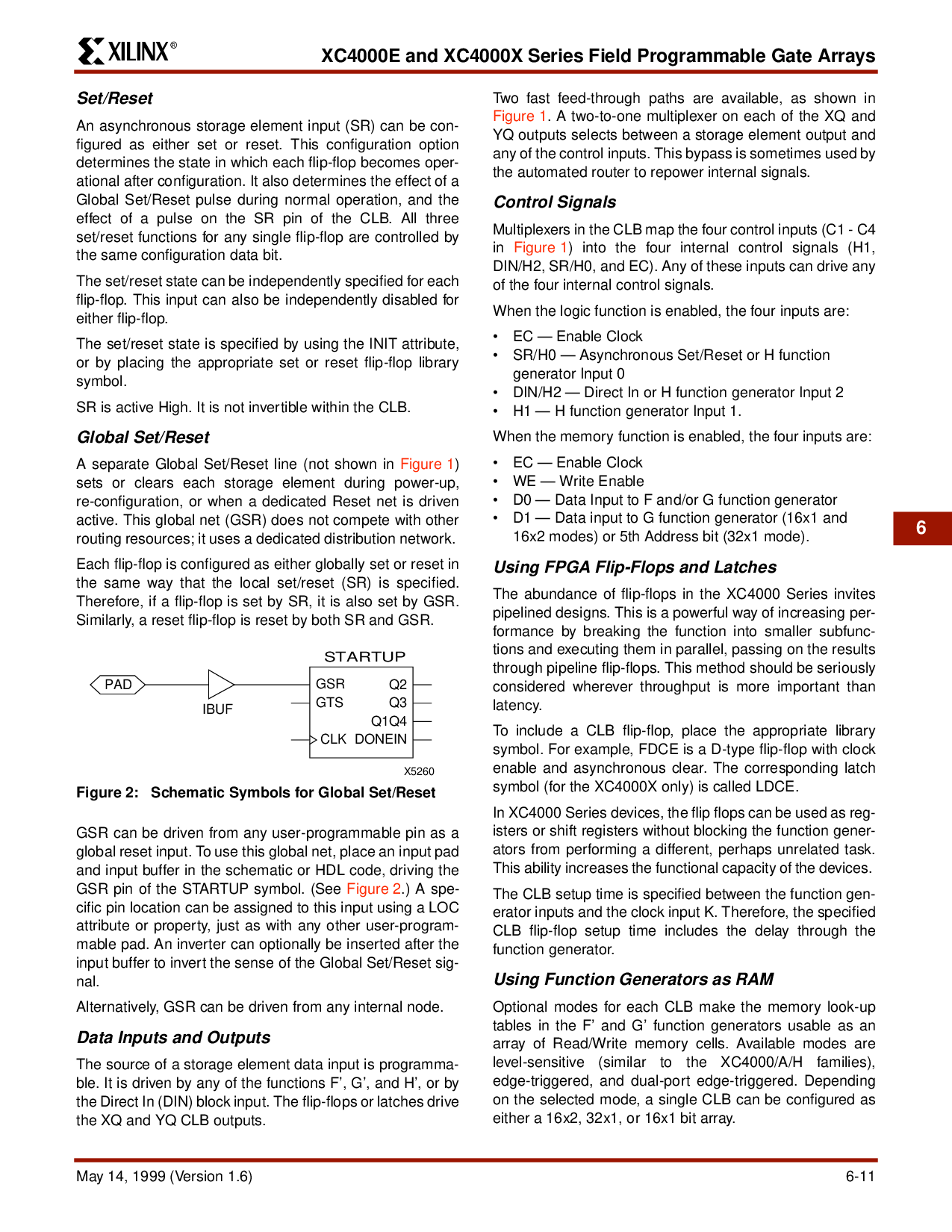

GSR 能 是 驱动 从 任何 用户-可编程序的 管脚 作 一个

global 重置 输入. 至 使用 这个 global 网, 放置 一个 输入 垫子

和 输入 缓存区 在 这 图式 或者 HDL 代号, 驱动 这

GSR 管脚 的 这 STARTUP 标识. (看 图示 2.) 一个 spe-

cific 管脚 location 能 是 assigned 至 这个 输入 使用 一个 LOC

attribute 或者 所有物, just 作 和 任何 其它 用户-程序-

mable 垫子. 一个 反相器 能 optionally 是 inserted 之后 这

输入 缓存区 至 invert 这 sense 的 这 Global 设置/重置 sig-

nal.

alternatively, gsr 能 是 驱动 从 任何 内部的 node.

数据 输入 和 输出

这 源 的 一个 存储 元素 数据 输入 是 programma-

ble. 它 是 驱动 用 任何 的 这 功能 f’, g’, 和 h’, 或者 用

这 直接 在 (din) 块 输入. 这 flip-flops 或者 latches 驱动

这 xq 和 yq clb 输出.

二 快 喂养-通过 paths 是 有, 作 显示 在

图示 1. 一个 二-至-一个 多路调制器 在 各自 的 这 XQ 和

YQ 输出 选择 在 一个 存储 元素 输出 和

任何 的 这 控制 输入. 这个 绕过 是 sometimes 使用 用

这 automated router 至 repower 内部的 信号.

控制 信号

Multiplexers 在 这 CLB 编排 这 四 控制 输入 (c1 - C4

在 图示 1) 在 这 四 内部的 控制 信号 (h1,

din/h2, sr/h0, 和 ec). 任何 的 这些 输入 能 驱动 任何

的 这 四 内部的 控制 信号.

当 这 逻辑 函数 是 使能, 这 四 输入 是:

• ec — 使能 时钟

• sr/h0 — 异步的 设置/重置 或者 h 函数

发生器 输入 0

• din/h2 — 直接 在 或者 h 函数 发生器 输入 2

• h1 — h 函数 发生器 输入 1.

当 这 记忆 函数 是 使能, 这 四 输入 是:

• ec — 使能 时钟

• 我们 — 写 使能

• d0 — 数据 输入 至 f 和/或者 g 函数 发生器

• d1 — 数据 输入 至 g 函数 发生器 (16x1 和

16x2 模式) 或者 5th 地址 位 (32x1 模式).

使用 fpga flip-flops 和 latches

这 abundance 的 flip-flops 在 这 XC4000 序列 invites

pipelined 设计. 这个 是 一个 powerful 方法 的 增加 每-

formance 用 breaking 这 函数 在 小 subfunc-

tions 和 executing 它们 在 并行的, passing 在 这 结果

通过 pipeline flip-flops. 这个 方法 应当 是 seriously

考虑 wherever throughput 是 更多 重要的 比

latency.

至 包含 一个 CLB flip-flop, 放置 这 适合的 库

标识. 为 例子, FDCE 是 一个 d-类型 flip-flop 和 时钟

使能 和 异步的 clear. 这 相应的 获得

标识 (为 这 xc4000x 仅有的) 是 called ldce.

在 XC4000 序列 设备, 这 flip flops 能 是 使用 作 reg-

isters 或者 变换 寄存器 没有 blocking 这 函数 gener-

ators 从 performing 一个 不同的, perhaps unrelated task.

这个 能力 增加 这 函数的 capacity 的 这 设备.

这 CLB 建制 时间 是 specified 在 这 函数 gen-

erator 输入 和 这 时钟 输入 k. 因此, 这 specified

CLB flip-flop 建制 时间 包含 这 延迟 通过 这

函数 发生器.

使用 函数 发生器 作 内存

Optional 模式 为 各自 CLB 制造 这 记忆 看-向上

tables 在 这 F’ 和 G’ 函数 发生器 usable 作 一个

排列 的 读/写 记忆 cells. 有 模式 是

水平的-敏感的 (类似的 至 这 xc4000/一个/h families),

边缘-triggered, 和 双-端口 边缘-triggered. 取决于

在 这 选择 模式, 一个 单独的 CLB 能 是 configured 作

也 一个 16x2, 32x1, 或者 16x1 位 排列.

垫子

IBUF

GSR

GTS

CLK

DONEIN

Q1Q4

Q2

Q3

STARTUP

X5260

图示 2: 图式 symbols 为 global 设置/重置