2XDRIVE 输出 驱动

0 12 毫安

1 25 毫安

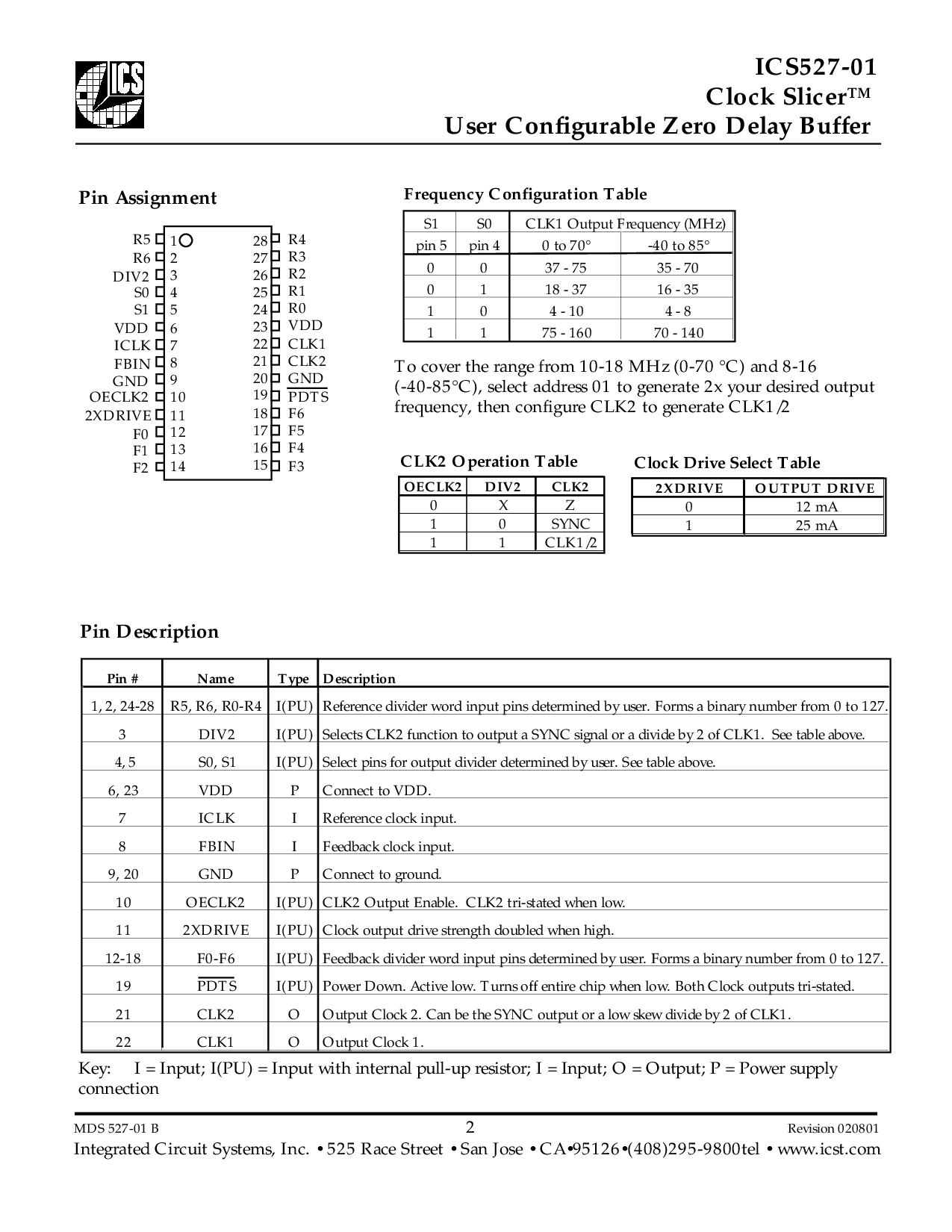

管脚 # 名字 类型 描述

1, 2, 24-28 r5, r6, r0-r4 i(pu) 涉及 分隔物 文字 输入 管脚 决定 用 用户. 形式 一个 二进制的 号码 从 0 至 127.

3 DIV2 i(pu) 选择 clk2 函数 至 输出 一个 同步 信号 或者 一个 分隔 用 2 的 clk1. 看 表格 在之上.

4, 5 s0, s1 i(pu) 选择 管脚 为 输出 分隔物 决定 用 用户. 看 表格 在之上.

6, 23 VDD P 连接 至 vdd.

7 ICLK I 涉及 时钟 输入.

8 FBIN I 反馈 时钟 输入.

9, 20 地 P 连接 至 地面.

10 OECLK2 i(pu) clk2 输出 使能. clk2 触发-陈述 当 低.

11 2XDRIVE i(pu) 时钟 输出 驱动 力量 doubled 当 高.

12-18 f0-f6 i(pu) 反馈 分隔物 文字 输入 管脚 决定 用 用户. 形式 一个 二进制的 号码 从 0 至 127.

19 PDTS i(pu) 电源 向下. 起作用的 低. 转变 止 全部 碎片 当 低. 两个都 时钟 输出 触发-陈述.

21 CLK2 O 输出 时钟 2. 能 是 这 同步 输出 或者 一个 低 skew 分隔 用 2 的 clk1.

22 CLK1 O 输出 时钟 1.

ics527-01

时钟 slicer™

用户 configurable 零 延迟 缓存区

mds 527-01 b 2 修订 020801

整体的 电路 系统, 公司 • 525 race 街道 • san jose • ca•95126•(408)295-9800tel • www.icst.com

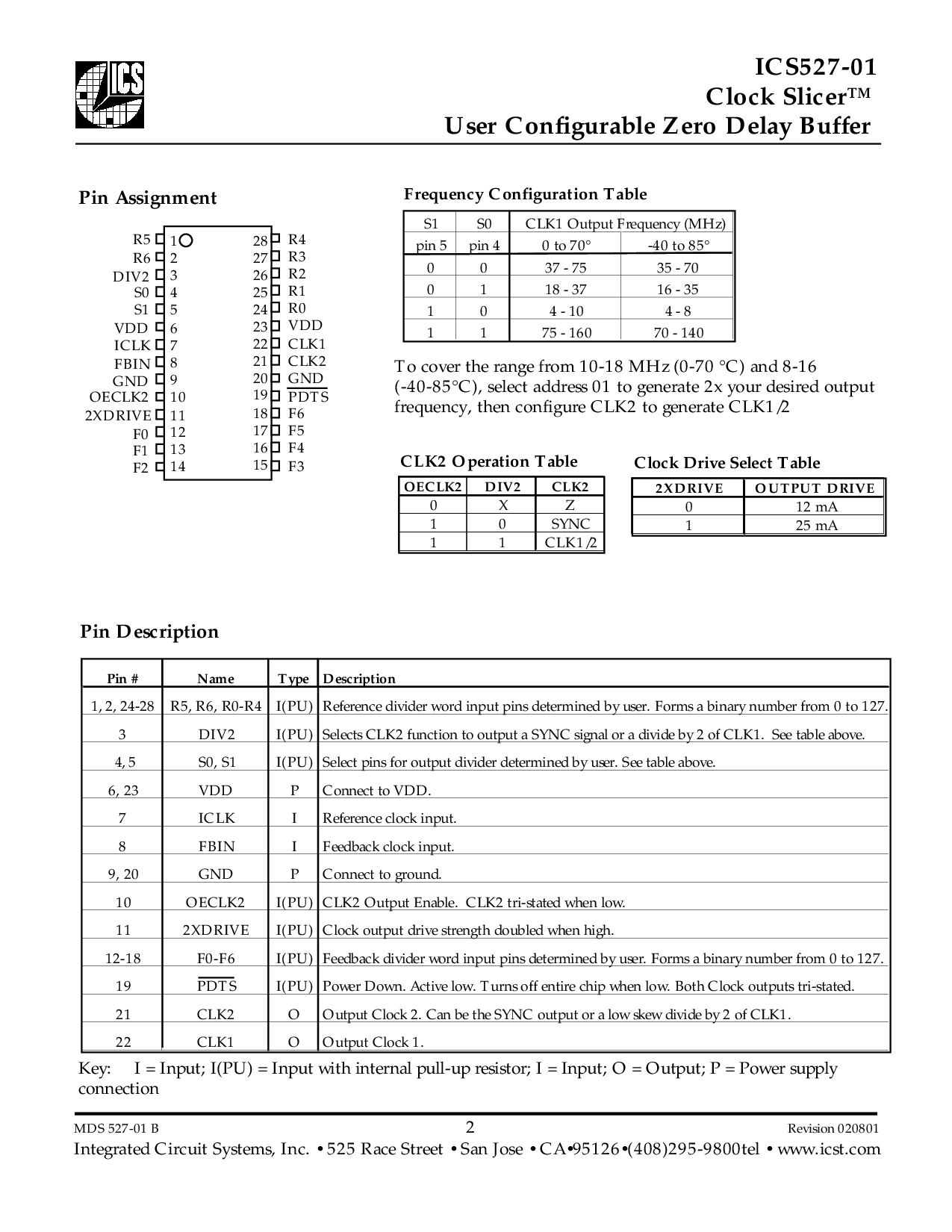

管脚 分派

关键: i = 输入; i(pu) = 输入 和 内部的 拉-向上 电阻; i = input; o = output; p = 电源 供应

连接

1

8

9

2

3

4

5

6

7

10

11

12

13

14

16

15

20

17

18

19

25

24

23

22

21

26

27

28

F0

FBIN

VDD

ICLK

地

F2

VDD

CLK1

地

R2

R4

F6

CLK2

R3

R1

F4

F3

PDTS

R0

R5

R6

OECLK2

F1

2XDRIVE

S1

DIV2

S0

F5

S1 S0 clk1 输出 频率 (mhz) clk1 输出 频率 (mhz)

管脚 5 管脚 4 0 至 70° -40 至 85°

0 0 37 - 75 35 - 70

0 1 18 - 37 16 - 35

1 0 4 - 10 4 - 8

1 1 75 - 160 70 - 140

频率 配置 表格

管脚 描述

OECLK2 DIV2 CLK2

0 X Z

1 0 同步

1 1 clk1/2

clk2 运作 表格

时钟 驱动 选择 表格

至 覆盖 这 范围 从 10-18 mhz (0-70 °c) 和 8-16

(-40-85°c), 选择 地址 01 至 发生 2x your desired 输出

频率, 然后 配置 clk2 至 发生 clk1/2