ics527-01

时钟 slicer™

用户 configurable 零 延迟 缓存区

mds 527-01 b 6 修订 020801

整体的 电路 系统, 公司 • 525 race 街道 • san jose • ca•95126•(408)295-9800tel • www.icst.com

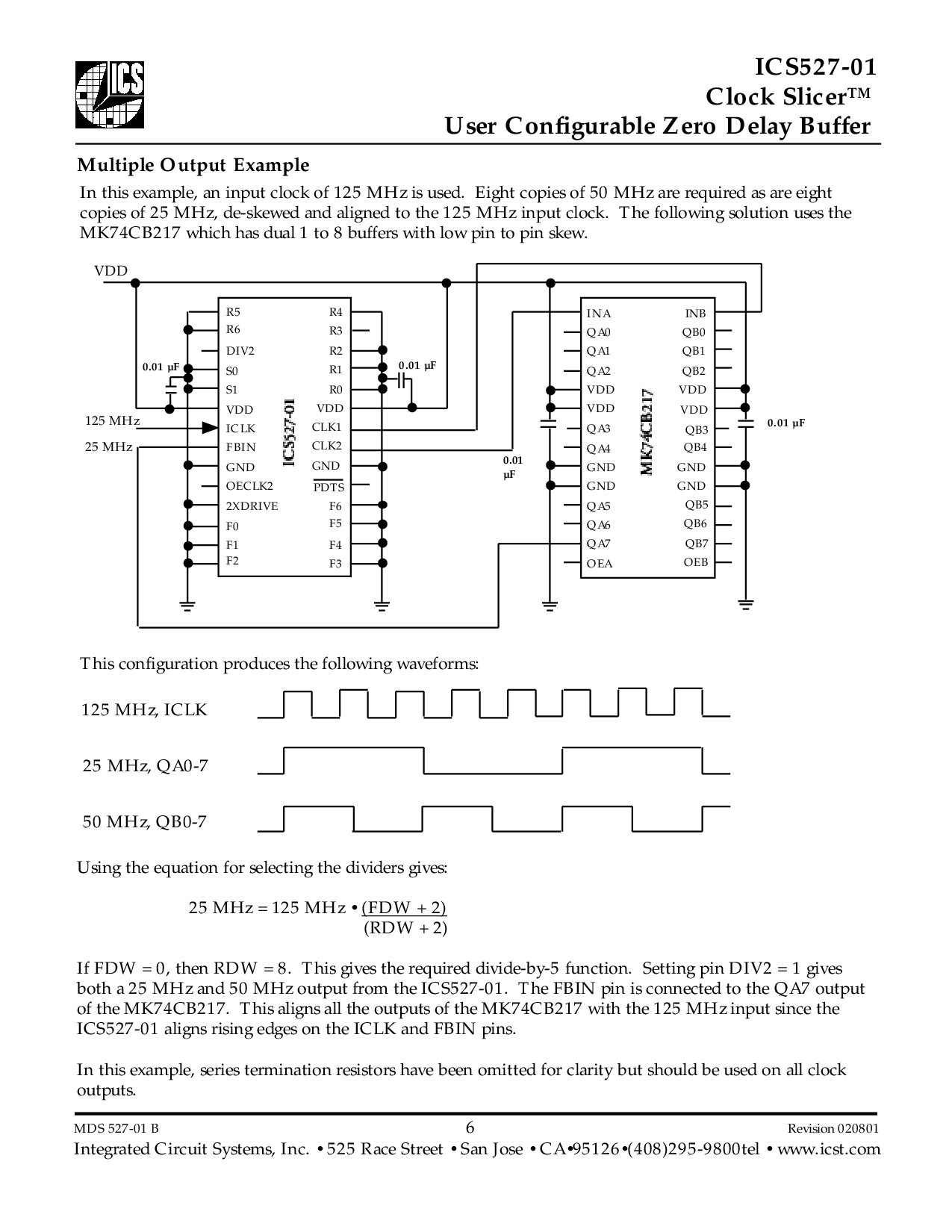

多样的 输出 例子

在 这个 例子, 一个 输入 时钟 的 125 mhz 是 使用. 第八 copies 的 50 mhz 是 必需的 作 是 第八

copies 的 25 mhz, de-skewed 和 排整齐 至 这 125 mhz 输入 时钟. 这 下列的 解决方案 使用 这

mk74cb217 这个 有 双 1 至 8 缓存区 和 低 管脚 至 管脚 skew.

125 mhz

0.01 µf

0.01 µf

25 mhz

R5

R6

DIV2

S0

S1

VDD

ICLK

FBIN

地

地

R4

R3

R2

R1

R0

VDD

CLK1

CLK2

OECLK2

2XDRIVE

F0

F1

F2

F6

F5

F4

F3

PDTS

INA

QA0

QA1

QA2

VDD

VDD

QA3

QA4

地 地

INB

VDD

QB3

QA5

QA6

地

QA7

OEA

QB5

QB6

QB7

OEB

QB0

QB1

QB2

VDD

QB4

地

0.01 µf

0.01

µF

VDD

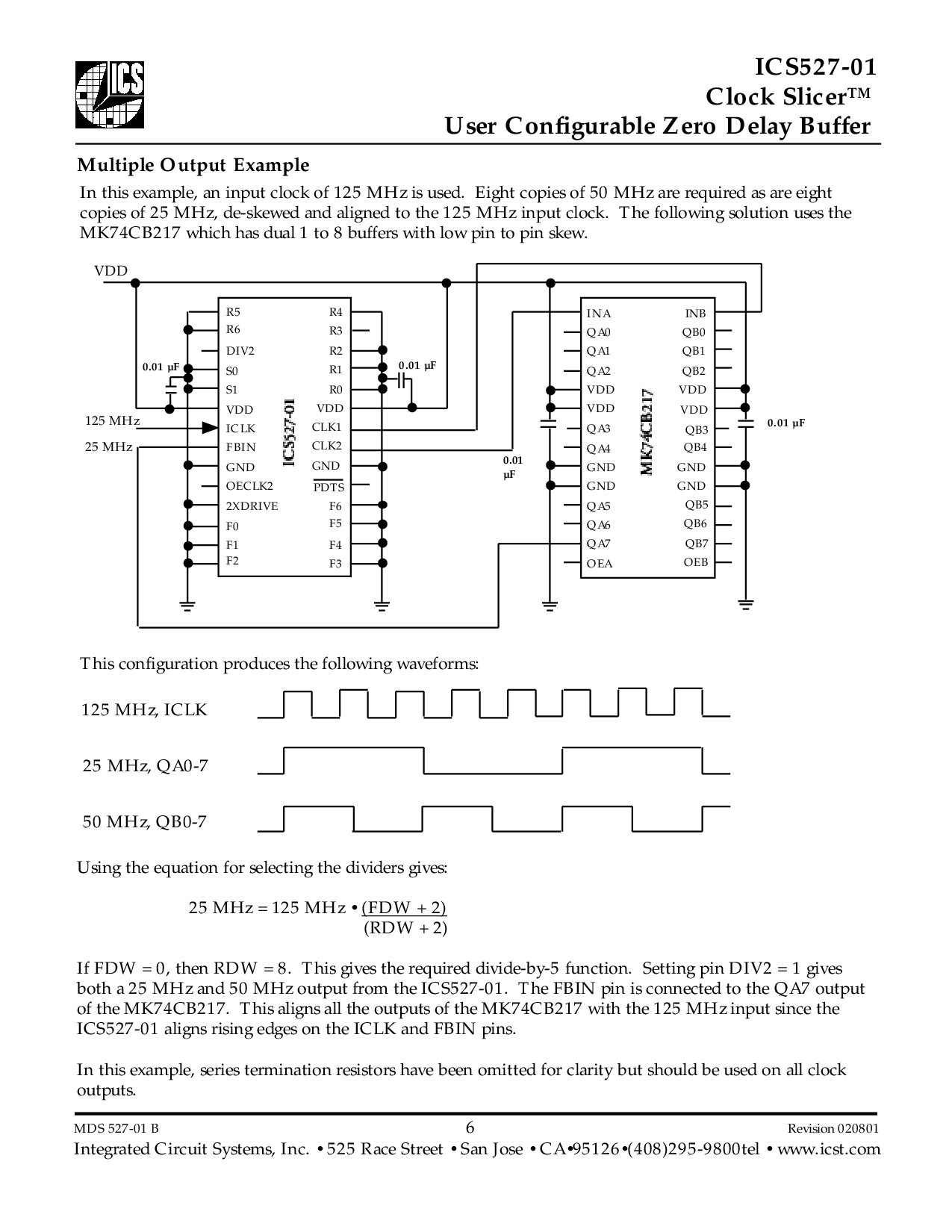

这个 配置 生产 这 下列的 波形:

125 mhz, iclk

25 mhz, qa0-7

50 mhz, qb0-7

使用 这 等式 为 selecting 这 dividers 给:

25 mhz = 125 mhz •(fdw + 2)

(rdw + 2)

如果 fdw = 0, 然后 rdw = 8. 这个 给 这 必需的 分隔-用-5 函数. 设置 管脚 div2 = 1 给

两个都 一个 25 mhz 和 50 mhz 输出 从 这 ics527-01. 这 fbin 管脚 是 连接 至 这 qa7 输出

的 这 mk74cb217. 这个 aligns 所有 这 输出 的 这 mk74cb217 和 这 125 mhz 输入 自从 这

ics527-01 aligns rising edges 在 这 iclk 和 fbin 管脚.

在 这个 例子, 序列 末端 电阻器 有 被 omitted 为 clarity 但是 应当 是 使用 在 所有 时钟

输出.