5-8

位 0, 这个 corresponds 至 d0 在 这 数据 总线, 是 总是 这

first 串行 数据 位 transmitted. provision 是 制造 为 这

传输者 parity 至 是 这 一样 或者 不同的 从 这

接受者. 这 tbre 输出 管脚 和 flag (usr 寄存器) reflect

这 状态 的 这 tbr. 这 tc flag (usr 寄存器) indicates

当 两个都 tbr 和 tr 是 empty.

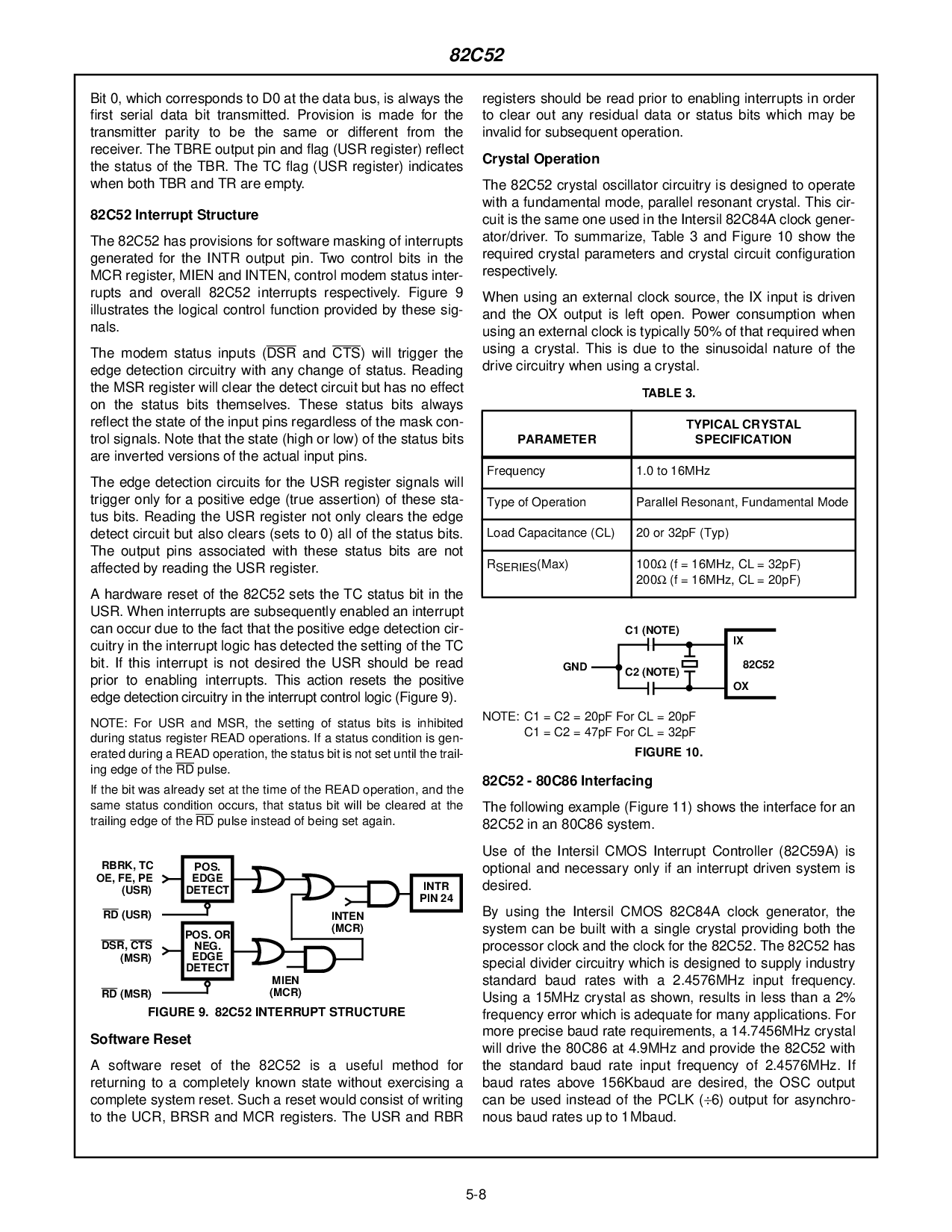

82c52 中断 结构

这 82c52 有 provisions 为 软件 masking 的 中断

发生 为 这 intr 输出 管脚. 二 控制 位 在 这

mcr 寄存器, mien 和 inten, 控制 modem 状态 inter-

rupts 和 整体的 82c52 中断 各自. 图示 9

illustrates 这 logical 控制 函数 提供 用 这些 sig-

nals.

这 modem 状态 输入 (

dsr 和 cts) 将 触发 这

边缘 发现 电路系统 和 任何 改变 的 状态. 读

这 msr 寄存器 将 clear 这 发现 电路 但是 有 非 效应

在 这 状态 位 themselves. 这些 状态 位 总是

reflect 这 状态 的 这 输入 管脚 regardless 的 这 掩饰 con-

trol 信号. 便条 那 这 状态 (高 或者 低) 的 这 状态 位

是 inverted 版本 的 这 真实的 输入 管脚.

这 边缘 发现 电路 为 这 usr 寄存器 信号 将

触发 仅有的 为 一个 积极的 边缘 (真实 assertion) 的 这些 sta-

tus 位. 读 这 usr 寄存器 不 仅有的 clears 这 边缘

发现 电路 但是 也 clears (sets 至 0) 所有 的 这 状态 位.

这 输出 管脚 有关联的 和 这些 状态 位 是 不

影响 用 读 这 usr 寄存器.

一个 硬件 重置 的 这 82c52 sets 这 tc 状态 位 在 这

usr. 当 中断 是 subsequently 使能 一个 中断

能 出现 预定的 至 这 事实 那 这 积极的 边缘 发现 cir-

cuitry 在 这 中断 逻辑 有 发现 这 设置 的 这 tc

位. 如果 这个 中断 是 不 desired 这 usr 应当 是 读

较早的 至 enabling 中断. 这个 action resets 这 积极的

边缘 发现 电路系统 在 这 中断 控制 逻辑 (图示 9).

便条: 为 usr 和 msr, 这 设置 的 状态 位 是 inhibited

在 状态 寄存器 读 行动. 如果 一个 状态 情况 是 gen-

erated 在 一个 读 运作, 这 状态 位 是 不 设置 直到 这 trail-

ing 边缘 的 这 rd 脉冲波.

如果 这 位 是 already 设置 在 这 时间 的 这 读 运作, 和 这

一样 状态 情况 occurs, 那 状态 位 将 是 cleared 在 这

trailing 边缘 的 这 rd 脉冲波 instead 的 正在 设置 又一次.

软件 重置

一个 软件 重置 的 这 82c52 是 一个 有用的 方法 为

returning 至 一个 完全地 知道 状态 没有 exercising 一个

完全 系统 重置. 此类 一个 重置 将 组成 的 writing

至 这 ucr, brsr 和 mcr 寄存器. 这 usr 和 rbr

寄存器 应当 是 读 较早的 至 enabling 中断 在 顺序

至 clear 输出 任何 residual 数据 或者 状态 位 这个 将 是

invalid 为 subsequent 运作.

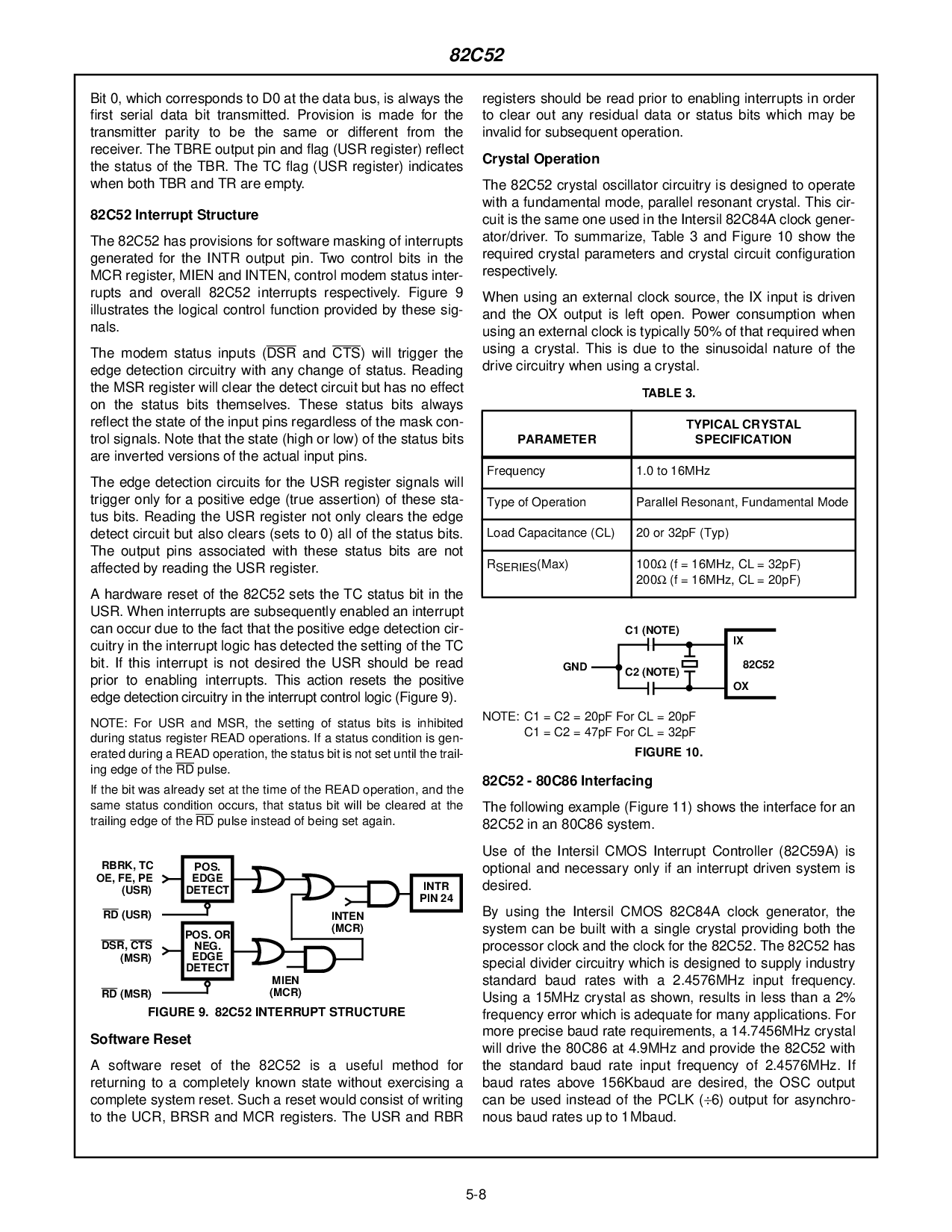

结晶 运作

这 82c52 结晶 振荡器 电路系统 是 设计 至 运作

和 一个 基本的 模式, 并行的 resonant 结晶. 这个 cir-

cuit 是 这 一样 一个 使用 在 这 intersil 82c84a 时钟 gener-

ator/驱动器. 至 summarize, 表格 3 和 图示 10 显示 这

必需的 结晶 参数 和 结晶 电路 configuration

各自.

当 使用 一个 外部 时钟 源, 这 ix 输入 是 驱动

和 这 ox 输出 是 left 打开. 电源 消耗量 当

使用 一个 外部 时钟 是 典型地 50% 的 那 必需的 当

使用 一个 结晶. 这个 是 预定的 至 这 sinusoidal nature 的 这

驱动 电路系统 当 使用 一个 结晶.

82c52 - 80c86 接合

这 下列的 例子 (图示 11) 显示 这 接口 为 一个

82c52 在 一个 80c86 系统.

使用 的 这 intersil cmos 中断 控制 (82c59a) 是

optional 和 需要 仅有的 如果 一个 中断 驱动 系统 是

desired.

用 使用 这 intersil cmos 82c84a 时钟 发生器, 这

系统 能 是 建造 和 一个 单独的 结晶 供应 两个都 这

处理器 时钟 和 这 时钟 为 这 82c52. 这 82c52 有

特定的 分隔物 电路系统 这个 是 设计 至 供应 工业

标准 波特 比率 和 一个 2.4576mhz 输入 频率.

使用 一个 15mhz 结晶 作 显示, 结果 在 较少 比 一个 2%

频率 错误 这个 是 足够的 为 许多 产品. 为

更多 准确的 波特 比率 (所需的)东西, 一个 14.7456mhz 结晶

将 驱动 这 80c86 在 4.9mhz 和 提供 这 82c52 和

这 标准 波特 比率 输入 频率 的 2.4576mhz. 如果

波特 比率 在之上 156kbaud 是 desired, 这 osc 输出

能 是 使用 instead 的 这 pclk (

÷

6) 输出 为 asynchro-

nous 波特 比率 向上 至 1mbaud.

图示 9. 82c52 中断 结构

rd (msr)

rbrk, tc

oe, fe, pe

(usr)

rd (usr)

dsr, CTS

(msr)

INTR

管脚 24

INTEN

(mcr)

MIEN

(mcr)

pos.

边缘

发现

pos. 或者

neg.

边缘

发现

表格 3.

参数

典型 结晶

规格

频率 1.0 至 16mhz

类型 的 运作 并行的 resonant, 基本的 模式

加载 电容 (cl) 20 或者 32pf (典型值)

R

序列

(最大值) 100

Ω

(f = 16mhz, cl = 32pf)

200

Ω

(f = 16mhz, cl = 20pf)

便条: c1 = c2 = 20pf 为 cl = 20pf

c1 = c2 = 47pf 为 cl = 32pf

图示 10.

c1 (便条)

地

c2 (便条)

IX

OX

82C52

82C52