5-4

重置

在 和 之后 电源-向上, 这 82c52 重置 输入 (rst)

必须 是 使保持 高 为 在 least 二 ix 时钟 循环 在 顺序 至

initialize 和 驱动 这 82c52 电路 至 一个 空闲 模式 直到

恰当的 程序编制 能 是 完毕. 一个 高 在 rst 导致

这 下列的 events 至 出现

• resets 这 内部的 波特 比率 发生器 (brg) 电路

时钟 counters 和 位 counters. 这 波特 比率 选择

寄存器 (brsr) 是 不 影响 (除了 为 位 7 这个 是

重置 至 0).

• clears 这 uart 状态 寄存器 (usr) 除了 为

传递 完全 (tc) 和 transmit 缓存区 寄存器

empty (tbre) 这个 是 设置. 这 modem 控制

寄存器 (mcr) 是 也 cleared. 所有 的 这 分离的 线条,

记忆 elements 和 miscellaneous 逻辑 有关联的

和 这些 寄存器 位 是 也 cleared 或者 转变 止. 便条

那 这 uart 控制 寄存器 (ucr) 是 不 影响.

下列的 除去 的 这 重置 情况 (rst = 低), 这

82c52 仍然是 在 这 空闲 模式 直到 编写程序 至 它的

desired 系统 configuration.

程序编制 这 82c52

这 完全 函数的 definition 的 这 82c52 是

编写程序 用 这 系统 软件. 一个 设置 的 控制 words

(ucr, brsr 和 mcr) 必须 是 sent 输出 用 这 cpu 至

initialize 这 82c52 至 支持 这 desired 交流

format. 这些 控制 words 将 程序 这 character

长度, 号码 的 停止 位, 甚至/odd/非 parity, 波特 rate,

等 once 编写程序, 这 82c52 是 准备好 至 执行 它的

交流 功能.

这 控制 寄存器 能 是 写 至 在 任何 顺序. 不管怎样,

这 mcr 应当 是 写 至 last 因为 它 控制 这

中断 使能, modem 控制 输出 和 这 接受者

使能 位. once 这 82c52 是 编写程序 和 运算的,

这些 寄存器 能 是 updated 任何 时间 这 82c52 是 不

立即 transmitting 或者 接到 数据.

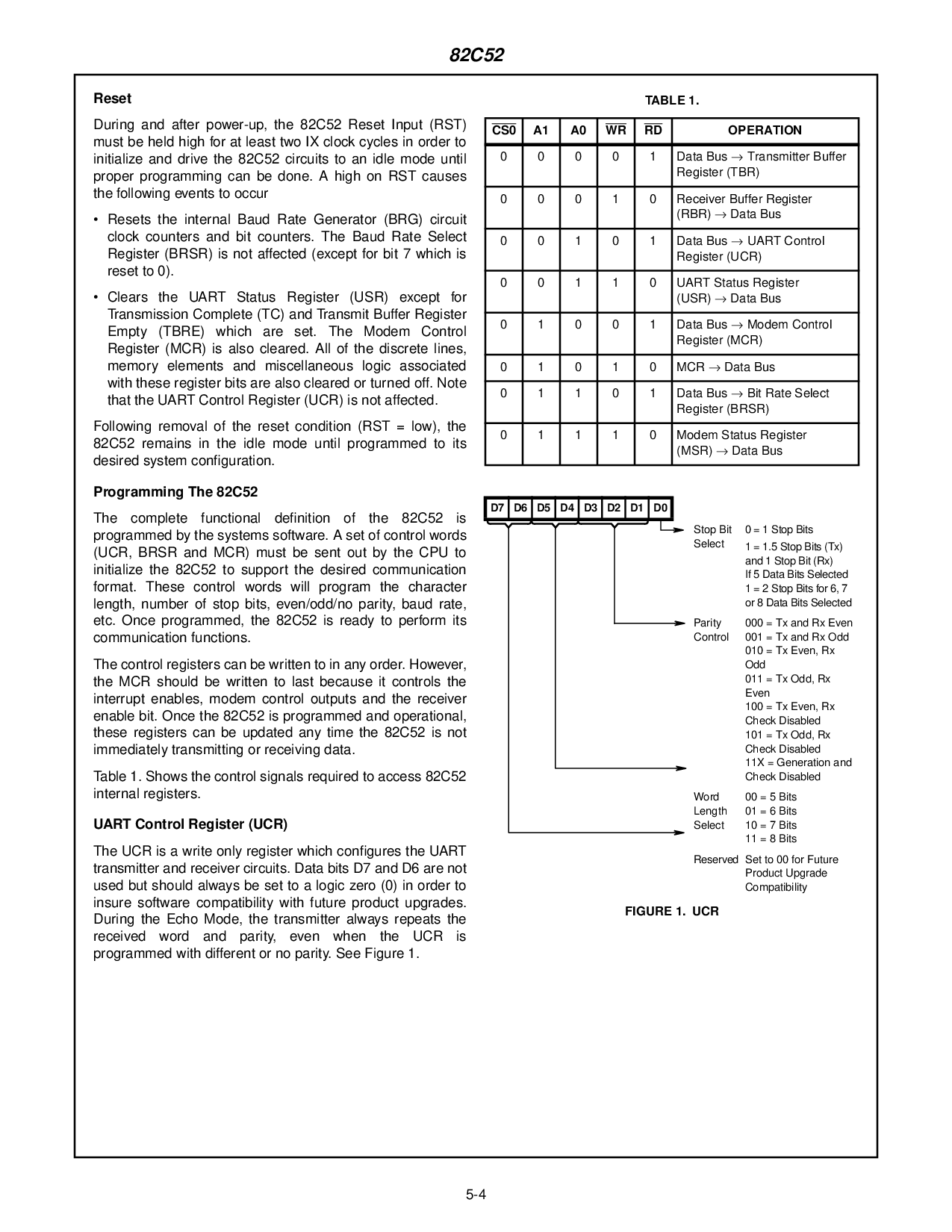

表格 1. 显示 这 控制 信号 必需的 至 进入 82c52

内部的 寄存器.

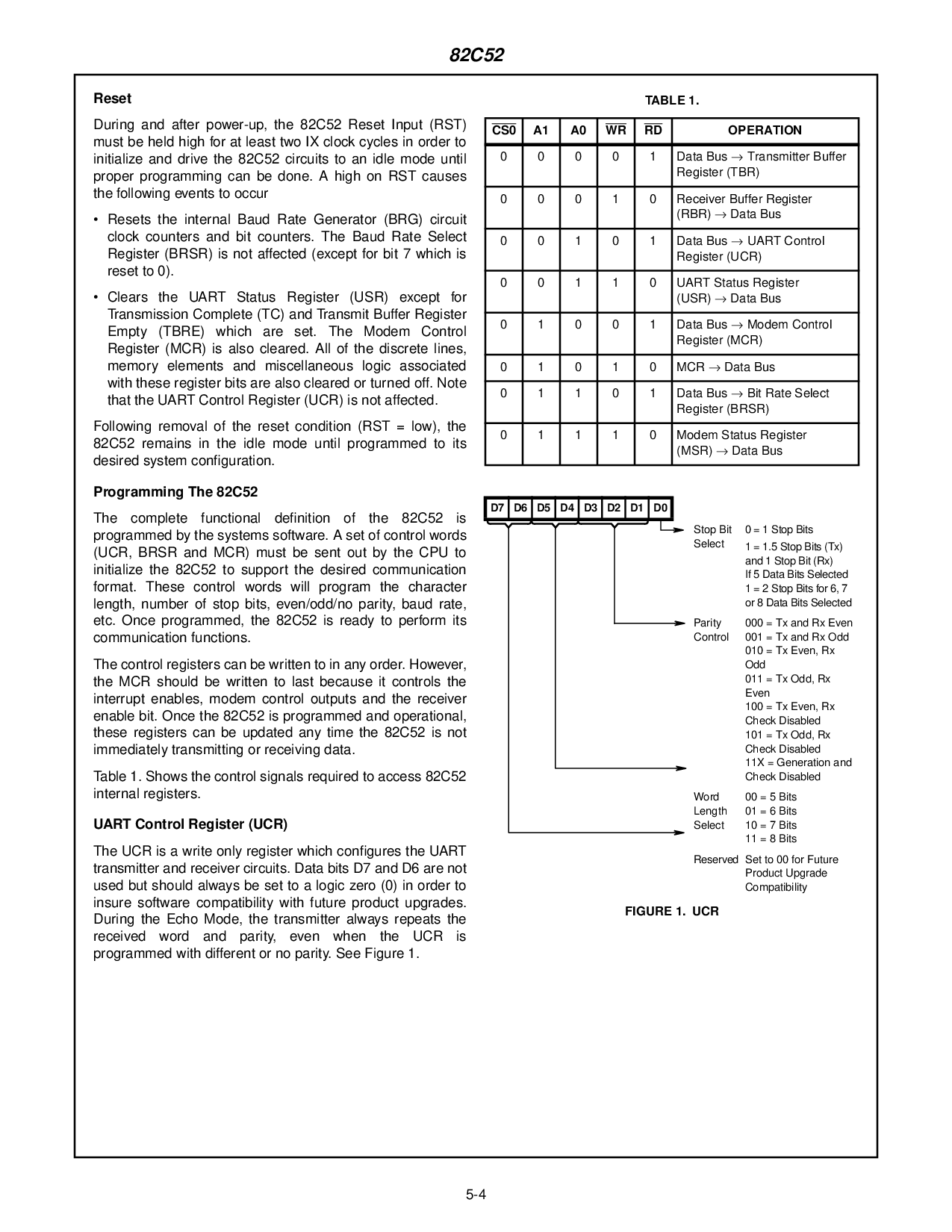

uart 控制 寄存器 (ucr)

这 ucr 是 一个 写 仅有的 寄存器 这个 configures 这 uart

传输者 和 接受者 电路. 数据 位 d7 和 d6 是 不

使用 但是 应当 总是 是 设置 至 一个 逻辑 零 (0) 在 顺序 至

insure 软件 兼容性 和 future 产品 升级.

在 这 echo 模式, 这 传输者 总是 repeats 这

received 文字 和 parity, 甚至 当 这 ucr 是

编写程序 和 不同的 或者 非 parity. 看 图示 1.

表格 1.

CS0 A1 A0 WR RD 运作

00001数据 总线

→

传输者 缓存区

寄存器 (tbr)

00010接受者 缓存区 寄存器

(rbr)

→

数据 总线

00101数据 总线

→

uart 控制

寄存器 (ucr)

00110uart 状态 寄存器

(usr)

→

数据 总线

01001数据 总线

→

modem 控制

寄存器 (mcr)

01010MCR

→

数据 总线

01101数据 总线

→

位 比率 选择

寄存器 (brsr)

01110modem 状态 寄存器

(msr)

→

数据 总线

D7 D6 D5 D4 D3 D2 D1 D0

停止 位

选择

0 = 1 停止 位

1 = 1.5 停止 位 (tx)

和 1 停止 位 (rx)

如果 5 数据 位 选择

1 = 2 停止 位 为 6, 7

或者 8 数据 位 选择

Parity

控制

000 = tx 和 rx 甚至

001 = tx 和 rx odd

010 = tx 甚至, rx

Odd

011 = tx odd, rx

甚至

100 = tx 甚至, rx

审查 无能

101 = tx odd, rx

审查 无能

11x = 一代 和

审查 无能

文字

长度

选择

00 = 5 位

01 = 6 位

10 = 7 位

11 = 8 位

保留 设置 至 00 为 future

产品 upgrade

兼容性

图示 1. UCR

82C52