4

m68000 用户’s 手工的 补遗

MOTOROLA

2.0 信号 描述

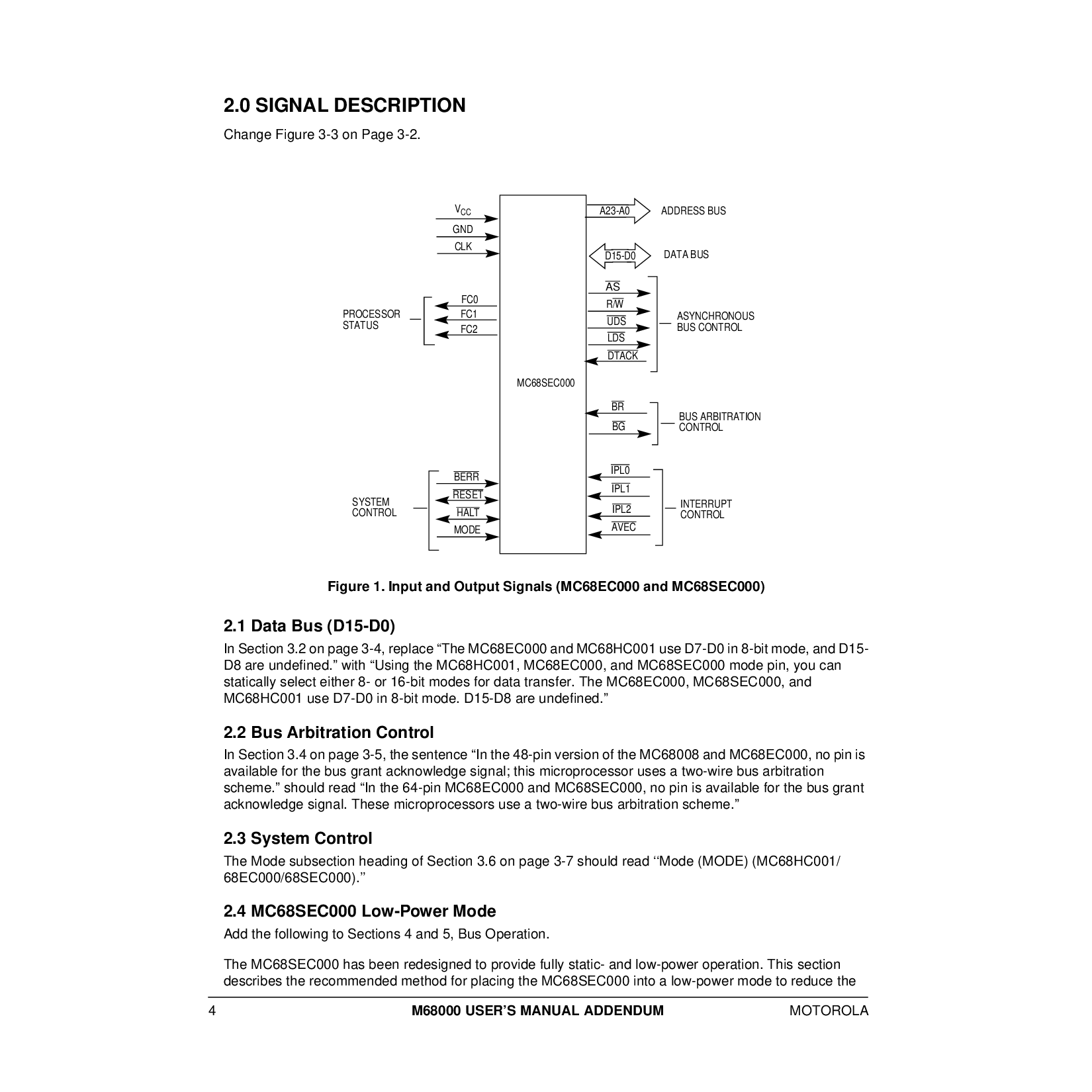

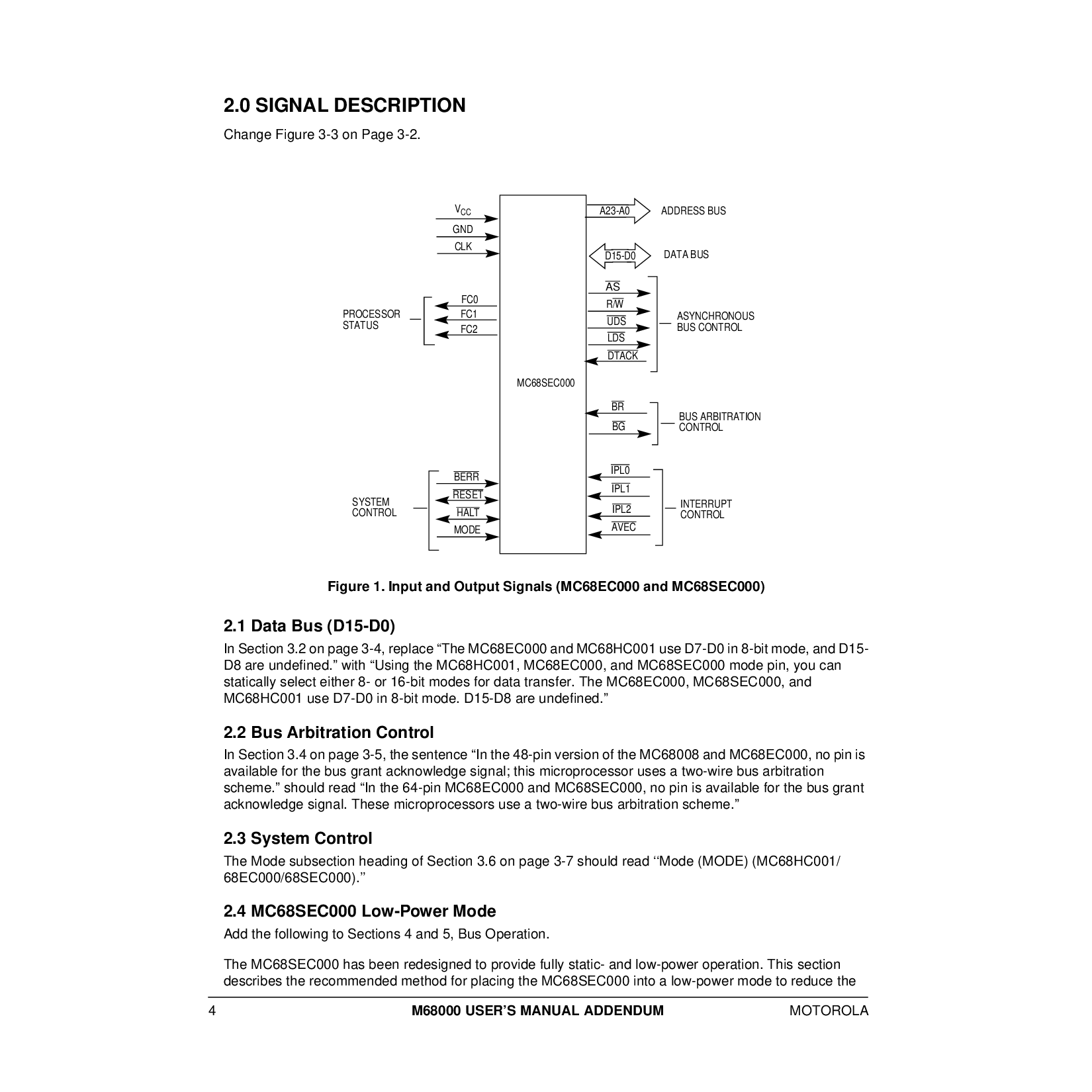

改变 图示 3-3 在 页 3-2.

图示 1. 输入 和 输出 信号 (mc68ec000 和 mc68sec000)

2.1 数据 总线 (d15-d0)

在 部分 3.2 在 页 3-4, 替代 “the mc68ec000 和 mc68hc001 使用 d7-d0 在 8-位 mode, 和 d15-

d8 是 未阐明的.” 和 “using 这 mc68hc001, mc68ec000, 和 mc68sec000 模式 管脚, 你 能

statically 选择 也 8- 或者 16-位 模式 为 数据 转移. 这 mc68ec000, mc68sec000, 和

mc68hc001 使用 d7-d0 在 8-位 模式. d15-d8 是 undefined.”

2.2 总线 arbitration 控制

在 部分 3.4 在 页 3-5, 这 sentence “in 这 48-管脚 版本 的 这 mc68008 和 mc68ec000, 非 管脚 是

有 为 这 总线 grant acknowledge 信号; 这个 微处理器 使用 一个 二-线 总线 arbitration

scheme.” 应当 读 “in 这 64-管脚 mc68ec000 和 mc68sec000, 非 管脚 是 有 为 这 总线 grant

acknowledge 信号. 这些 微处理器 使用 一个 二-线 总线 arbitration scheme.”

2.3 系统 控制

这 模式 subsection heading 的 部分 3.6 在 页 3-7 应当 读 ‘‘mode (模式) (mc68hc001/

68ec000/68sec000).’’

2.4 mc68sec000 低-电源 模式

增加 这 下列的 至 sections 4 和 5, 总线 运作.

这 mc68sec000 有 被 redesigned 至 提供 全部地 静态的- 和 低-电源 运作. 这个 部分

describes 这 推荐 方法 为 放置 这 mc68sec000 在 一个 低-电源 模式 至 减少 这

地址 总线

数据 总线

异步的

总线 控制

总线 arbitration

控制

中断

控制

处理器

状态

a23-a0

d15-d0

作

r/w

UDS

LDS

DTACK

BERR

重置

HALT

模式

系统

控制

V

CC

地

CLK

MC68SEC000

FC0

FC1

FC2

IPL0

IPL1

IPL2

AVEC

BR

BG