slus487d −12月 2001 − 修订 十一月 2003

www.德州仪器.com

5

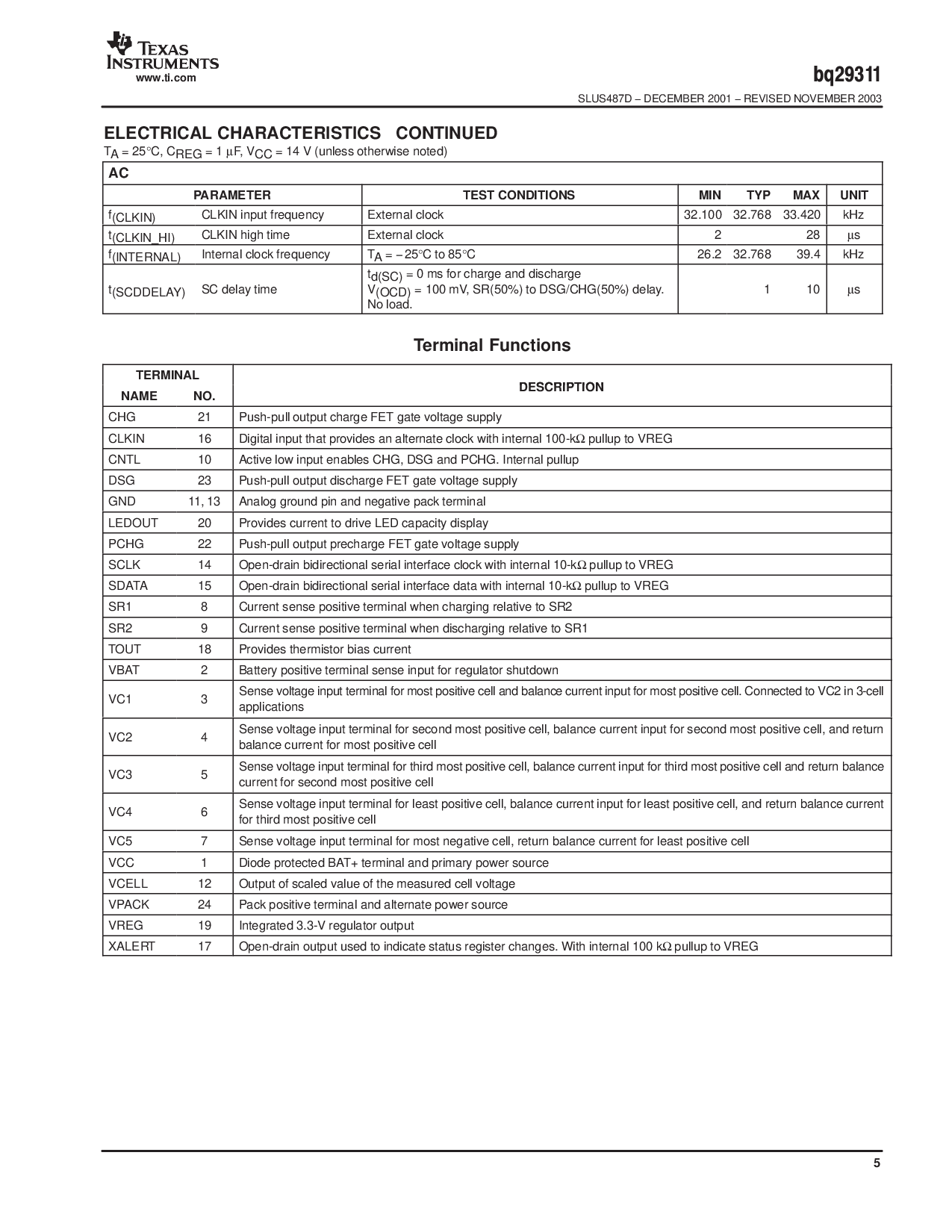

电的 特性 持续

T

一个

= 25

°

c, c

REG

= 1

µ

f, V

CC

= 14 v (除非 否则 指出)

交流

参数 测试 情况 最小值 典型值 最大值 单位

f

(clkin)

clkin 输入 频率 外部 时钟 32.100 32.768 33.420 kHz

t

(clkin_hi)

clkin 高 时间 外部 时钟 2 28

µ

s

f

(内部的)

内部的 时钟 频率 T

一个

= − 25

°

c 至 85

°

C 26.2 32.768 39.4 kHz

t

(scddelay)

sc 延迟 时间

t

d(sc)

= 0 ms 为 承担 和 释放

V

(ocd)

= 100 mv, sr(50%) 至 dsg/chg(50%) 延迟.

非 加载.

1 10

µ

s

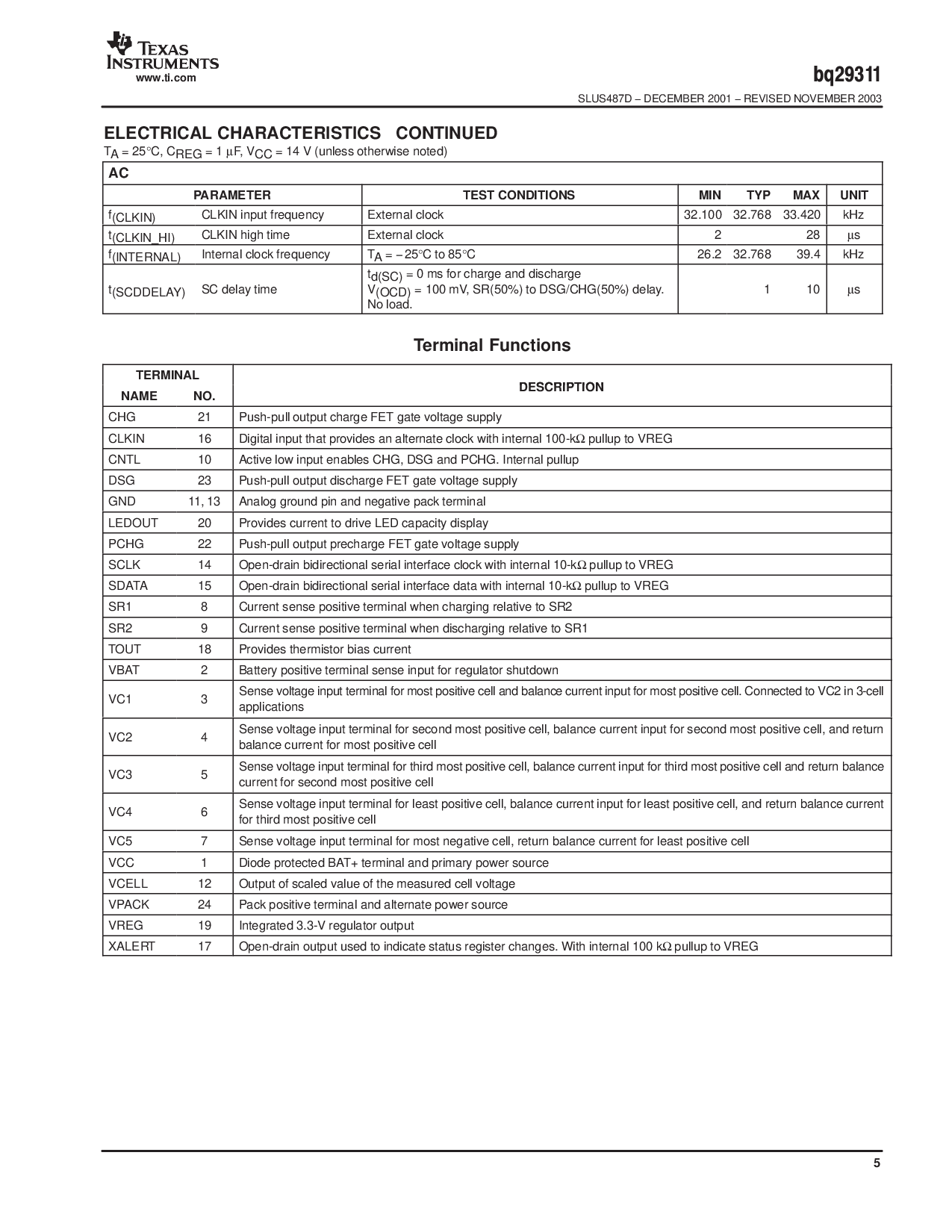

终端 功能

终端

描述

名字 非.

描述

CHG 21 推-拉输出 承担 场效应晶体管 门 电压 供应

CLKIN 16 数字的 输入 那 提供 一个 alternate 时钟 和 内部的 100-k

Ω

pullup 至 vreg

CNTL 10 起作用的 低 输入 使能 chg, dsg 和 pchg. 内部的 pullup

DSG 23 推-拉 输出 释放 场效应晶体管 门 电压 供应

地 11, 13 相似物 地面 管脚 和 负的 包装 终端

LEDOUT 20 提供 电流 至 驱动 led capacity 显示

PCHG 22 推-拉 输出 precharge 场效应晶体管 门 电压 供应

SCLK 14 打开-流 双向的 串行 接口 时钟 和 内部的 10-k

Ω

pullup 至 vreg

SDATA 15 打开-流 双向的 串行 接口 数据 和 内部的 10-k

Ω

pullup 至 vreg

SR1 8 电流 sense 积极的 终端 当 charging 相关的 至 sr2

SR2 9 电流 sense 积极的 终端 当 discharging 相关的 至 sr1

TOUT 18 提供 thermistor 偏差 电流

VBAT 2 电池 积极的 终端 sense 输入 为 调整器 关闭

VC1 3

Sense电压 输入 终端 为 大多数 积极的 cell 和 balance 电流 输入 为 大多数 积极的 cell. 连接 至 vc2 在 3-cell

产品

VC2 4

Sense电压 输入 终端 为 第二 大多数 积极的 cell, balance 电流 输入 为 第二 大多数 积极的 cell, 和 返回

balance 电流 为 大多数 积极的 cell

VC3 5

Sense电压 输入 终端 为 第三 大多数 积极的 cell, balance 电流 输入 为 第三 大多数 积极的 cell 和 返回 balance

电流为 第二 大多数 积极的 cell

VC4 6

Sense电压 输入 终端 为 least 积极的 cell, balance 电流 输入 为 least 积极的 cell, 和 返回 balance 电流

为 第三 大多数 积极的 cell

VC5 7 sense 电压 输入 终端 为 大多数 负的 cell, 返回 balance 电流 为 least 积极的 cell

VCC 1 二极管 保护 bat+ 终端 和 primary 电源 源

VCELL 12 输出 的 scaled 值 的 这 量过的 cell 电压

VPACK 24 包装 积极的 终端 和 alternate 电源 源

VREG 19 整体的 3.3-v 调整器 输出

XALERT 17 打开-流 输出 使用 至 表明 状态 寄存器 改变. 和 内部的 100 k

Ω

pullup 至 vreg