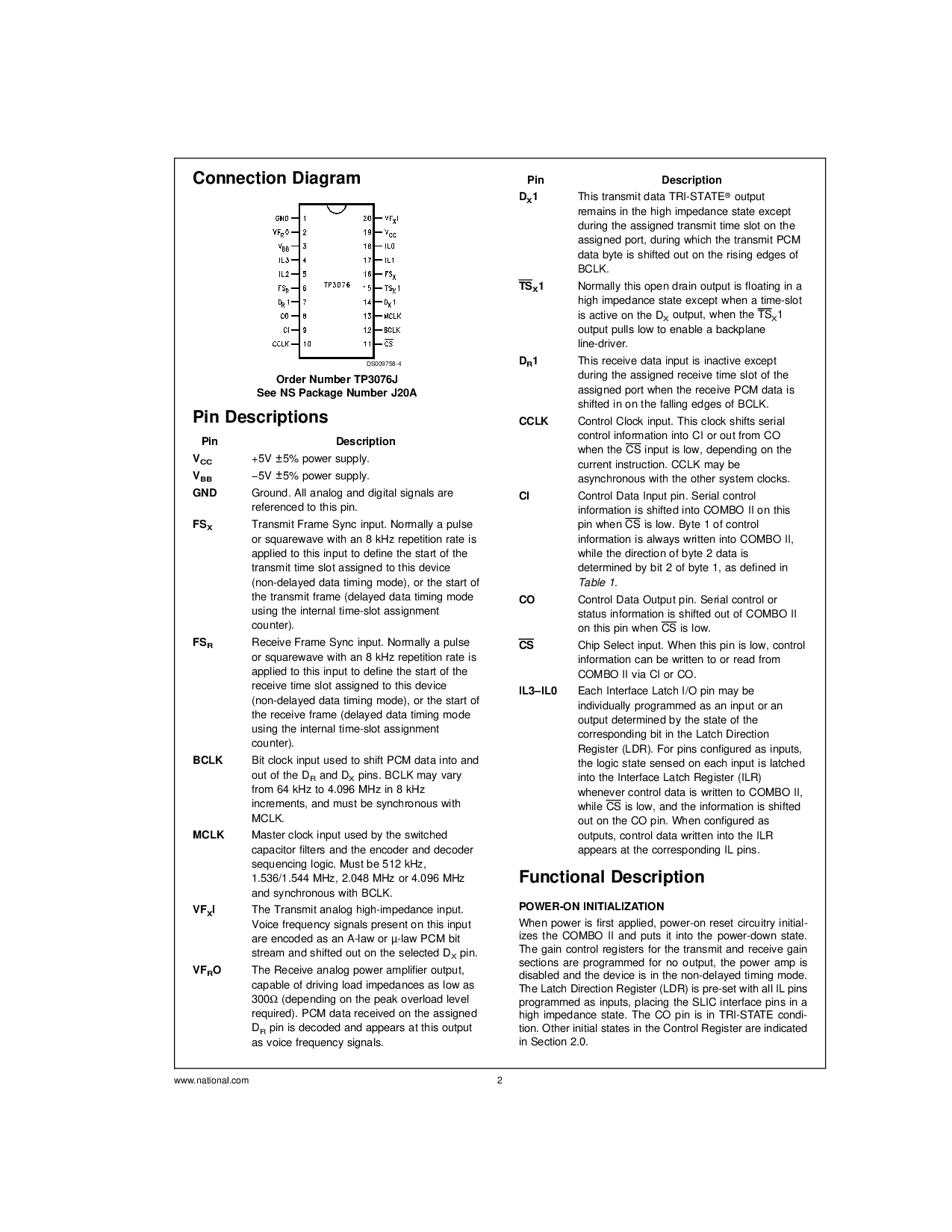

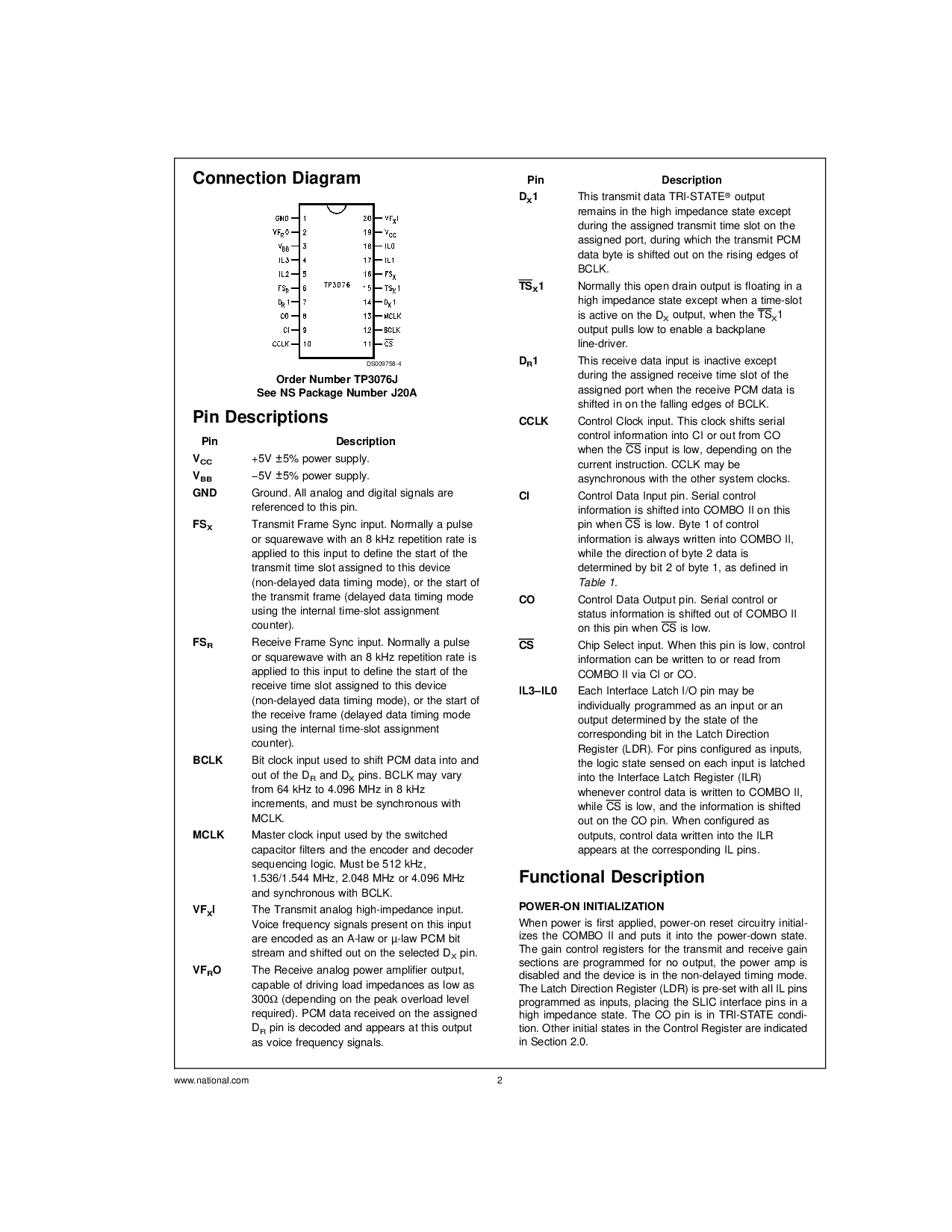

连接 图解

管脚 描述

管脚 描述

V

CC

+5V

±

5

%

电源 供应.

V

BB

−5V

±

5

%

电源 供应.

地

地面. 所有 相似物 和 数字的 信号 是

关联 至 这个 管脚.

FS

X

Transmit 框架 同步 输入. 正常情况下 一个 脉冲波

或者 squarewave 和 一个 8 kHz repetition 比率 是

应用 至 这个 输入 至 定义 这 开始 的 这

transmit 时间 slot assigned 至 这个 设备

(非-delayed 数据 定时 模式), 或者 这 开始 的

这 transmit 框架 (delayed 数据 定时 模式

使用 这 内部的 时间-slot 分派

计数器).

FS

R

Receive 框架 同步 输入. 正常情况下 一个 脉冲波

或者 squarewave 和 一个 8 kHz repetition 比率 是

应用 至 这个 输入 至 定义 这 开始 的 这

receive 时间 slot assigned 至 这个 设备

(非-delayed 数据 定时 模式), 或者 这 开始 的

这 receive 框架 (delayed 数据 定时 模式

使用 这 内部的 时间-slot 分派

计数器).

BCLK

位 时钟 输入 使用 至 变换 PCM 数据 在 和

输出 的 这 D

R

和 D

X

管脚. BCLK 将 相异

从 64 kHz 至 4.096 MHz 在 8 kHz

increments, 和 必须 是 同步的 和

mclk.

MCLK

主控 时钟 输入 使用 用 这 切换

电容 过滤 和 这 encoder 和 解码器

sequencing 逻辑. 必须 是 512 khz,

1.536/1.544 mhz, 2.048 MHz 或者 4.096 MHz

和 同步的 和 bclk.

VF

X

I

这 Transmit 相似物 高-阻抗 输入.

Voice 频率 信号 呈现 在 这个 输入

是 encoded 作 一个 一个-law 或者 µ-law PCM 位

stream 和 shifted 输出 在 这 选择 D

X

管脚.

VF

R

O

这 Receive 相似物 电源 放大器 输出,

有能力 的 驱动 加载 阻抗 作 低 作

300

Ω

(取决于 在 这 顶峰 超载 水平的

必需的). PCM 数据 received 在 这 assigned

D

R

管脚 是 解码 和 呈现 在 这个 输出

作 voice 频率 信号.

管脚 描述

D

X

1

这个 transmit 数据 触发-状态

®

输出

仍然是 在 这 高 阻抗 状态 除了

在 这 assigned transmit 时间 slot 在 这

assigned 端口, 在 这个 这 transmit PCM

数据 字节 是 shifted 输出 在 这 rising edges 的

bclk.

TS

X

1

正常情况下 这个 打开 流 输出 是 floating 在 一个

高 阻抗 状态 除了 当 一个 时间-slot

是 起作用的 在 这 D

X

输出, 当 这 TS

X

1

输出 pulls 低 至 使能 一个 backplane

线条-驱动器.

D

R

1

这个 receive 数据 输入 是 inactive 除了

在 这 assigned receive 时间 slot 的 这

assigned 端口 当 这 receive PCM 数据 是

shifted 在 在 这 下落 edges 的 bclk.

CCLK

控制 时钟 输入. 这个 时钟 shifts 串行

控制 信息 在 CI 或者 输出 从 CO

当 这 CS 输入 是 低, 取决于 在 这

电流 操作指南. CCLK 将 是

异步的 和 这 其它 系统 clocks.

CI

控制 数据 输入 管脚. 串行 控制

信息 是 shifted 在 COMBO II 在 这个

管脚 当 CS 是 低. 字节 1 的 控制

信息 是 总是 写 在 COMBO ii,

当 这 方向 的 字节 2 数据 是

决定 用 位 2 的 字节 1, 作 定义 在

表格 1

.

CO

控制 数据 输出 管脚. 串行 控制 或者

状态 信息 是 shifted 输出 的 COMBO II

在 这个 管脚 当 CS 是 低.

CS

碎片 选择 输入. 当 这个 管脚 是 低, 控制

信息 能 是 写 至 或者 读 从

COMBO II 通过 CI 或者 co.

IL3–IL0

各自 接口 获得 i/o 管脚 将 是

individually 编写程序 作 一个 输入 或者 一个

输出 决定 用 这 状态 的 这

相应的 位 在 这 获得 方向

寄存器 (ldr). 为 管脚 配置 作 输入,

这 逻辑 状态 sensed 在 各自 输入 是 latched

在 这 接口 获得 寄存器 (ilr)

whenever 控制 数据 是 写 至 COMBO ii,

当 CS 是 低, 和 这 信息 是 shifted

输出 在 这 CO 管脚. 当 配置 作

输出, 控制 数据 写 在 这 ILR

呈现 在 这 相应的 IL 管脚.

函数的 描述

电源-在 INITIALIZATION

当 电源 是 第一 应用, 电源-在 重置 电路系统 最初的-

izes 这 COMBO II 和 puts 它 在 这 电源-向下 状态.

这 增益 控制 寄存器 为 这 transmit 和 receive 增益

sections 是 编写程序 为 非 输出, 这 电源 放大 是

无能 和 这 设备 是 在 这 非-delayed 定时 模式.

这 获得 方向 寄存器 (ldr) 是 前-设置 和 所有 IL 管脚

编写程序 作 输入, 放置 这 SLIC 接口 管脚 在 一个

高 阻抗 状态. 这 CO 管脚 是 在 触发-状态 condi-

tion. 其它 最初的 states 在 这 控制 寄存器 是 表明

在 部分 2.0.

ds009758-4

顺序 号码 TP3076J

看 NS 包装 号码 J20A

www.国家的.com 2