函数的 描述

(持续)

vices (combo); 时间-slots begin nominally coincident 和

这 rising 边缘 的 这 适合的 FS 输入. 这 alternative 是

至 使用 Delayed 数据 模式, 这个 是 类似的 至 shortframe

同步 定时 在 combo, 在 这个 各自 FS 输入 必须 是 高

在 least 一个 half-循环 的 BCLK 早期 比 这 timeslot. 这

时间-slot 分派 电路 在 这 设备 能 仅有的 是 使用

和 Delayed 数据 定时.

当 使用 时间-slot 分派, 这 beginning 的 这 第一

时间-slot 在 一个 框架 是 identified 用 这 适合的 FS 输入.

这 真实的 transmit 和 receive 时间-slots 是 然后 deter-

mined 用 这 内部的 时间-slot 分派 counters.

Transmit 和 Receive frames 和 时间-slots 将 是 skewed

从 各自 其它 用 任何 号码 的 BCLK 循环. 在 各自

assigned Transmit 时间-slot, 这 D

X

1 输出 shifts 数据 输出

从 这 PCM 寄存器 在 这 rising edges 的 bclk. TS

X

1

也 pulls 低 为 这 第一 7

1

⁄

2

位 时间 的 这 时间-slot 至 con-

trol 这 触发-状态 使能 的 一个 backplane 线条-驱动器. 串行

PCM 数据 是 shifted 在 这 D

R

1 输入 在 各自 assigned

Receive 时间-slot 在 这 下落 edges 的 bclk.

串行 控制 端口

控制 信息 和 数据 是 写 在 或者 读-后面的

从 COMBO II 通过 这 串行 控制 端口 consisting 的 这

控制 时钟 cclk, 这 串行 数据 输入, ci, 和 输出, co,

和 这 碎片 选择 输入, cs. 所有 控制 说明 需要

2 字节, 作 列表

表格 1

, 和 这 例外 的 一个 单独的 字节

电源-向上/向下 command. 这 字节 1 位 是 使用 作 fol-

lows: 位 7 specifies 电源 向上 或者 电源 向下; 位 6, 5, 4 和

3 具体说明 这 寄存器 地址, 位 2 specifies whether 这 在-

构造 是 读 或者 写; 位 1 specifies 一个 一个 或者 二 字节 在-

构造; 和 位 0 是 不 使用.

至 变换 控制 数据 在 COMBO ii, CCLK 必须 是 搏动

高 8 时间 当 CS 是 低. 数据 在 这 CI 输入 是 shifted

在 这 串行 输入 寄存器 在 这 下落 边缘 的 各自 CCLK

脉冲波. 之后 所有 数据 是 shifted 在, 这 内容 的 这 输入

变换 寄存器 是 解码, 和 将 表明 那 一个 2nd 字节

的 控制 数据 将 follow. 这个 第二 字节 将 也 是 de-

fined 用 一个 第二 字节-宽 CS 脉冲波 或者 将 follow 这 第一

contiguously, i.e, 它 是 不 mandatory 为 CS 至 返回 高 是-

tween 这 第一 和 第二 控制 字节. 在 这 终止 的

CCLK8 在 这 2nd 控制 字节 这 数据 是 承载 在 这 ap-

propriate 可编程序的 寄存器. CS 将 仍然是 低 con-

tinuously 当 程序编制 successive 寄存器, 如果 de-

sired. 不管怎样, CS 必须 是 设置 高 当 非 数据 transfers

是 在 progress.

至 readback 接口 获得 数据 或者 状态 信息 从

COMBO ii, 这 第一 字节 的 这 适合的 操作指南 是

strobed 当 CS 是 低, 作 定义 在

表格 1

. CS 必须 是

保持 低, 或者 是 带去 低 又一次 为 一个 更远 8 CCLK 循环,

在 这个 这 数据 是 shifted 面向 这 CO 管脚 在 这 rising

edges 的 cclk. 当 CS 是 高 这 CO 管脚 是 在 这

高-阻抗 触发-状态, enabling 这 CI 和 CO 管脚 的

许多 设备 至 是 多路复用 一起.

如果 CS returns 高 在 也 字节 1 或者 字节 2 在之前 所有

第八 CCLK 脉冲 的 那 字节 出现, 两个都 这 位 计数 和

字节 计数 是 重置 和 寄存器 内容 是 不 影响.

这个 阻止 丧失 的 同步 在 这 控制 接口

作 好 作 corruption 的 寄存器 数据 预定的 至 处理器 inter-

rupt 或者 其它 问题. 当 CS returns 低 又一次, 这 de-

恶行 将 是 准备好 至 接受 位 1 的 字节 1 的 一个 新 instruc-

tion.

可编程序的 功能

电源-向上/向下 控制

下列的 电源-在 initialization, 电源-向上 和 电源-向下

控制 将 是 accomplished 用 writing 任何 的 这 控制 在-

structions 列表 在

表格 1

在 COMBO II 和 这 “P” 位 设置

至 “0” 为 电源-向上 或者 “1” 为 电源-向下. 正常情况下 它 是 rec-

ommended 那 所有 可编程序的 功能 是 initially pro-

grammed 当 这 设备 是 powered 向下. 电源 状态

控制 能 然后 是 包含 和 这 last 程序编制 在-

构造 或者 这 独立的 单独的-字节 操作指南. 任何 的 这

可编程序的 寄存器 将 也 是 修改 当 这 de-

恶行 是 powered-向上 或者 向下 用 设置 这 “P” 位 作 indi-

cated. 当 这 电源-向上 或者 向下 控制 是 entered 作 一个

单独的 字节 操作指南, 位 一个 (1) 必须 是 重置 至 一个 0.

当 一个 电源-向上 command 是 给, 所有 de-使活动 电路

是 使活动, 但是 这 触发-状态 PCM 输出(s), D

X

1 将 re-

主要的 在 这 高 阻抗 状态 直到 这 第二 FS

X

脉冲波

之后 电源-向上.

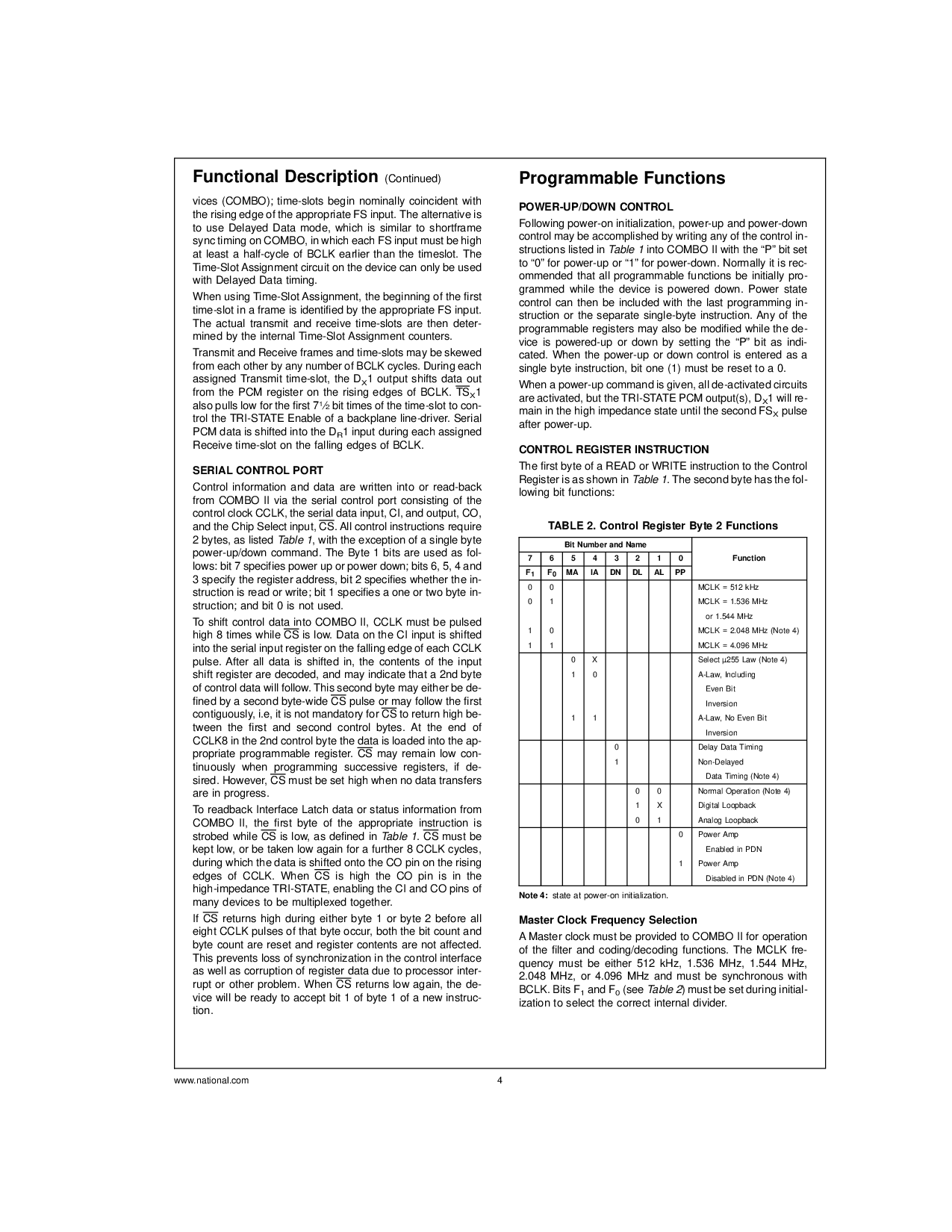

控制 寄存器 操作指南

这 第一 字节 的 一个 读 或者 写 操作指南 至 这 控制

寄存器 是 作 显示 在

表格 1

. 这 第二 字节 有 这 fol-

lowing 位 功能:

表格 2. 控制 寄存器 字节 2 功能

位 号码 和 名字

76543210 函数

F

1

F

0

毫安 IA DN DL AL PP

0 0 MCLK

=

512 kHz

0 1 MCLK

=

1.536 MHz

或者 1.544 MHz

1 0 MCLK

=

2.048 MHz (便条 4)

1 1 MCLK

=

4.096 MHz

0 X 选择 µ255 Law (便条 4)

1 0 一个-law, 包含

甚至 位

倒置

1 1 一个-law, 非 甚至 位

倒置

0 延迟 数据 定时

1 非-delayed

数据 定时 (便条 4)

0 0 正常的 运作 (便条 4)

1 X 数字的 Loopback

0 1 相似物 Loopback

0 电源 放大

使能 在 PDN

1 电源 放大

无能 在 PDN (便条 4)

便条 4:

状态 在 电源-在 initialization.

主控 时钟 频率 选择

一个 主控 时钟 必须 是 提供 至 COMBO II 为 运作

的 这 过滤 和 编码/解码 功能. 这 MCLK fre-

quency 必须 是 也 512 khz, 1.536 mhz, 1.544 mhz,

2.048 mhz, 或者 4.096 MHz 和 必须 是 同步的 和

bclk. 位 F

1

和 F

0

(看

表格 2

) 必须 是 设置 在 最初的-

ization 至 选择 这 准确无误的 内部的 分隔物.

www.国家的.com 4