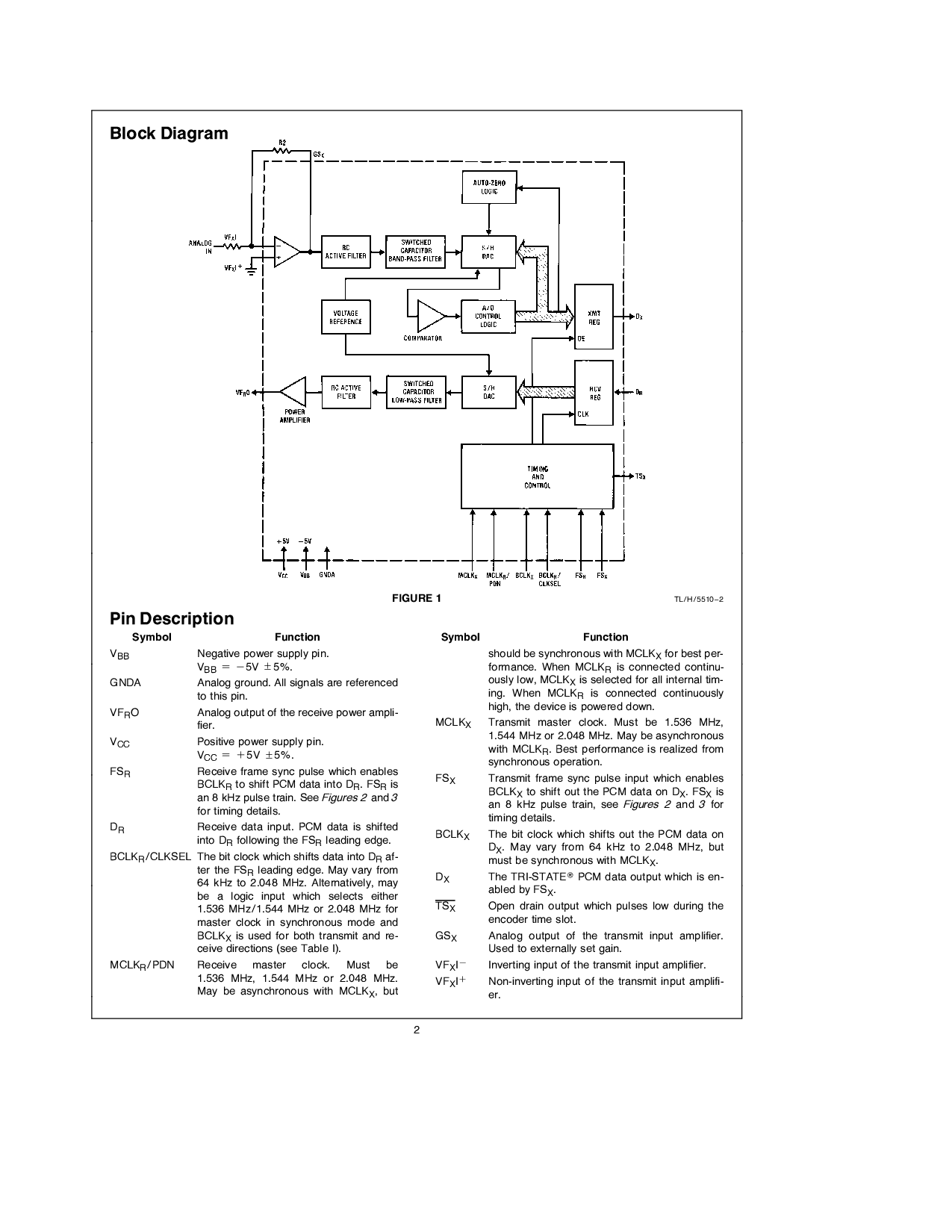

块 图解

图示 1

TLH5510–2

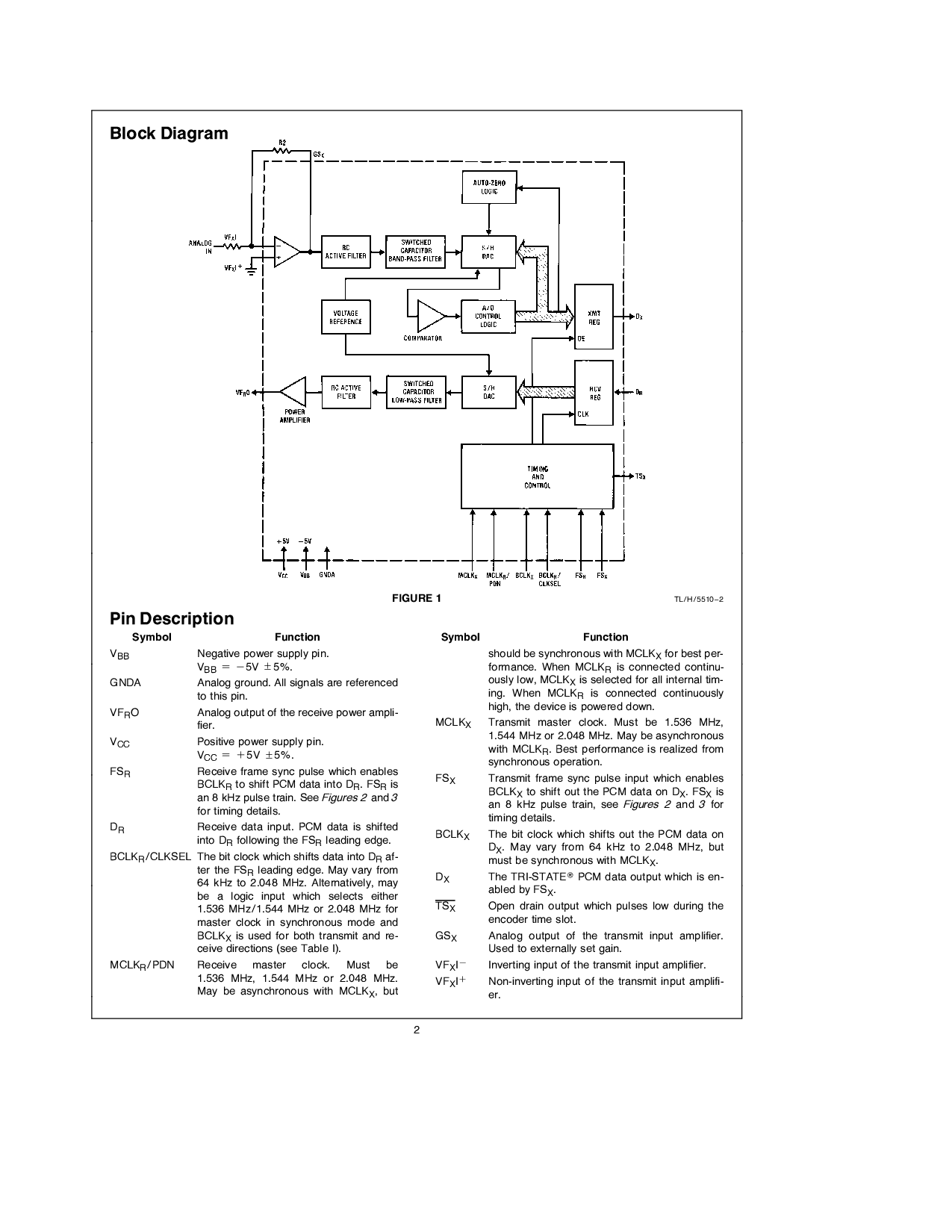

管脚 描述

标识 函数

V

BB

负的 电源 供应 pin

V

BB

eb

5V

g

5%

GNDA 相似物 ground 所有 信号 是 关联

至 这个 pin

VF

R

O 相似物 输出 的 这 receive 电源 放大器-

fier

V

CC

积极的 电源 供应 pin

V

CC

ea

5V

g

5%

FS

R

Receive 框架 同步 脉冲波 这个 使能

BCLK

R

至 变换 PCM 数据 在 D

R

FS

R

是

一个 8 kHz 脉冲波 train 看

计算数量 2

和

3

为 定时 details

D

R

Receive 数据 input PCM 数据 是 shifted

在 D

R

下列的 这 FS

R

leading edge

BCLK

R

CLKSEL 这 位 时钟 这个 shifts 数据 在 D

R

af-

ter 这 FS

R

leading edge 将 相异 从

64 kHz 至 2048 MHz Alternatively 将

是 一个 逻辑 输入 这个 选择 也

1536 MHz1544 MHz 或者 2048 MHz 为

主控 时钟 在 同步的 模式 和

BCLK

X

是 使用 为 两个都 transmit 和 re-

ceive 方向 (看 表格 i)

MCLK

R

PDN Receive 主控 clock 必须 是

1536 MHz 1544 MHz 或者 2048 MHz

将 是 异步的 和 MCLK

X

但是

标识 函数

应当 是 同步的 和 MCLK

X

为 最好的 每-

formance 当 MCLK

R

是 连接 continu-

ously low MCLK

X

是 选择 为 所有 内部的 tim-

ing 当 MCLK

R

是 连接 continuously

high 这 设备 是 powered down

MCLK

X

Transmit 主控 clock 必须 是 1536 MHz

1544 MHz 或者 2048 MHz 将 是 异步的

和 MCLK

R

最好的 效能 是 认识到 从

同步的 operation

FS

X

Transmit 框架 同步 脉冲波 输入 这个 使能

BCLK

X

至 变换 输出 这 PCM 数据 在 D

X

FS

X

是

一个 8 kHz 脉冲波 train 看

计算数量 2

和

3

为

定时 details

BCLK

X

这 位 时钟 这个 shifts 输出 这 PCM 数据 在

D

X

将 相异 从 64 kHz 至 2048 MHz 但是

必须 是 同步的 和 MCLK

X

D

X

这 触发-状态

PCM 数据 输出 这个 是 en-

abled 用 FS

X

TS

X

打开 流 输出 这个 脉冲 低 在 这

encoder 时间 slot

GS

X

相似物 输出 的 这 transmit 输入 amplifier

使用 至 externally 设置 gain

VF

X

I

b

反相的 输入 的 这 transmit 输入 amplifier

VF

X

I

一个

非-反相的 输入 的 这 transmit 输入 amplifi-

er

2