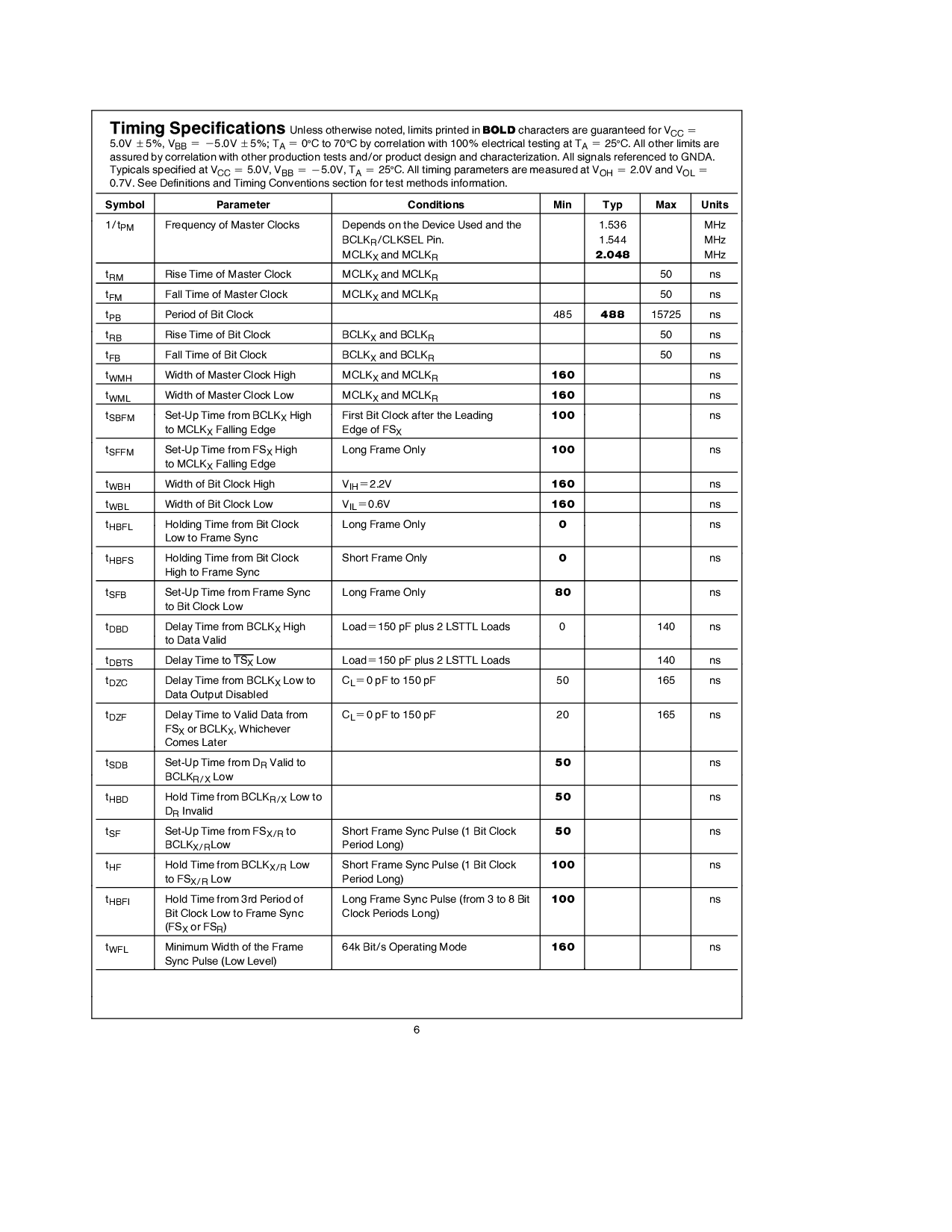

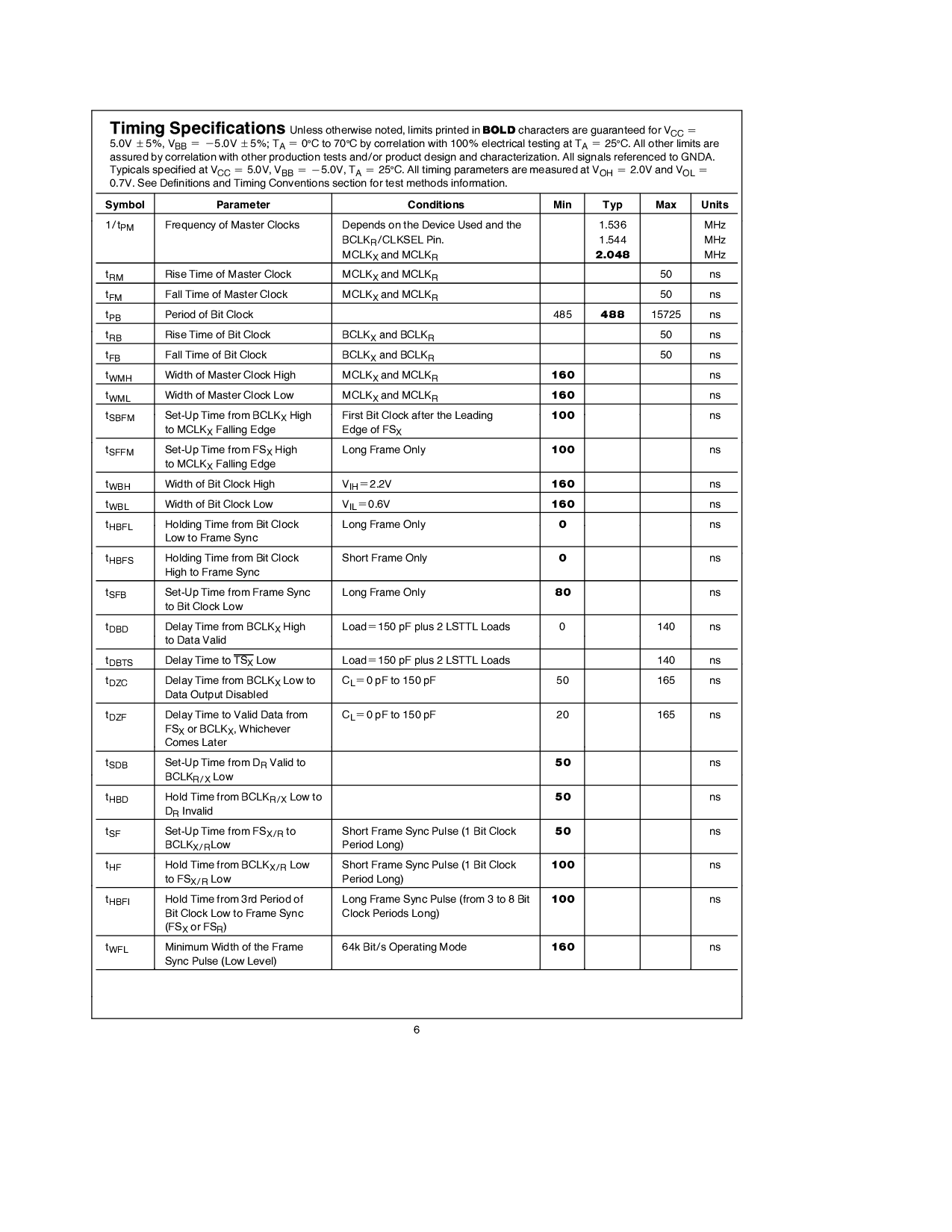

定时 规格

除非 否则 noted 限制 打印 在

BOLD

characters 是 有保证的 为 V

CC

e

50V

g

5% V

BB

eb

50V

g

5% T

一个

e

0

Cto70

C 用 correlation 和 100% 电的 测试 在 T

一个

e

25

C 所有 其它 限制 是

使确信 用 correlation 和 其它 生产 tests andor 产品 设计 和 characterization 所有 信号 关联 至 GNDA

Typicals 指定 在 V

CC

e

50V V

BB

eb

50V T

一个

e

25

C 所有 定时 参数 是 量过的 在 V

OH

e

20V 和 V

OL

e

07V 看 定义 和 定时 Conventions 部分 为 测试 方法 information

标识 参数 情况 最小值 典型值 最大值 单位

1t

PM

频率 的 主控 Clocks 取决于 在 这 设备 使用 和 这 1536 MHz

BCLK

R

CLKSEL Pin 1544 MHz

MCLK

X

和 MCLK

R

2048

MHz

t

RM

上升 时间 的 主控 时钟 MCLK

X

和 MCLK

R

50 ns

t

FM

下降 时间 的 主控 时钟 MCLK

X

和 MCLK

R

50 ns

t

铅

时期 的 位 时钟 485

488

15725 ns

t

RB

上升 时间 的 位 时钟 BCLK

X

和 BCLK

R

50 ns

t

FB

下降 时间 的 位 时钟 BCLK

X

和 BCLK

R

50 ns

t

WMH

宽度 的 主控 时钟 高 MCLK

X

和 MCLK

R

160

ns

t

WML

宽度 的 主控 时钟 低 MCLK

X

和 MCLK

R

160

ns

t

SBFM

设置-向上 时间 从 BCLK

X

高 第一 位 时钟 之后 这 Leading

100

ns

至 MCLK

X

下落 边缘 边缘 的 FS

X

t

SFFM

设置-向上 时间 从 FS

X

高 长 框架 仅有的

100

ns

至 MCLK

X

下落 边缘

t

WBH

宽度 的 位 时钟 高 V

IH

e

22V

160

ns

t

WBL

宽度 的 位 时钟 低 V

IL

e

06V

160

ns

t

HBFL

支持 时间 从 位 时钟 长 框架 仅有的

0

ns

低 至 框架 同步

t

HBFS

支持 时间 从 位 时钟 短的 框架 仅有的

0

ns

高 至 框架 同步

t

SFB

设置-向上 时间 从 框架 同步 长 框架 仅有的

80

ns

至 位 时钟 低

t

DBD

延迟 时间 从 BCLK

X

高 加载

e

150 pF 加 2 LSTTL 负载 0 140 ns

至 数据 有效的

t

DBTS

延迟 时间 至 TS

X

低 加载

e

150 pF 加 2 LSTTL 负载 140 ns

t

DZC

延迟 时间 从 BCLK

X

低 至 C

L

e

0 pF 至 150 pF 50 165 ns

数据 输出 无能

t

DZF

延迟 时间 至 有效的 数据 从 C

L

e

0 pF 至 150 pF 20 165 ns

FS

X

或者 BCLK

X

Whichever

Comes 后来的

t

SDB

设置-向上 时间 从 D

R

有效的 至

50

ns

BCLK

RX

低

t

HBD

支撑 时间 从 BCLK

RX

低 至

50

ns

D

R

Invalid

t

SF

设置-向上 时间 从 FS

XR

至 短的 框架 同步 脉冲波 (1 位 时钟

50

ns

BCLK

XR

低 时期 长)

t

HF

支撑 时间 从 BCLK

XR

低 短的 框架 同步 脉冲波 (1 位 时钟

100

ns

至 FS

XR

低 时期 长)

t

HBFl

支撑 时间 从 3rd 时期 的 长 框架 同步 脉冲波 (从 3 至 8 位

100

ns

位 时钟 低 至 框架 同步 时钟 时期 长)

(fs

X

或者 FS

R

)

t

WFL

最小 宽度 的 这 框架 64k Bits 运行 模式

160

ns

同步 脉冲波 (低 水平的)

6