W83194R-67B

初步的

发行 释放 日期: dec.. 1999

-4-修订 0.50

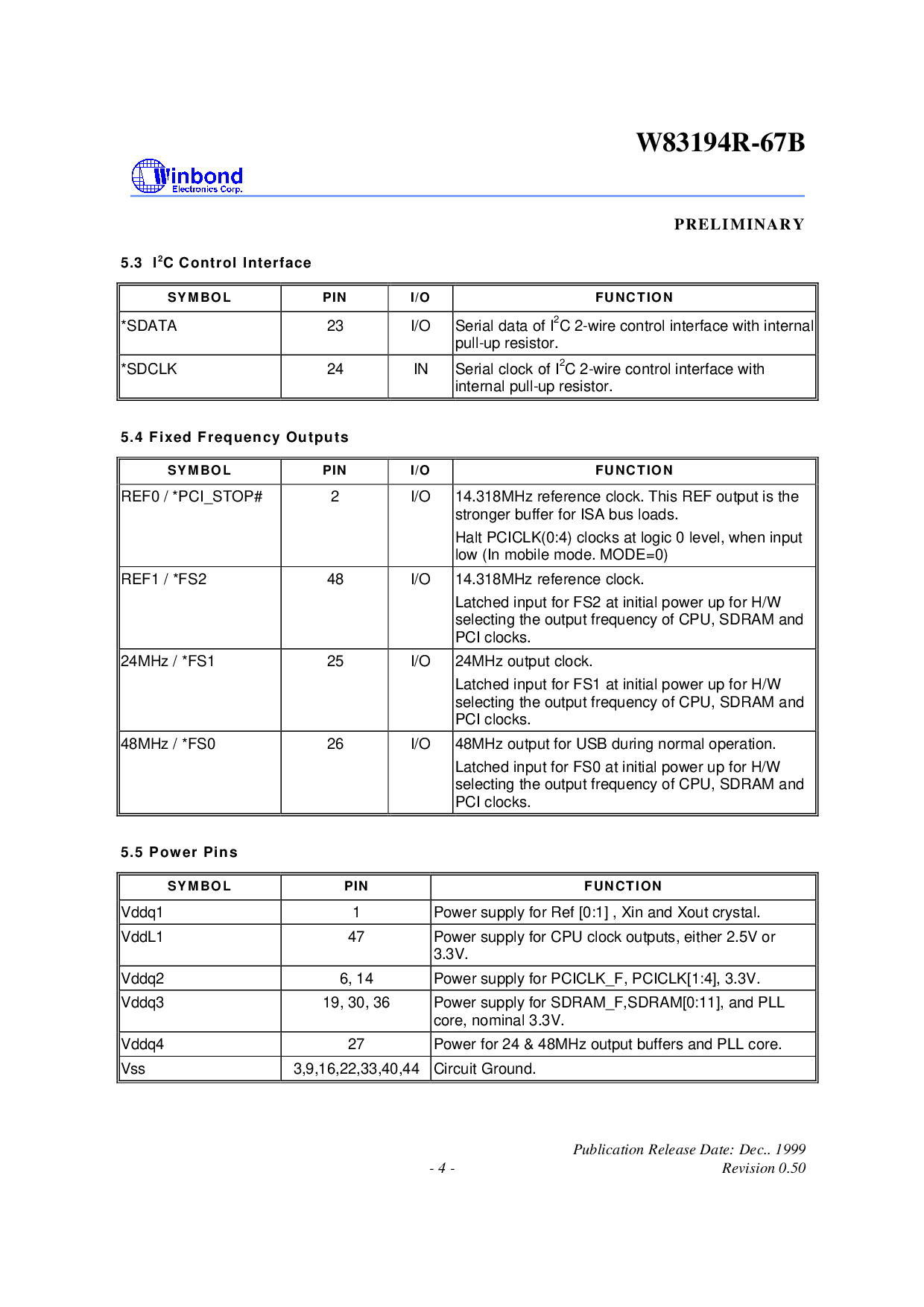

5.3 i

2

c 控制 接口

标识 管脚 i/o 函数

*SDATA 23 i/o 串行 数据 的 i

2

c 2-线控制 接口 和 内部的

拉-向上 电阻.

*SDCLK 24 在 串行 时钟 的 i

2

c 2-线 控制 接口 和

内部的 拉-向上 电阻.

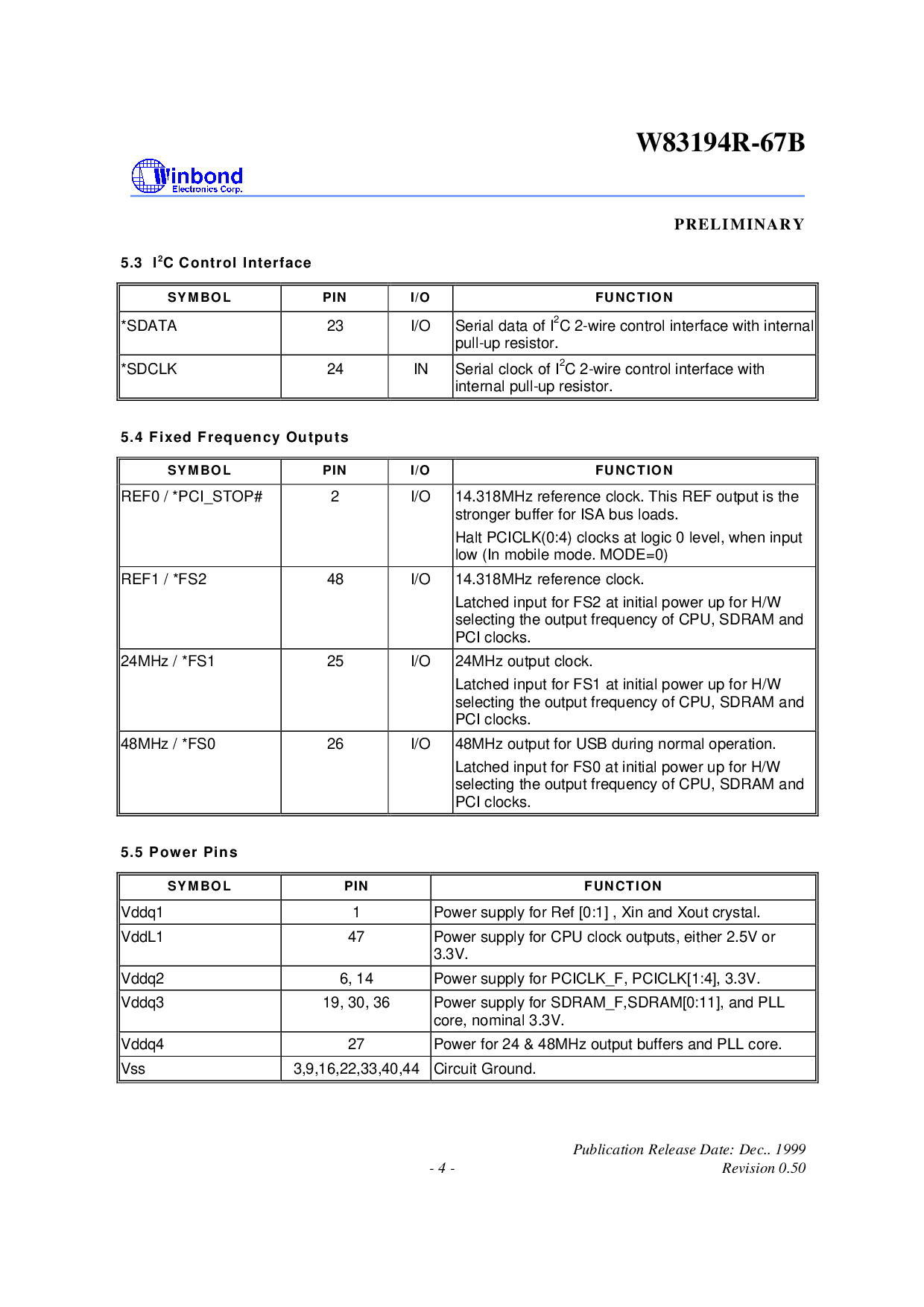

5.4 fixed 频率 输出

标识 管脚 i/o 函数

ref0 / *pci_stop# 2 i/o 14.318mhz 涉及 时钟. 这个 ref输出 是 这

stronger 缓存区 为 isa 总线 负载.

halt pciclk(0:4) clocks 在 逻辑 0 水平的, 当 输入

低 (在 mobile 模式. 模式=0)

ref1 / *fs2 48 i/o 14.318mhz 涉及 时钟.

latched 输入 为 fs2 在 最初的 电源 向上 为 h/w

selecting 这 输出 frequency 的 cpu, sdram 和

pci clocks.

24mhz / *fs1 25 i/o 24mhz 输出 时钟.

latched 输入 为 fs1 在 最初的 电源 向上 为 h/w

selecting 这 输出 频率 的 cpu, sdram 和

pci clocks.

48mhz / *fs0 26 i/o 48mhz 输出 为 usb 在 正常的 运作.

Latched 输入 为 fs0 在 最初的 电源 向上 为 h/w

selecting 这 输出 频率 的 cpu, sdram 和

pci clocks.

5.5 电源 管脚

标识 管脚 函数

Vddq1 1 电源 供应 为 ref [0:1] , xin 和 xout 结晶.

VddL1 47 电源 供应 为 cpu 时钟 输出, either 2.5v 或者

3.3v.

Vddq2 6, 14 电源 供应 为 pciclk_f, pciclk[1:4], 3.3v.

Vddq3 19, 30, 36 电源 供应 为 sdram_f,sdram[0:11], 和 pll

核心, 名义上的 3.3v.

Vddq4 27 电源 为 24 &放大; 48mhz 输出 缓存区 和 pll 核心.

Vss 3,9,16,22,33,40,44 电路地面.