W83877TF

发行 释放 日期: march 1998

-40- 版本 0.61

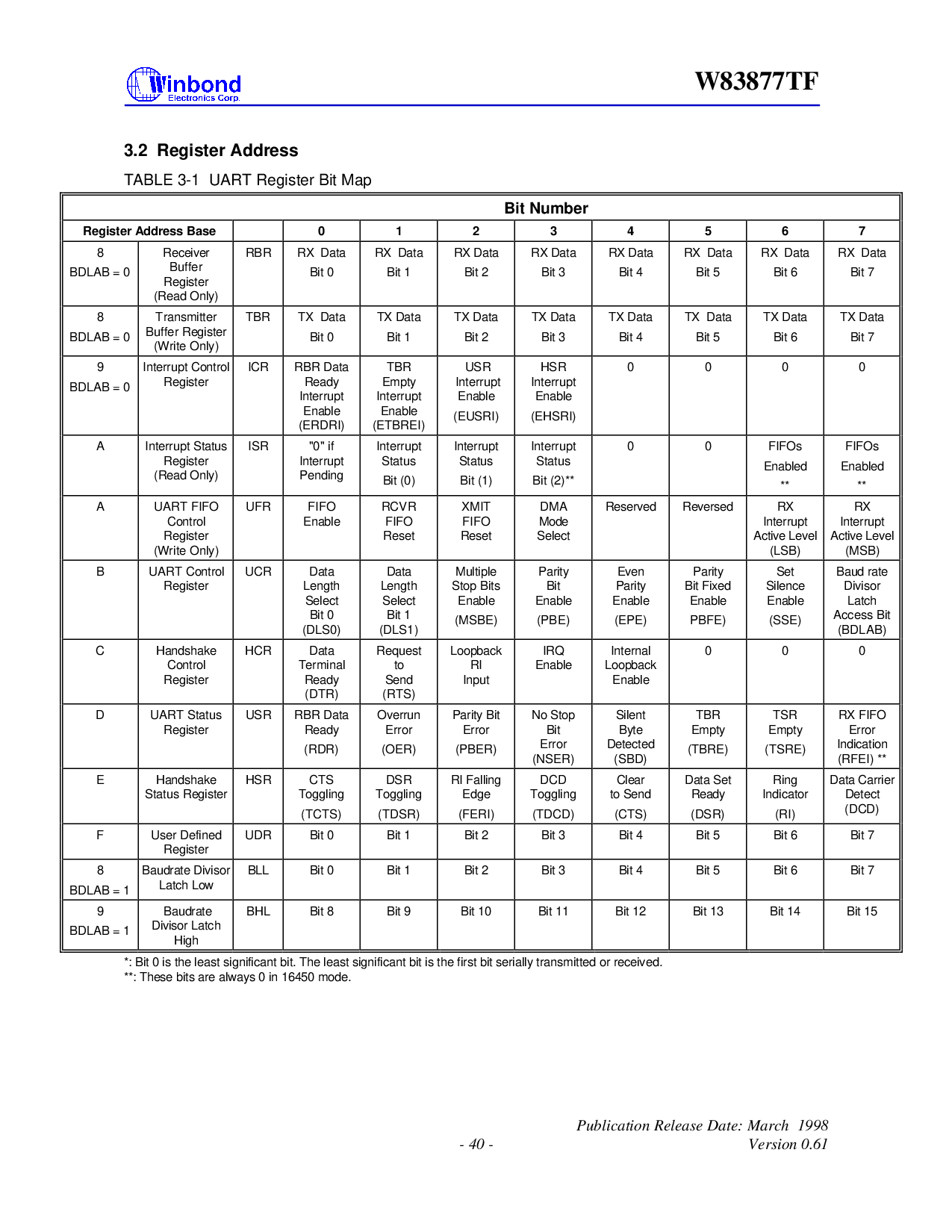

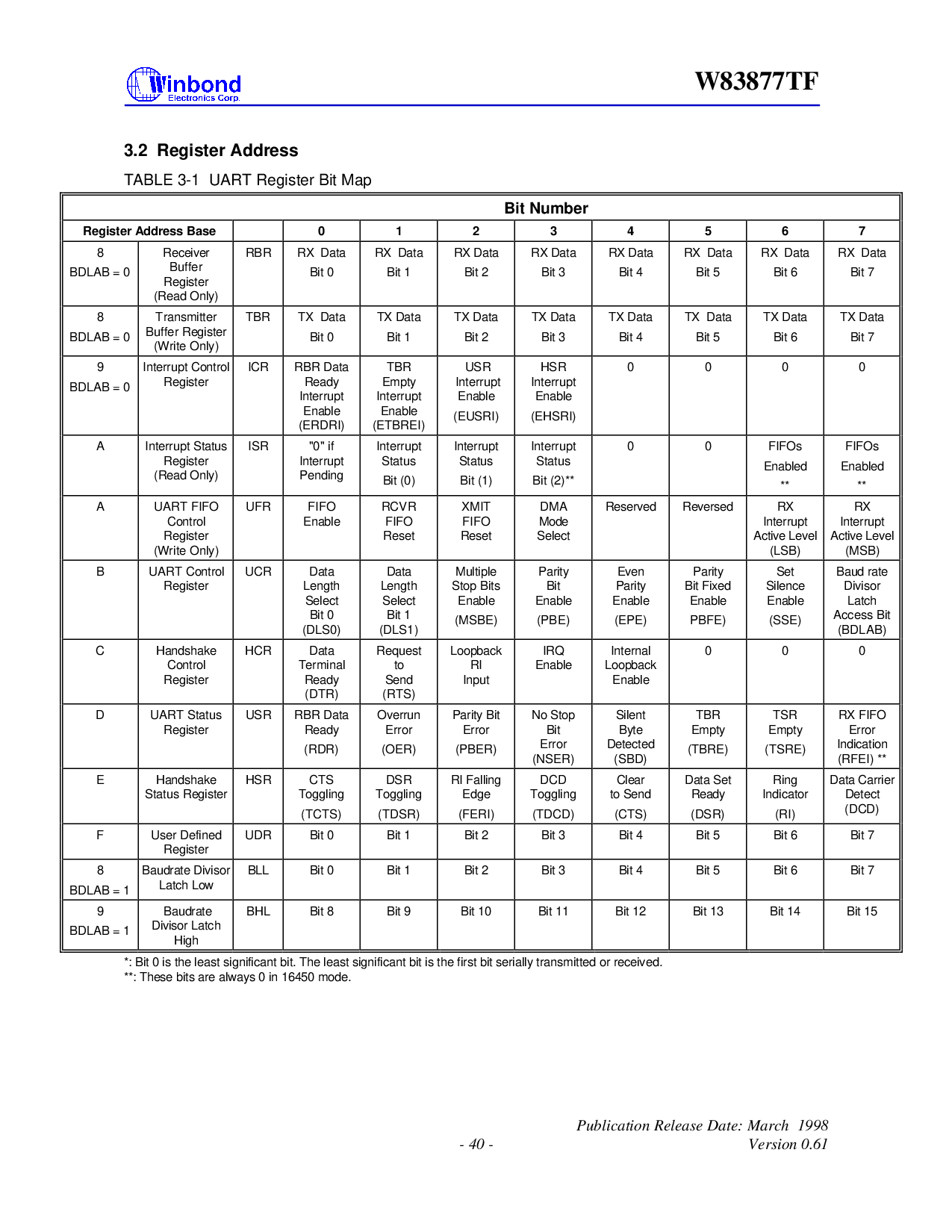

3.2 寄存器 地址

表格 3-1 uart 寄存器 位 编排

B它Number

Register一个ddressBase 0 1 2 3 4 5 6 7

8

bdlab = 0

Receiver

Buffer

Register

(读 仅有的)

RBR rx 数据

位 0

rx 数据

位 1

rx 数据

位 2

rx 数据

位 3

rx 数据

位 4

rx 数据

位 5

rx 数据

位 6

rx 数据

位 7

8

bdlab = 0

Transmitter

BufferRegister

(写 仅有的)

TBR tx 数据

位 0

tx 数据

位 1

tx 数据

位 2

tx 数据

位 3

tx 数据

位 4

tx 数据

位 5

tx 数据

位 6

tx 数据

位 7

9

bdlab = 0

InterruptControl

Register

ICR rbr 数据

准备好

中断

使能

(erdri)

TBR

Empty

中断

使能

(etbrei)

USR

中断

使能

(eusri)

HSR

中断

使能

(ehsri)

0 0 0 0

一个 InterruptStatus

Register

(读 仅有的)

ISR "0" 如果

中断

Pending

中断

状态

位 (0)

中断

状态

位 (1)

中断

状态

位 (2)**

0 0 FIFOs

使能

**

FIFOs

使能

**

一个 U艺术先进先出

Control

Register

(写 仅有的)

UFR 先进先出

使能

RCVR

先进先出

重置

XMIT

先进先出

重置

DMA

模式

选择

保留 使反转 RX

中断

起作用的 水平的

(lsb)

RX

中断

起作用的 水平的

(msb)

B U艺术Control

Register

UCR 数据

长度

选择

位 0

(dls0)

数据

长度

选择

位 1

(dls1)

多样的

停止 位

使能

(msbe)

Parity

位

使能

(pbe)

甚至

Parity

使能

(epe)

Parity

位 fixed

使能

pbfe)

设置

Silence

使能

(sse)

波特 比率

Divisor

获得

进入 位

(bdlab)

C Handshake

Control

Register

HCR 数据

终端

准备好

(dtr)

要求

至

Send

(rts)

Loopback

RI

输入

IRQ

使能

内部的

Loopback

使能

0 0 0

D U艺术Status

Register

USR rbr 数据

准备好

(rdr)

Overrun

错误

(oer)

parity 位

错误

(pber)

非 停止

位

错误

(nser)

Silent

字节

发现

(sbd)

TBR

Empty

(tbre)

TSR

Empty

(tsre)

rx 先进先出

错误

Indication

(rfei) **

E Handshake

StatusRegister

HSR CTS

Toggling

(tcts)

DSR

Toggling

(tdsr)

ri 下落

边缘

(feri)

DCD

Toggling

(tdcd)

Clear

至 send

(cts)

数据 设置

准备好

(dsr)

环绕

指示信号

(ri)

数据 运输车

发现

(dcd)

F UserDefined

Register

UDR 位 0 位 1 位 2 位 3 位 4 位 5 位 6 位 7

8

bdlab = 1

BaudrateDivisor

LatchLow

BLL 位 0 位 1 位 2 位 3 位 4 位 5 位 6 位 7

9

bdlab = 1

Baudrate

DivisorLatch

High

BHL 位 8 位 9 位 10 位 11 位 12 位 13 位 14 位 15

*: 位 0 是 这 least 重大的 位. 这 least 重大的 位 是 这 第一 位 serially transmitted 或者 received.

**: 这些 位 是 总是 0 在 16450 模式.