W83877TF

发行 释放 日期: march 1998

-42- 版本 0.61

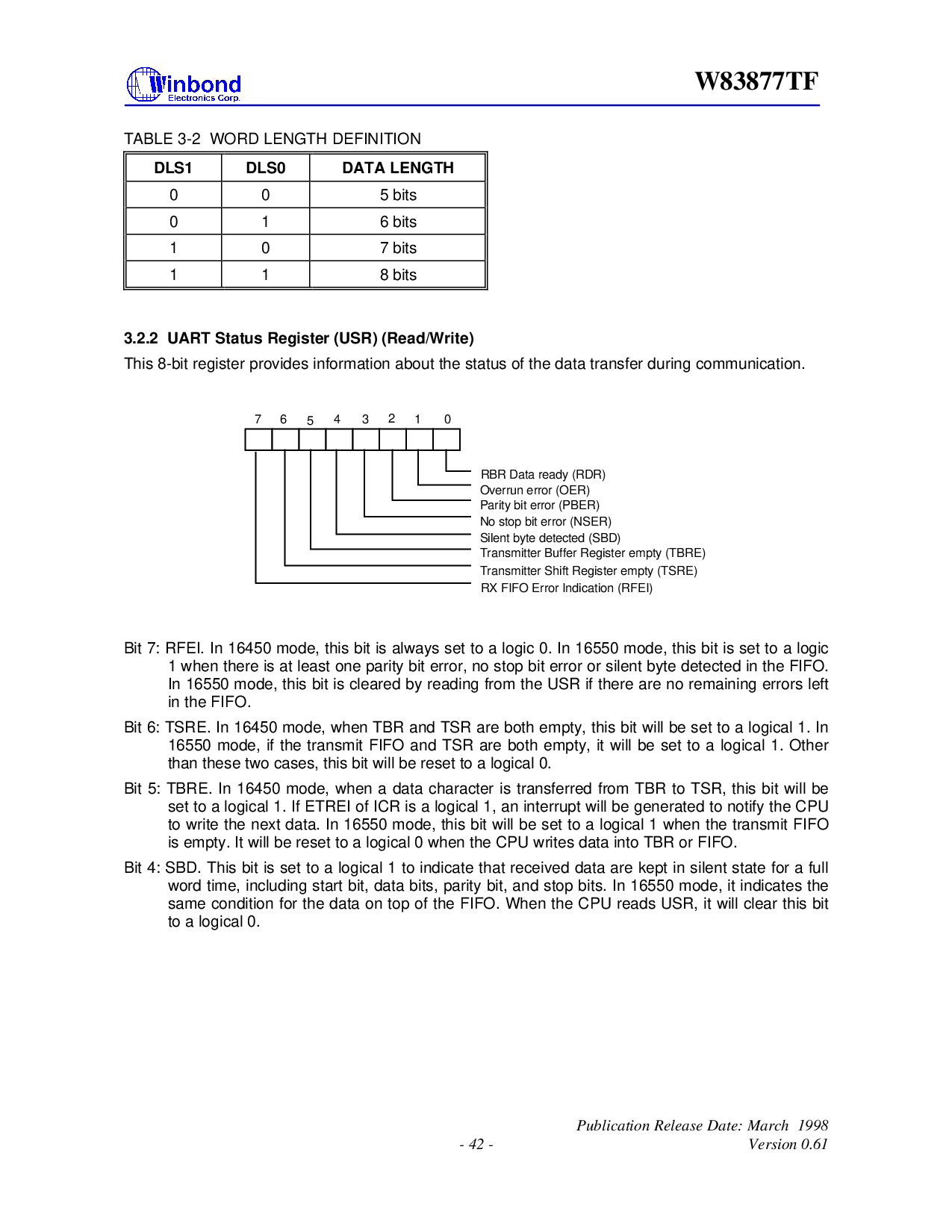

表格 3-2 文字 长度 定义

DLS1 DLS0 数据 长度

0 0 5 位

0 1 6 位

1 0 7 位

1 1 8 位

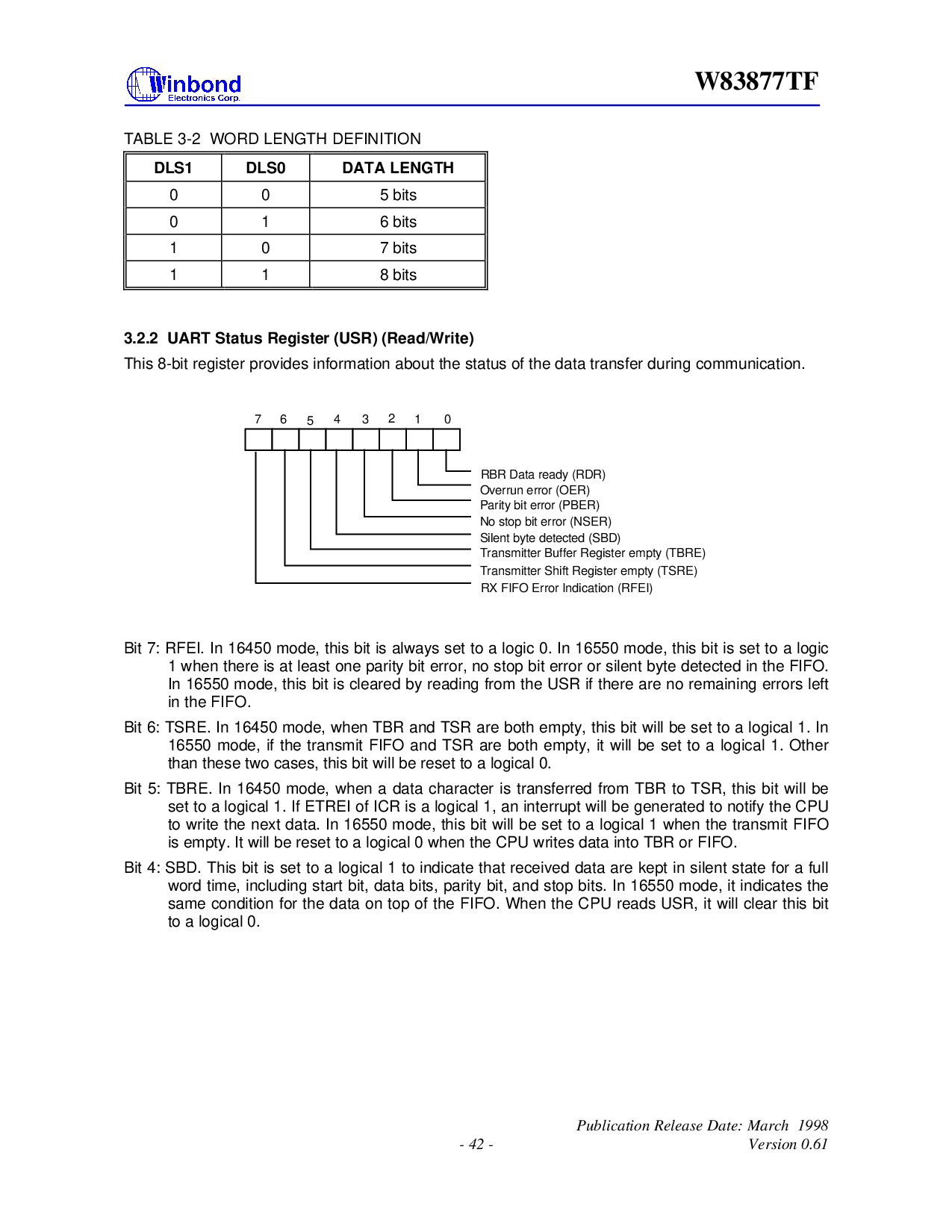

3.2.2 uart 状态 寄存器 (usr) (读/写)

这个 8-位 寄存器 提供 信息 关于 这 状态 的 这 数据 转移 在 交流.

1

2

34

5

67 0

rbr 数据 准备好 (rdr)

overrun 错误 (oer)

parity 位 错误 (pber)

非 停止 位 错误 (nser)

silent 字节 发现 (sbd)

传输者 缓存区 寄存器 empty (tbre)

传输者 变换 寄存器 empty (tsre)

rx 先进先出 错误 indication (rfei)

位 7: rfei. 在 16450 模式, 这个 位 是 总是 设置 至 一个 逻辑 0. 在 16550 mode, 这个 位 是 设置 至 一个 逻辑

1 当 那里 是 在 least 一个 parity 位 错误, 非 停止 位 错误 或者 silent 字节 发现 在 这 先进先出.

在 16550 模式, 这个 位 是 cleared 用 读 从 这 usr 如果 那里 是 非 remaining errors left

在 这 先进先出.

位 6: tsre. 在 16450 模式, 当 tbr 和 tsr 是 两个都 empty, 这个 位 将 是 设置 至 一个 logical 1. 在

16550 模式, 如果 这 transmit 先进先出 和 tsr 是 两个都 empty, 它 将 是 设置 至 一个 logical 1. 其它

比 这些 二 具体情况, 这个 位 将 是 重置 至 一个 logical 0.

位 5: tbre. 在 16450 模式, 当 一个 数据 character 是 transferred 从 tbr 至 tsr, 这个 位 将 是

设置 至 一个 logical 1. 如果 etrei 的 icr 是 一个 logical 1, 一个 中断 将 是 发生 至 notify 这 cpu

至 写 这 next 数据. 在 16550 模式, 这个 位 将 是 设置 至 一个 logical 1 当 这 transmit 先进先出

是 empty. 它 将 是 重置 至 一个 logical 0 当 这 cpu 写 数据 在 tbr 或者 先进先出.

位 4: sbd. 这个 位 是 设置 至 一个 logical 1 至 表明 那 received 数据 是 保持 在 silent 状态 为 一个 全部

文字 时间, 包含 开始 位, 数据 位, parity 位, 和 停止 bits. 在 16550 mode, 它 indicates 这

一样 情况 为 这 数据 在 顶 的 这 先进先出. 当 这 cpu 读 usr, 它 将 clear 这个 位

至 一个 logical 0.