9

所有 intersil 半导体 产品 是 制造的, 聚集 和 测试 下面

ISO9000

质量 系统 certification.

Intersil 半导体 产品 是 出售 用 描述 仅有的. Intersil 公司 reserves 这 正确的 至 制造 改变 在 电路 设计 和/或者 规格 在 任何 时间 和-

输出 注意. accordingly, 这 reader 是 cautioned 至 核实 那 数据 薄板 是 电流 在之前 放置 顺序. 信息 陈设 用 Intersil 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 Intersil 或者 它的 附属机构 为 它的 使用; 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部 这个 将 结果

从 它的 使用. 非 执照 是 准予 用 牵涉 或者 否则 下面 任何 专利权 或者 专利权 权利 的 intersil 或者 它的 附属机构.

为 信息 关于 Intersil 公司 和 它的 产品, 看 网 站点

www.intersil.com

销售 office 总部

北 america

intersil 公司

p. o. 盒 883, 邮递 停止 53-204

melbourne, fl 32902

电话: (407) 724-7000

传真: (407) 724-7240

欧洲

intersil sa

mercure 中心

100, rue de la fusee

1130 brussels, belgium

电话: (32) 2.724.2111

传真: (32) 2.724.22.05

ASIA

intersil (台湾) 有限公司.

7f-6, 非. 101 fu hsing 北 road

taipei, 台湾

republic 的 中国

电话: (886) 2 2716 9310

传真: (886) 2 2715 3029

HGTG20N60A4D

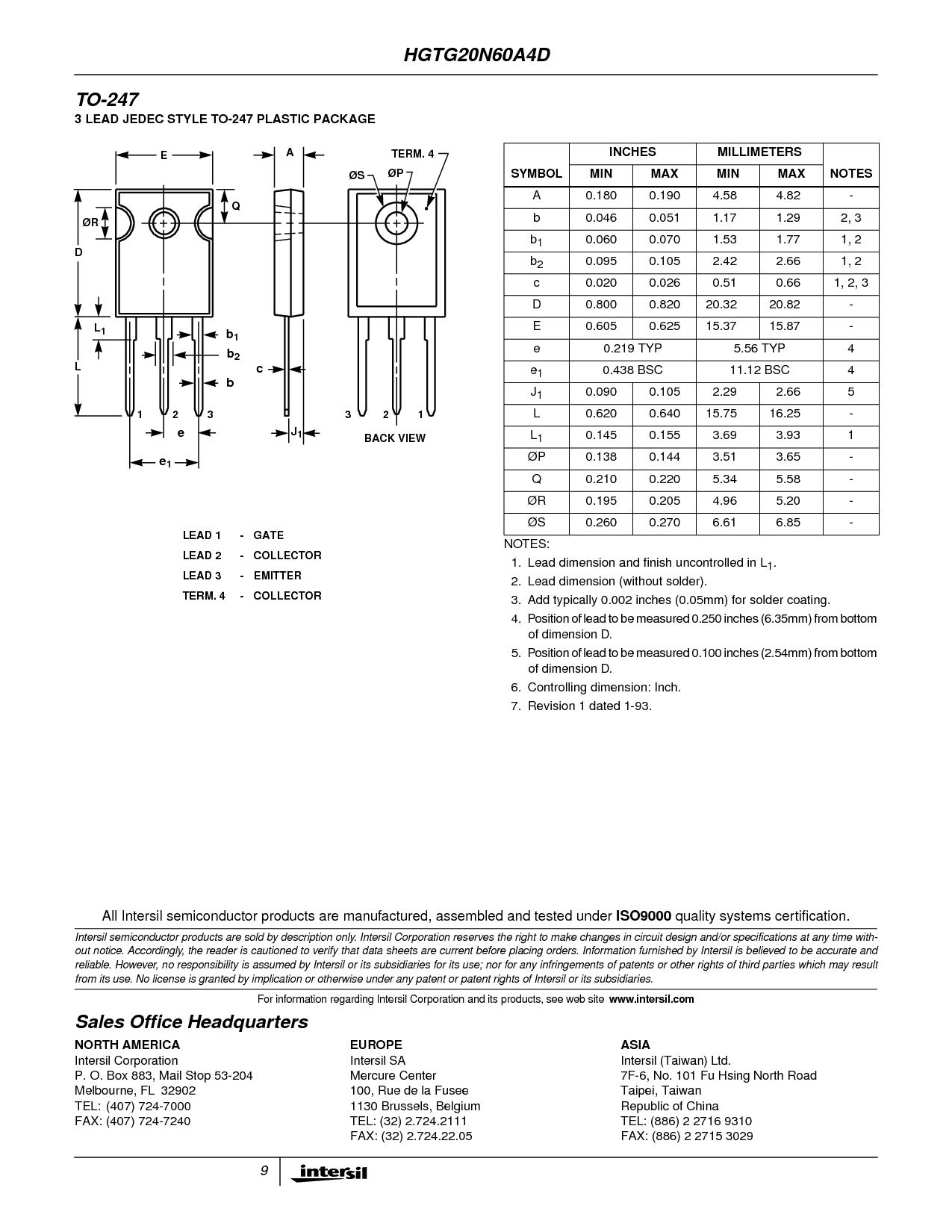

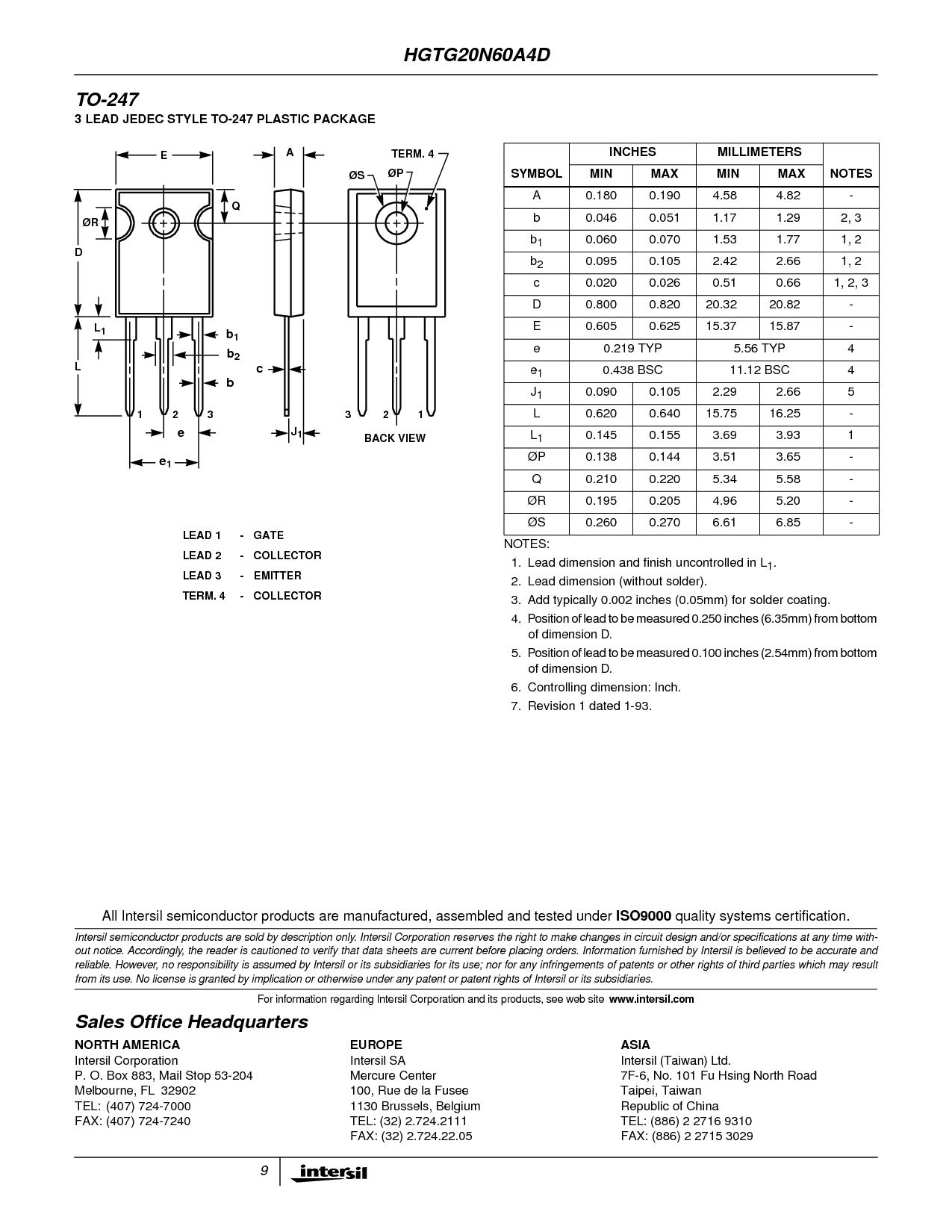

至-247

3 含铅的 电子元件工业联合会 样式 至-247 塑料 包装

igbt 包装 表格

含铅的 1 - 门

含铅的 2 - 集电级

含铅的 3 - 发射级

期. 4 - 集电级

一个

b

b

1

c

D

E

L

L

1

ØR

1

2

e

1

3

1

J

1

ØS

Q

ØP

后面的 视图

期. 4

3

e

b

2

2

标识

英寸 毫米

NOTESMIN 最大值 最小值 最大值

一个 0.180 0.190 4.58 4.82 -

b 0.046 0.051 1.17 1.29 2, 3

b

1

0.060 0.070 1.53 1.77 1, 2

b

2

0.095 0.105 2.42 2.66 1, 2

c 0.020 0.026 0.51 0.66 1, 2, 3

D 0.800 0.820 20.32 20.82 -

E 0.605 0.625 15.37 15.87 -

e 0.219 典型值 5.56 典型值 4

e

1

0.438 bsc 11.12 bsc 4

J

1

0.090 0.105 2.29 2.66 5

L 0.620 0.640 15.75 16.25 -

L

1

0.145 0.155 3.69 3.93 1

ØP 0.138 0.144 3.51 3.65 -

Q 0.210 0.220 5.34 5.58 -

ØR 0.195 0.205 4.96 5.20 -

ØS 0.260 0.270 6.61 6.85 -

注释:

1. 含铅的 维度 和 finish uncontrolled 在 l

1

.

2. 含铅的 维度 (没有 焊盘).

3. 增加 典型地 0.002 英寸 (0.05mm) 为 焊盘 coating.

4. 位置 的 含铅的 至 是 量过的 0.250 英寸 (6.35mm) 从 bottom

的 维度 d.

5. 位置 的 含铅的 至 是 量过的 0.100 英寸 (2.54mm) 从 bottom

的 维度 d.

6. controlling 维度: inch.

7. 修订 1 dated 1-93.