3

idt72v263/273/283/293/103/113 3.3v 高 密度supersync ii

TM

narrow 总线 先进先出

8k x 18, 16k x 9/18, 32k x 9/18, 64k x 9/18, 128k x 9/18, 256k x 9/18, 512k x9

商业的 和 工业的

温度 范围

idt72v223/233/243/253/263/273/283/293 3.3v 高 密度 supersync ii

TM

narrow 总线 先进先出

512 x 18, 1k x 9/18, 2k x 9/18, 4k x 9/18, 8k x 9/18, 16k x 9/18, 32k x 9/18, 64k x 9/18, 128k x 9

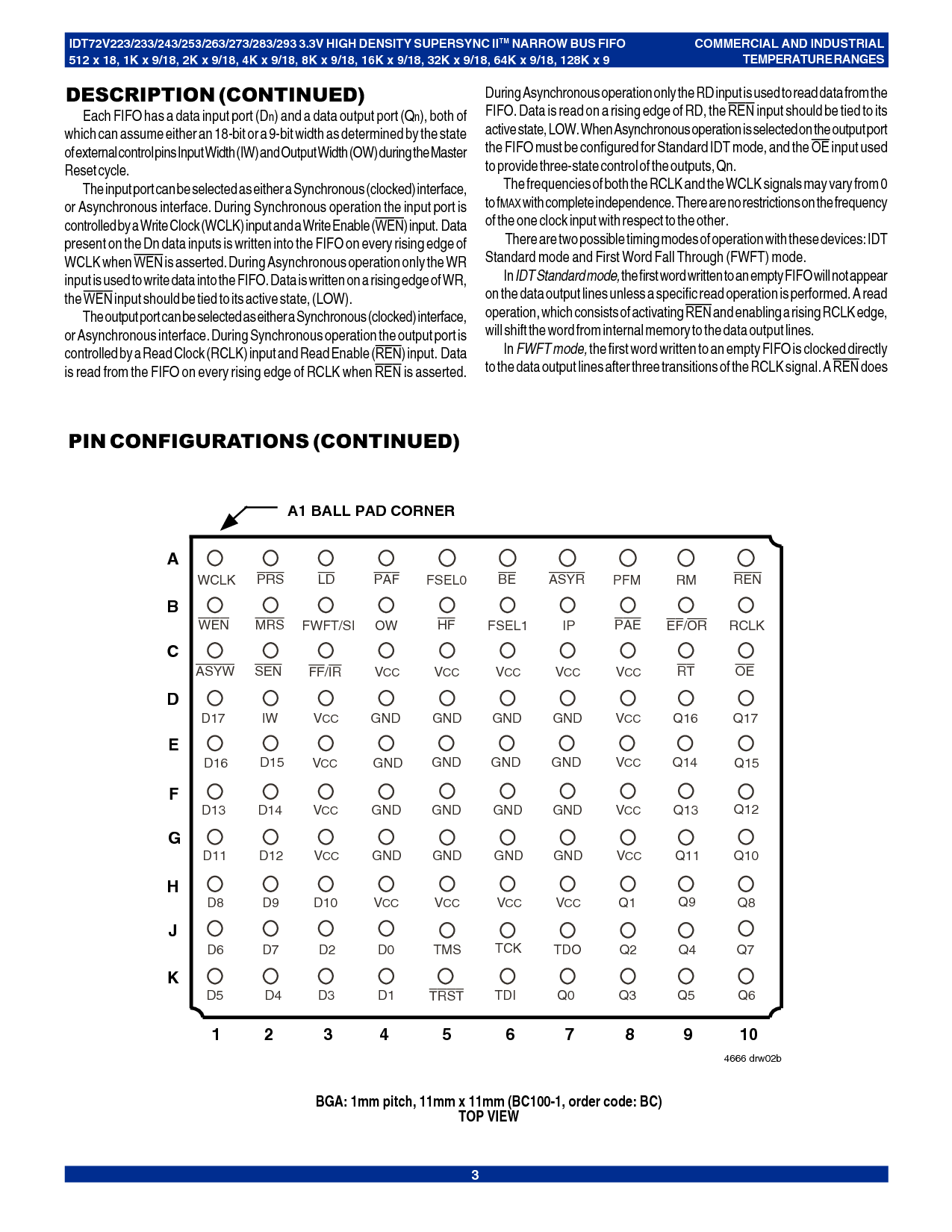

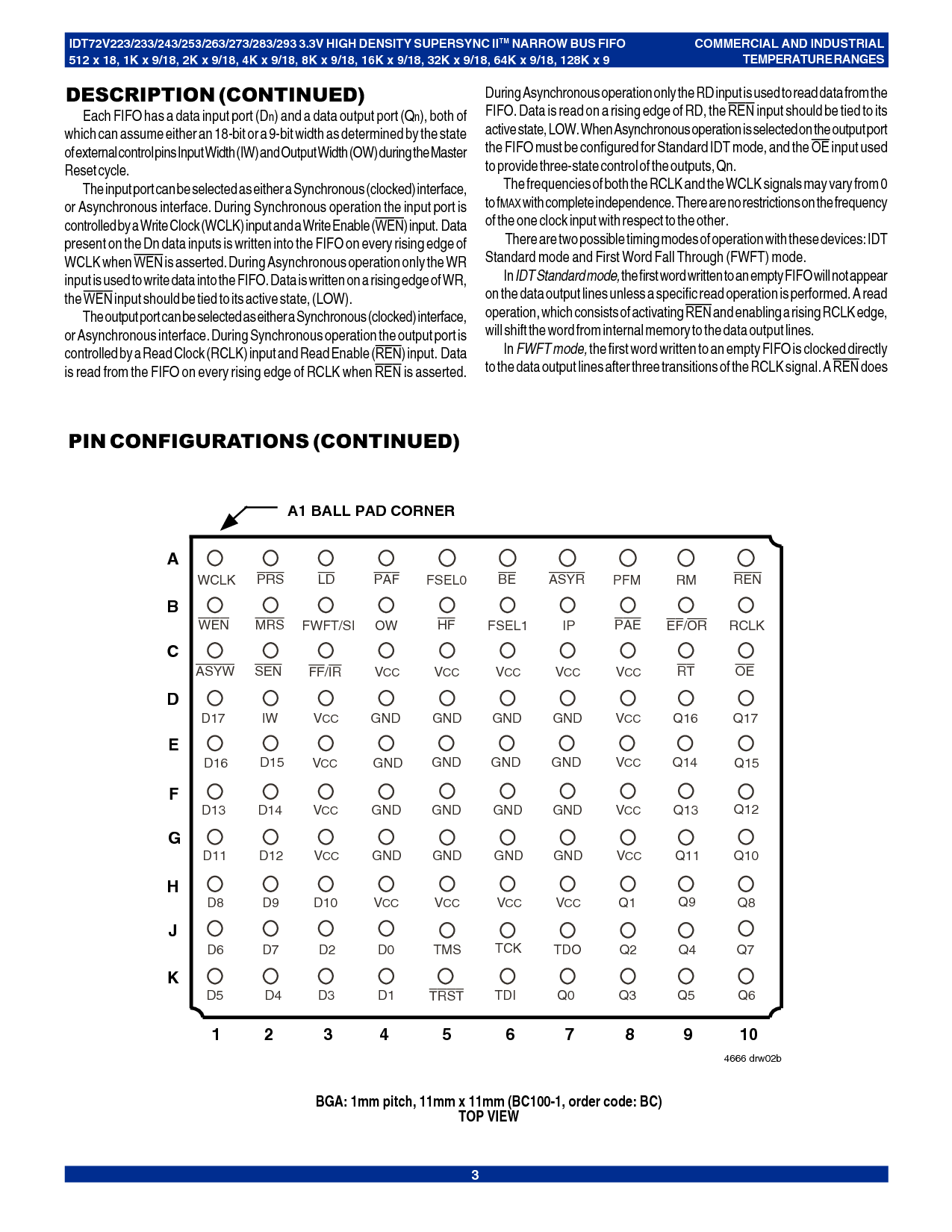

管脚 配置 (持续)

bga: 1mm 程度, 11mm x 11mm (bc100-1, 顺序 代号: bc)

顶 视图

各自 先进先出 有 一个 数据 输入 端口 (d

n

) 和 一个 数据 输出 端口 (q

n

), 两个都 的

这个 能 假设 也 一个 18-位 或者 一个 9-位 宽度 作 决定 用 这 状态

的 外部 控制 管脚 输入 宽度 (iw) 和 输出 宽度 (ow) 在 这 主控

重置 循环.

这 输入 端口 能 是 选择 作 也 一个 同步的 (clocked) 接口,

或者 异步的 接口. 在 同步的 运作 这 输入 端口 是

控制 用 一个 写 时钟 (wclk) 输入 和 一个 写 使能 (

WEN

) 输入. 数据

呈现 在 这 dn 数据 输入 是 写 在 这 先进先出 在 每 rising 边缘 的

wclk 当

WEN

是 asserted. 在 异步的 运作 仅有的 这 wr

输入 是 使用 至 写 数据 在 这 先进先出. 数据 是 写 在 一个 rising 边缘 的 wr,

这

WEN

输入 应当 是 系 至 它的 起作用的 状态, (低).

这 输出 端口 能 是 选择 作 也 一个 同步的 (clocked) 接口,

或者 异步的 接口. 在 同步的 运作 这 输出 端口 是

控制 用 一个 读 时钟 (rclk) 输入 和 读 使能 (

REN

) 输入. 数据

是 读 从 这 先进先出 在 每 rising 边缘 的 rclk 当

REN

是 asserted.

在 异步的 运作 仅有的 这 rd 输入 是 使用 至 读 数据 从 这

先进先出. 数据 是 读 在 一个 rising 边缘 的 rd, 这

REN

输入 应当 是 系 至 它的

起作用的 状态, 低. 当 异步的 运作 是 选择 在 这 输出 端口

这 先进先出 必须 是 配置 为 标准 idt 模式, 和 这

OE

输入 使用

至 提供 三-状态 控制 的 这 输出, qn.

这 发生率 的 两个都 这 rclk 和 这 wclk 信号 将 相异 从 0

至 f

最大值

和 完全 independence. 那里 是 非 restrictions 在 这 频率

的 这 一个 时钟 输入 和 遵守 至 这 其它.

那里 是 二 可能 定时 模式 的 运作 和 这些 设备: idt

标准 模式 和 第一 文字 下降 通过 (fwft) 模式.

在

idt 标准 模式,

这 第一 文字 写 至 一个 empty 先进先出 将 不 呈现

在 这 数据 输出 线条 除非 一个 明确的 读 运作 是 执行. 一个 读

运作, 这个 组成 的 activating

REN

和 enabling 一个 rising rclk 边缘,

将 变换 这 文字 从 内部的 记忆 至 这 数据 输出 线条.

在

fwft 模式,

这 第一 文字 写 至 一个 empty 先进先出 是 clocked 直接地

至 这 数据 输出 线条 之后 三 transitions 的 这 rclk 信号. 一个

REN

做

描述 (持续)

ASYW

WEN

WCLK

PAF

FF

/

IR

是 ASYR

PFM RM

REN

SEN

MRS

PRS LD

HF

FSEL0

IP

PAE

EF

/

或者

rclkfwft/si OW

V

CC

V

CC

V

CC

RT OE

D17 IW V

CC

地 地 地 地 V

CC

Q16 Q17

D16

D13

V

CC

地 Q15

D15

D14 V

CC

地

Q12

D11 D12 V

CC

地 Q10

D8 D9 D10 V

CC

Q8

D6 D7 D2 D0 Q7

D5 D4 D3 D1

TRST

TDI Q0 Q3 Q5

Q6

a1 球 垫子 corner

一个

B

C

D

E

F

G

H

J

K

12 3 4 5 6 7 8 9 10

4666 drw02b

地 地 地 V

CC

Q14

地 地 地 V

CC

Q13

Q9

地 地 地 V

CC

Q11

TMS

TCK

TDO Q2 Q4

V

CC

V

CC

V

CC

Q1

V

CC

V

CC

FSEL1