®

pcm1760p/u df1760p/u

8

功能 的

这 数字的 过滤

系统 时钟

这 df1760 能 接受 一个 系统 时钟 的 也 256fs 或者

384fs. 如果 一个 384fs 系统 时钟 是 使用, 这 df1760 divides

用 2/3 至 create 这 256fs 系统 时钟 必需的 为 这

pcm1760. 这 系统 时钟 是 应用 至 管脚 15 (sysclk

输入). 这 真实的 时钟 选择 是 完毕 用 设置 管脚 25

(clksel 输入) “high” 为 256fs 时钟 和 “low” 为

384fs 时钟.

这 详细地 定时 (所需的)东西 为 这 系统 时钟 是

显示 在 图示 3c.

CLKSEL SYSCLK

H 256fs

L 384fs

主控/从动装置 模式

这 df1760 能 是 使用 在 两个都 这 主控 模式 和 从动装置

模式. 在 这 主控 模式, 这 df1760 输出 l/r (left/

正确的 频道 阶段 时钟), sclk (数据 时钟) 和 fsync

(框架 时钟 2fs) 信号. 在 这 从动装置 模式, 这 df1760

accepts l/r, sclk 和 fsync 信号. 这 模式 选择

是 完毕 用 带去 管脚 24 (s/m 输入) “high” 为 从动装置

模式 和 “low” 为 主控 模式.

s/m 模式

H 从动装置

L 主控

输出 数据 format

这 串行 输出 数据 有 四 可能 formats. 这 selec-

tion 的 这 formats 能 是 完毕 用 这 模式 1 和 模式 2

输入.

CALD 校准

H 使不能运转

L 使能

模式 1 模式 2 FORMATS

H H msb 第一, 16 位, 下落 边缘

L H msb 第一, 20 位, 下落 边缘

H L msb 第一, 20 位, rising 边缘

L L lsb 第一, 20 位, 下落 边缘

LRSC l/r 时钟 和 频道

H h = lch, l = rch

L l = lch, h = rch

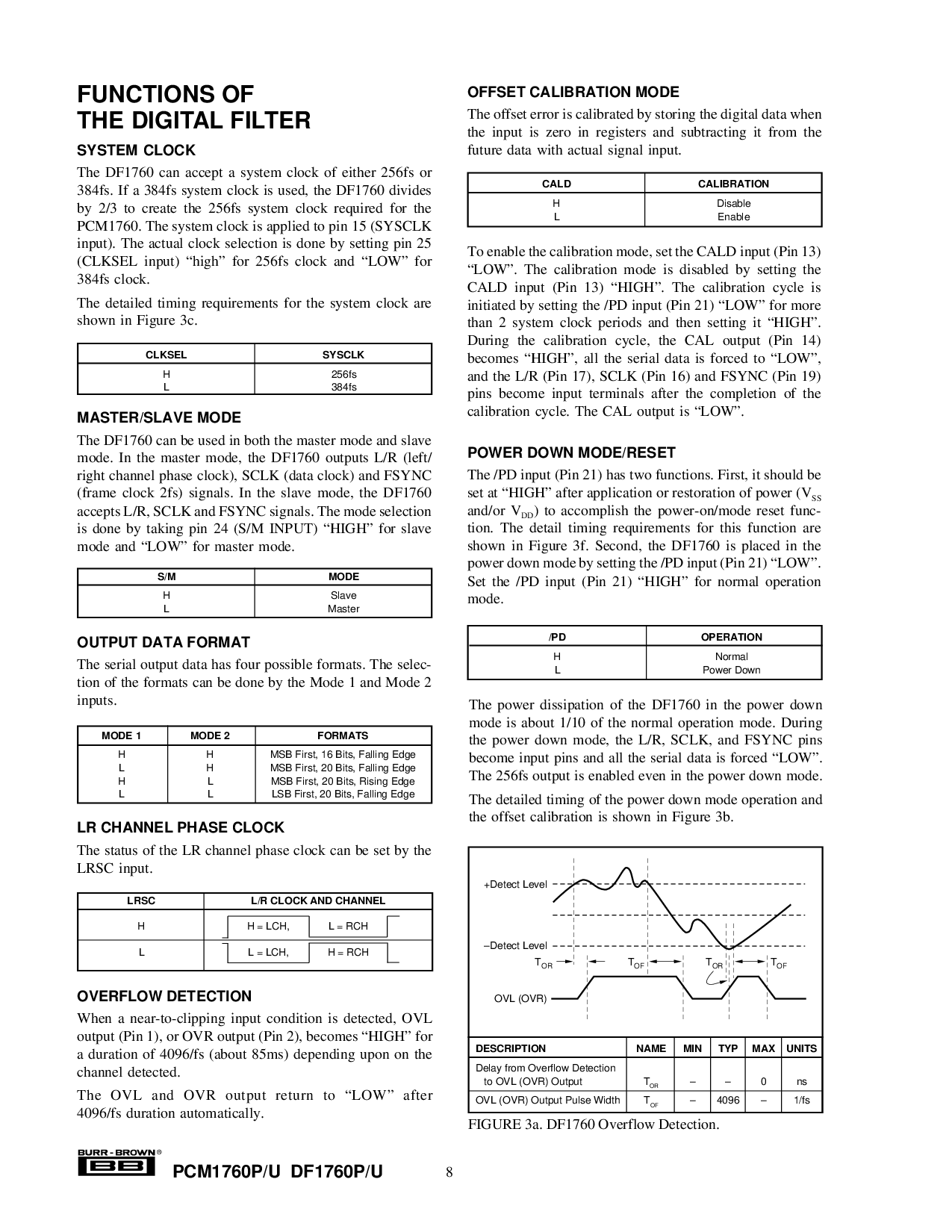

overflow 发现

当 一个 near-至-修剪 输入 情况 是 发现, ovl

输出 (管脚 1), 或者 ovr 输出 (管脚 2), 变为 “high” 为

一个 持续时间 的 4096/fs (关于 85ms) 取决于 在之上 在 这

频道 发现.

这 ovl 和 ovr 输出 返回 至 “low” 之后

4096/fs 持续时间 automatically.

补偿 校准 模式

这 补偿 错误 是 校准 用 storing 这 数字的 数据 当

这 输入 是 零 在 寄存器 和 subtracting 它 从 这

future 数据 和 真实的 信号 输入.

至 使能 这 校准 模式, 设置 这 cald 输入 (管脚 13)

“low”. 这 校准 模式 是 无能 用 设置 这

cald 输入 (管脚 13) “high”. 这 校准 循环 是

initiated 用 设置 这 /pd 输入 (管脚 21) “low” 为 更多

比 2 系统 时钟 时期 和 然后 设置 它 “high”.

在 这 校准 循环, 这 cal 输出 (管脚 14)

变为 “high”, 所有 这 串行 数据 是 强迫 至 “low”,

和 这 l/r (管脚 17), sclk (管脚 16) 和 fsync (pin 19)

管脚 变为 输入 terminals 之后 这 completion 的 这

校准 循环. 这 cal 输出 是 “low”.

电源 向下 模式/重置

这 /pd 输入 (管脚 21) 有 二 功能. first, 它 应当 是

设置 在 “high” 之后 应用 或者 restoration 的 电源 (v

SS

和/或者 v

DD

) 至 accomplish 这 电源-在/模式 重置 func-

tion. 这 detail 定时 (所需的)东西 为 这个 函数 是

显示 在 图示 3f. 第二, 这 df1760 是 放置 在 这

电源 向下 模式 用 设置 这 /pd 输入 (管脚 21) “low”.

设置 这 /pd 输入 (管脚 21) “high” 为 正常的 运作

模式.

lr 频道 阶段 时钟

这 状态 的 这 lr 频道 阶段 时钟 能 是 设置 用 这

lrsc 输入.

/pd 运作

H 正常的

L 电源 向下

描述 名字 最小值 典型值 最大值 单位

延迟 从 overflow 发现

至 ovl (ovr) 输出 T

或者

––0ns

ovl (ovr) 输出 脉冲波 宽度 T

的

– 4096 – 1/fs

图示 3a. df1760 overflow 发现.

T

OF

T

OR

T

OF

T

OR

ovl (ovr)

–detect level

+detect level

这 电源 消耗 的 这 df1760 在 这 电源 向下

模式 是 关于 1/10 的 这 正常的 运作 模式. 在

这 电源 向下 模式, 这 l/r, sclk, 和 fsync 管脚

变为 输入 管脚 和 所有 这 串行 数据 是 强迫 “low”.

这 256fs 输出 是 使能 甚至 在 这 电源 向下 模式.

这 详细地 定时 的 这 电源 向下 模式 运作 和

这 补偿 校准 是 显示 在 图示 3b.