rev. b–2–

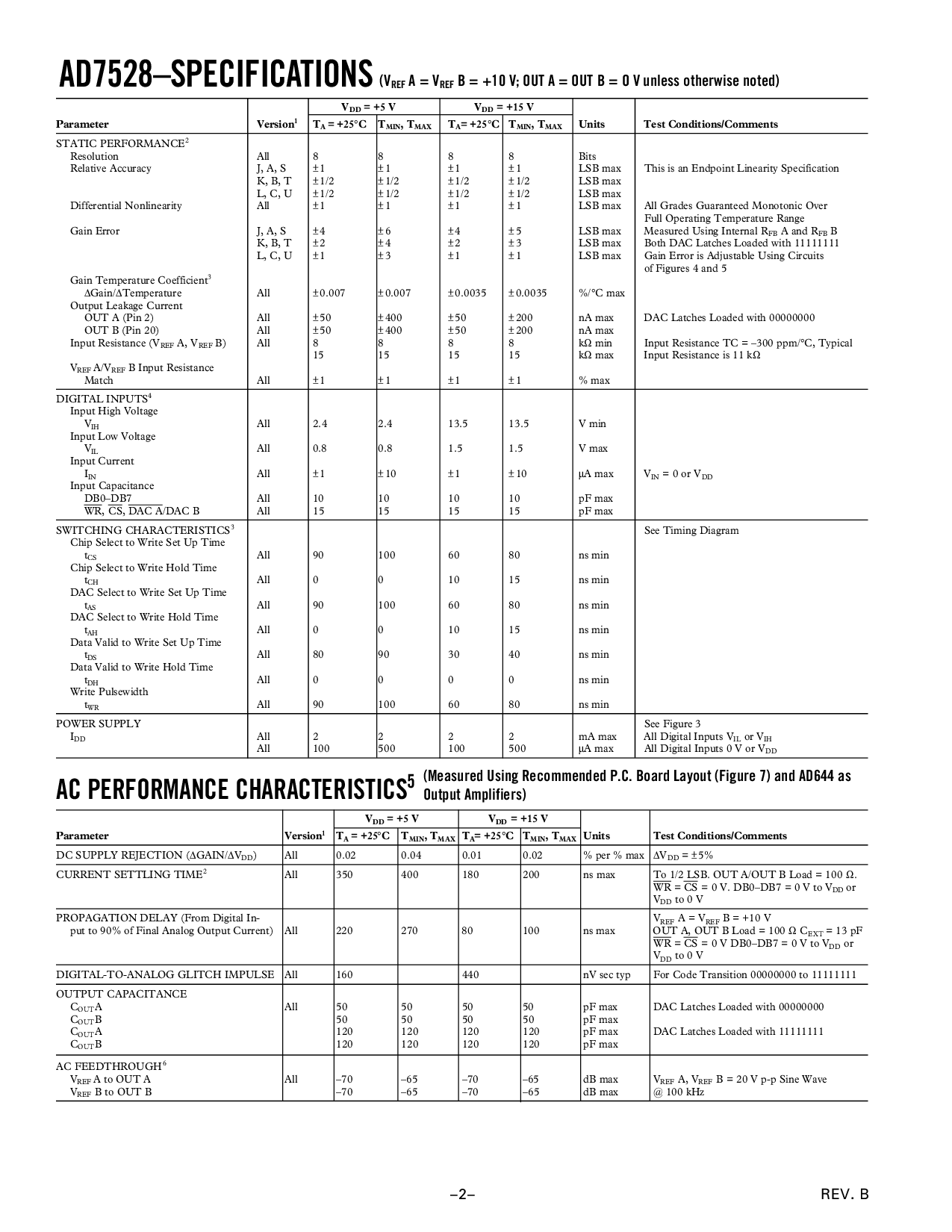

AD7528–SPECIFICATIONS

(v

REF

一个 = v

REF

b = +10 v; 输出 一个 = 输出 b = o v 除非 否则 指出)

V

DD

= +5 v V

DD

= +15 v

参数 版本

1

T

一个

= +25

°

CT

最小值

, t

最大值

T

一个

= +25

°

CT

最小值

, t

最大值

单位 测试 情况/comments

静态的 效能

2

决议 所有 8 8 8 8 位

相关的 精度 j, 一个, s

±

1

±

1

±

1

±

1 lsb 最大值 这个 是 一个 endpoint 线性 规格

k, b, t

±

1/2

±

1/2

±

1/2

±

1/2 lsb 最大值

l, c, u

±

1/2

±

1/2

±

1/2

±

1/2 lsb 最大值

差别的 非线性 所有

±

1

±

1

±

1

±

1 lsb 最大值 所有 grades 有保证的 monotonic 在

全部 运行 温度 范围

增益 错误 j, 一个, s

±

4

±

6

±

4

±

5 lsb 最大值 量过的 使用 内部的 r

FB

一个 和 r

FB

B

k, b, t

±

2

±

4

±

2

±

3 lsb 最大值 两个都 dac latches 承载 和 11111111

l, c, u

±

1

±

3

±

1

±

1 lsb 最大值 增益 错误 是 可调整的 使用 电路

的 计算数量 4 和 5

增益 温度 系数

3

∆

增益/

∆

温度 所有

±

0.007

±

0.007

±

0.0035

±

0.0035 %/

°

c 最大值

输出 泄漏 电流

输出 一个 (管脚 2) 所有

±

50

±

400

±

50

±

200 na 最大值 dac latches 承载 和 00000000

输出 b (管脚 20) 所有

±

50

±

400

±

50

±

200 na 最大值

输入 阻抗 (v

REF

一个, v

REF

b) 所有 8 8 8 8 k

Ω

最小值 输入 阻抗 tc = –300 ppm/

°

c, 典型

15 15 15 15 k

Ω

最大值 输入 阻抗 是 11 k

Ω

V

REF

一个/v

REF

b 输入 阻抗

相一致 所有

±

1

±

1

±

1

±

1% 最大值

数字的 输入

4

输入 高 电压

V

IH

所有 2.4 2.4 13.5 13.5 v 最小值

输入 低 电压

V

IL

所有 0.8 0.8 1.5 1.5 v 最大值

输入 电流

I

在

所有

±

1

±

10

±

1

±

10

µ

一个 最大值 V

在

= 0 或者 v

DD

输入 电容

DB0–DB7 所有 10 10 10 10 pf 最大值

WR

,

CS

,

dac 一个

/dac b 所有 15 15 15 15 pf 最大值

切换 特性

3

看 定时 图解

碎片 选择 至 写 设置 向上 时间

t

CS

所有 90 100 60 80 ns 最小值

碎片 选择 至 写 支撑 时间

t

CH

所有 0 0 10 15 ns 最小值

dac 选择 至 写 设置 向上 时间

t

作

所有 90 100 60 80 ns 最小值

dac 选择 至 写 支撑 时间

t

AH

所有 0 0 10 15 ns 最小值

数据 有效的 至 写 设置 向上 时间

t

DS

所有 80 90 30 40 ns 最小值

数据 有效的 至 写 支撑 时间

t

DH

所有 0 0 0 0 ns 最小值

写 pulsewidth

t

WR

所有 90 100 60 80 ns 最小值

电源 供应 看 图示 3

I

DD

所有 2 2 2 2 毫安 最大值 所有 数字的 输入 v

IL

或者 v

IH

所有 100 500 100 500

µ

一个 最大值 所有 数字的 输入 0 v 或者 v

DD

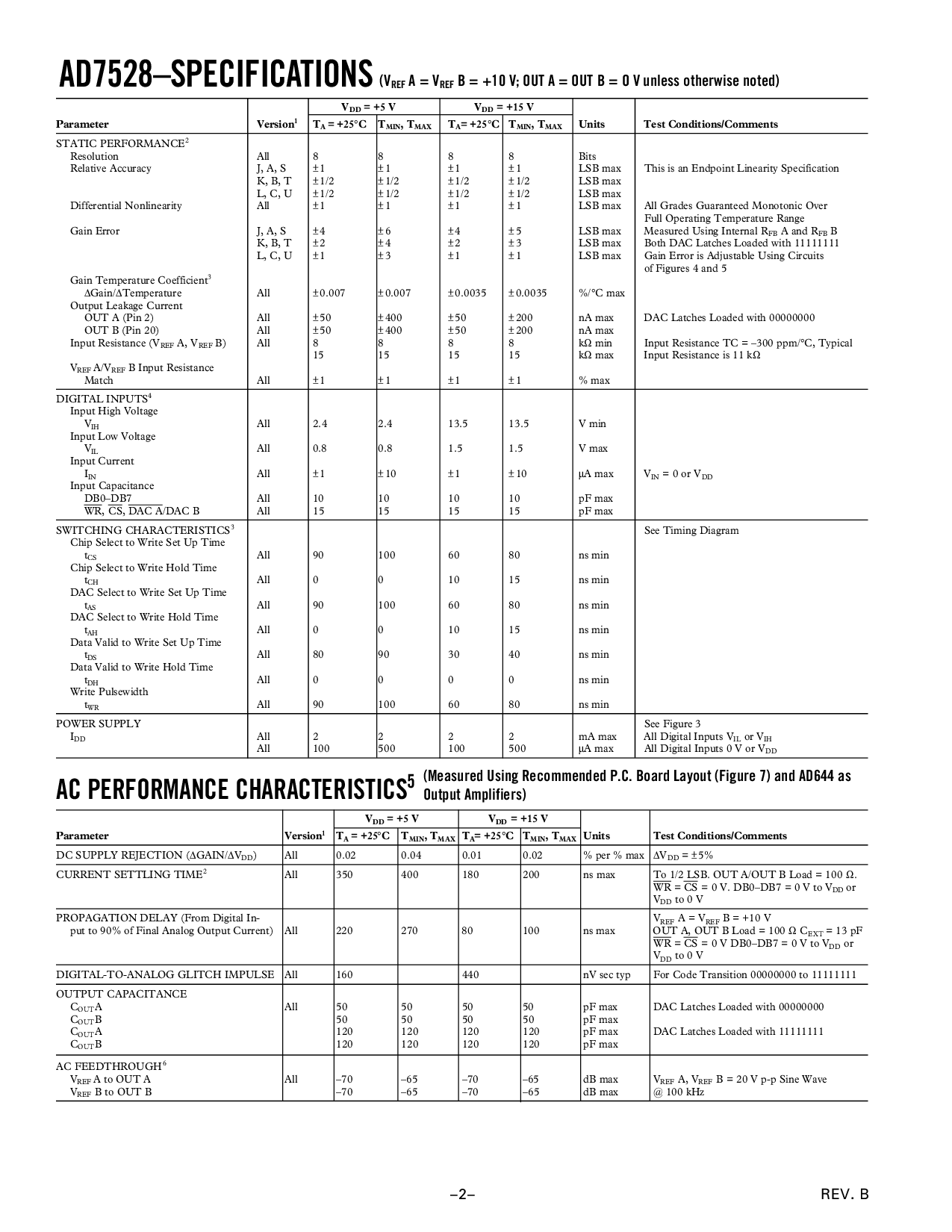

交流 效能 特性

5

V

DD

= +5 v V

DD

= +15 v

参数 版本

1

T

一个

= +25

°

CT

最小值

, t

最大值

T

一个

= +25

°

CT

最小值

, t

最大值

单位 测试 情况/comments

直流 供应 拒绝 (

∆

增益/

∆

V

DD

) 所有 0.02 0.04 0.01 0.02 % 每 % 最大值

∆

V

DD

=

±

5%

电流 安排好 时间

2

所有 350 400 180 200 ns 最大值 至 1/2 lsb. 输出 一个/输出 b 加载 = 100

Ω

.

WR

=

CS

= 0 v. db0–db7 = 0 v 至 v

DD

或者

V

DD

至 0 v

传播 延迟 (从 数字的 在- V

REF

一个 = v

REF

b = +10 v

放 至 90% 的 最终 相似物 输出 电流) 所有 220 270 80 100 ns 最大值 输出 一个, 输出 b 加载 = 100

Ω

C

EXT

= 13 pf

WR

=

CS

= 0 v db0–db7 = 0 v 至 v

DD

或者

V

DD

至 0 v

数字的-至-相似物 glitch impulse 所有 160 440 nv 秒 典型值 为 代号 转变 00000000 至 11111111

输出 电容

C

输出

一个 所有 50 50 50 50 pf 最大值 dac latches 承载 和 00000000

C

输出

B 50 505050pf 最大值

C

输出

一个 120 120 120 120 pf 最大值 dac latches 承载 和 11111111

C

输出

B 120 120 120 120 pf 最大值

交流 feedthrough

6

V

REF

一个 至 输出 一个 所有 –70 –65 –70 –65 db 最大值 V

REF

一个, v

REF

b = 20 v p-p sine 波

V

REF

b 至 输出 b –70 –65 –70 –65 db 最大值 @ 100 khz

(量过的 使用 推荐 p.c. 板 布局 (图示 7) 和 ad644 作

输出 放大器)