ADS8324

9

SBAS172A

www.德州仪器.com

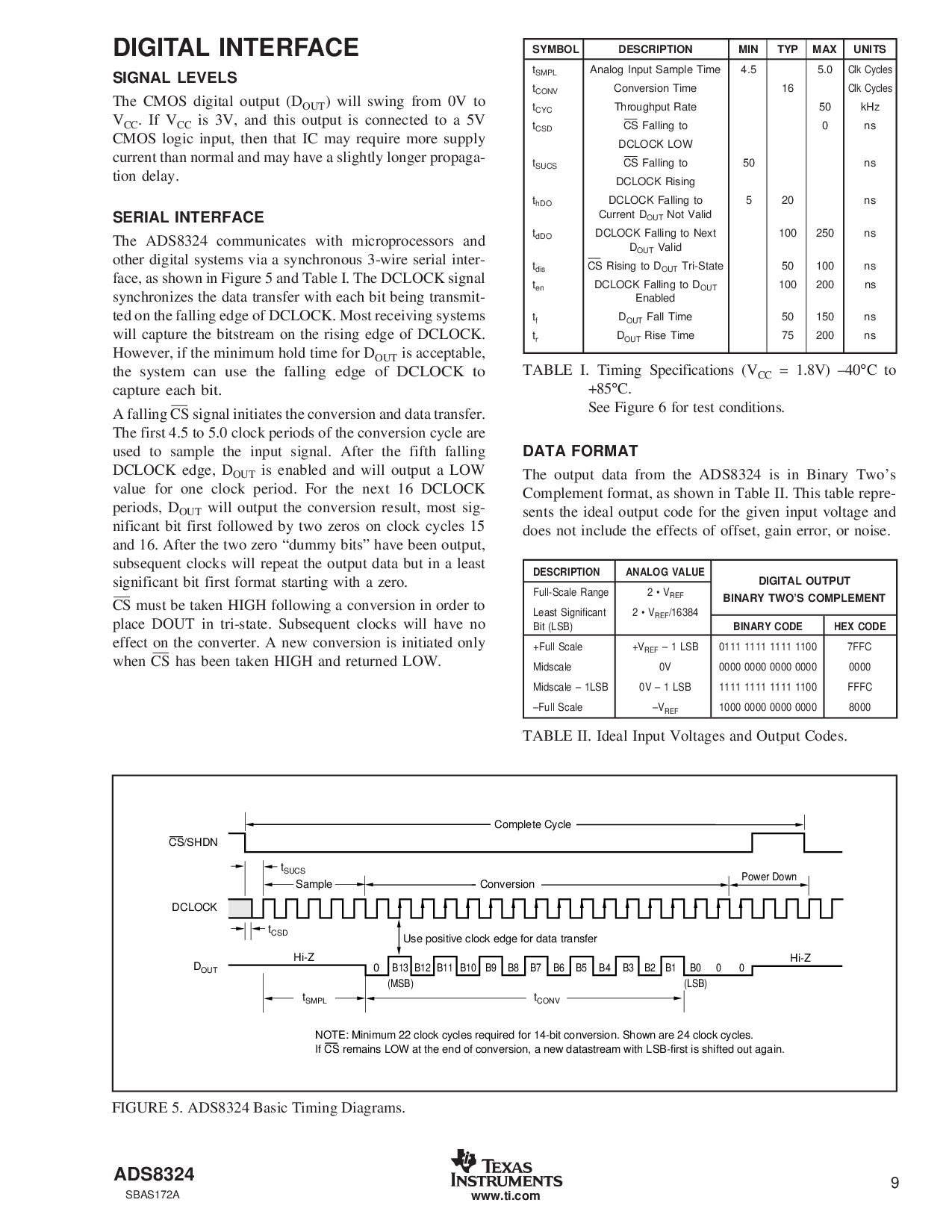

标识 描述 最小值 典型值 最大值 单位

t

SMPL

相似物 输入 样本 时间 4.5 5.0

clk 循环

t

CONV

转换 时间 16

clk 循环

t

CYC

throughput 比率 50 kHz

t

CSD

cs 下落 至 0 ns

dclock 低

t

SUCS

cs 下落 至 50 ns

dclock rising

t

hDO

dclock 下落 至 5 20 ns

电流 d

输出

不 有效的

t

dDO

dclock 下落 至 next 100 250 ns

D

输出

有效的

t

dis

cs rising 至 d

输出

触发-状态 50 100 ns

t

en

dclock 下落 至 d

输出

100 200 ns

使能

t

f

D

输出

下降 时间 50 150 ns

t

r

D

输出

上升 时间 75 200 ns

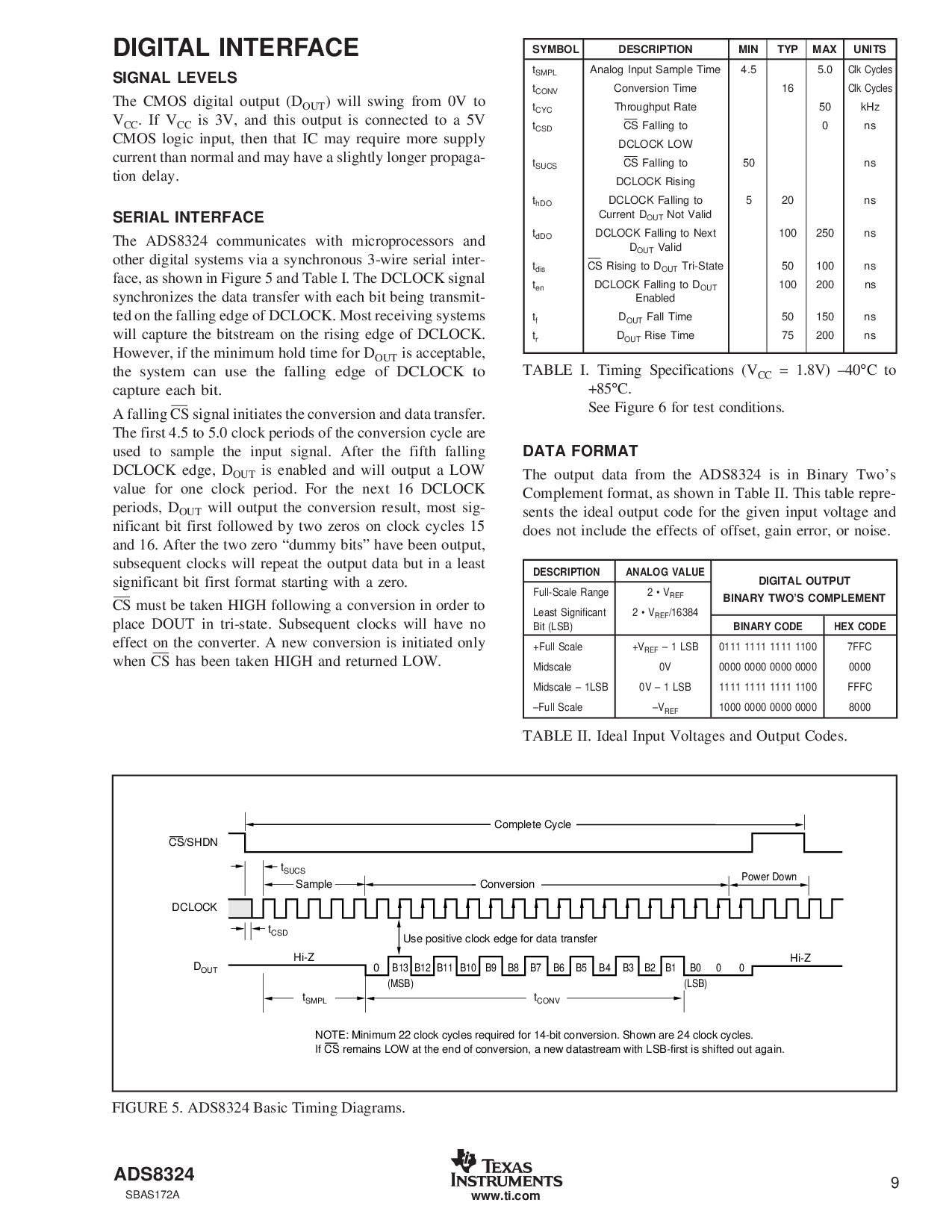

图示 5. ads8324 基本 定时 图解.

数字的 接口

信号 水平

这 cmos 数字的 输出 (d

输出

) 将 摆动 从 0v 至

V

CC

. 如果 v

CC

是 3v, 和 这个 输出 是 连接 至 一个 5v

cmos 逻辑 输入, 然后 那 ic 将 需要 更多 供应

电流 比 正常的 和 将 有 一个 slightly 变长 propaga-

tion 延迟.

串行 接口

这 ads8324 communicates 和 微处理器 和

其它 数字的 系统 通过 一个 同步的 3-线 串行 inter-

面向, 作 显示 在 图示 5 和 表格 i. 这 dclock 信号

synchronizes 这 数据 转移 和 各自 位 正在 transmit-

ted 在 这 下落 边缘 的 dclock. 大多数 接到 系统

将 俘获 这 bitstream 在 这 rising 边缘 的 dclock.

不管怎样, 如果 这 最小 支撑 时间 为 d

输出

是 可接受的,

这

系统 能 使用 这 下落 边缘 的 dclock 至

俘获 各自 位.

一个 下落 cs 信号 initiates 这 转换 和 数据 转移.

这 第一 4.5 至 5.0 时钟 时期 的 这 转换 循环 是

使用 至 样本 这 输入 信号. 之后 这 fifth 下落

dclock 边缘, d

输出

是 使能 和 将 输出 一个 低

值 为 一个 时钟 时期. 为 这 next 16 dclock

时期, d

输出

将 输出 这 转换 结果, 大多数 sig-

nificant 位 第一 followed 用 二 zeros 在 时钟 循环 15

和 16. 之后 这 二 零 “dummy bits” 有 被 输出,

subsequent clocks 将 repeat 这 输出 数据 但是 在 一个 least

重大的 位 第一 format 开始 和 一个 零.

cs 必须 是 带去 高 下列的 一个 转换 在 顺序 至

放置 dout 在 触发-状态. subsequent clocks 将 有 非

效应 在 这 转换器. 一个 新 转换 是 initiated 仅有的

当 cs 有 被 带去 高 和 returned 低.

数据 format

这 输出 数据 从 这 ads8324 是 在 二进制的 二’s

complement format, 作 显示 在 表格 ii. 这个 表格 repre-

sents 这 完美的 输出 代号 为 这 给 输入 电压 和

做 不 包含 这 影响 的 补偿, 增益 错误, 或者 噪音.

表格 i. 定时规格 (v

CC

= 1.8v) –40

°

c 至

+85

°

c.

看 图示 6 为 测试 情况.

cs/shdn

D

输出

DCLOCK

完全 循环

电源 向下

ConversionSample

使用 积极的 时钟 边缘 为 数据 转移

t

SUCS

t

CONV

t

SMPL

便条: 最小 22 时钟 循环 必需的 为 14-位 转换. 显示 是 24 时钟 循环.

如果 cs 仍然是 低 在 这 终止 的 转换, 一个 新 datastream 和 lsb-第一 是 shifted 输出 又一次.

B13

(msb)

B12 B11 B10 B9 B8 B7 B6 B0

(lsb)

00B5 B4 B3 B1B2

hi-z

0

hi-z

t

CSD

描述 相似物 值

全部-规模 范围 2

•

V

REF

least 重大的 2

•

V

REF

/16384

位 (lsb)

二进制的 代号 十六进制 代号

+full 规模 +V

REF

–

1 lsb 0111 1111 1111 1100 7FFC

Midscale 0V 0000 0000 0000 0000 0000

Midscale

–

1LSB 0V

–

1 lsb 1111 1111 1111 1100 FFFC

–

全部 规模

–

V

REF

1000 0000 0000 0000 8000

数字的 输出

二进制的 二

’

s complement

表格 ii. 完美的 输入 电压 和 输出 代号.