adsp-21xx

–8–

rev. b

一个 时钟 输出 信号 (clkout) 是 发生 用 这 处理器,

同步 至 这 处理器’s 内部的 循环.

重置

这 重置

信号 initiates 一个 完全 重置 的 这 adsp-21xx.

这

重置

信号 必须 是 asserted 当 这 碎片 是 powered

向上 至 使确信 恰当的 initialization. 如果 这

重置

信号 是 应用

在 最初的 电源-向上, 它 必须 是 使保持 长 足够的 至 准许

这 处理器’s 内部的 时钟 至 stabilize. 如果

重置

是 使活动

在 任何 时间 之后 电源-向上 和 这 输入 时钟 频率 做

不 改变, 这 处理器’s 内部的 时钟 持续 和 做

不 需要 这个 stabilization 时间.

这 电源-向上 sequence 是 定义 作 这 总的 时间 必需的 为

这 结晶 振荡器 电路 至 stabilize 之后 一个 有效的 v

DD

是

应用 至 这 处理器 和 为 这 内部的 阶段-锁 循环

(pll) 至 锁 面向 这 明确的 结晶 频率. 一个 最小 的

2000 t

CK

循环 将 确保 那 这 pll 有 锁 (这个 做

不, 不管怎样, 包含 这 结晶 振荡器 开始-向上 时间).

在 这个 电源-向上 sequence 这

重置

信号 应当 是

使保持 低. 在 任何 subsequent resets, 这

重置

信号 必须

满足 这 最小 脉冲波 宽度 规格, t

RSP

.

至 发生 这

重置

信号, 使用 也 一个 rc 电路 和 一个

外部 schmidt 触发 或者 一个 商业上 有 重置 ic.

(做 不 使用 仅有的 一个 rc 电路.)

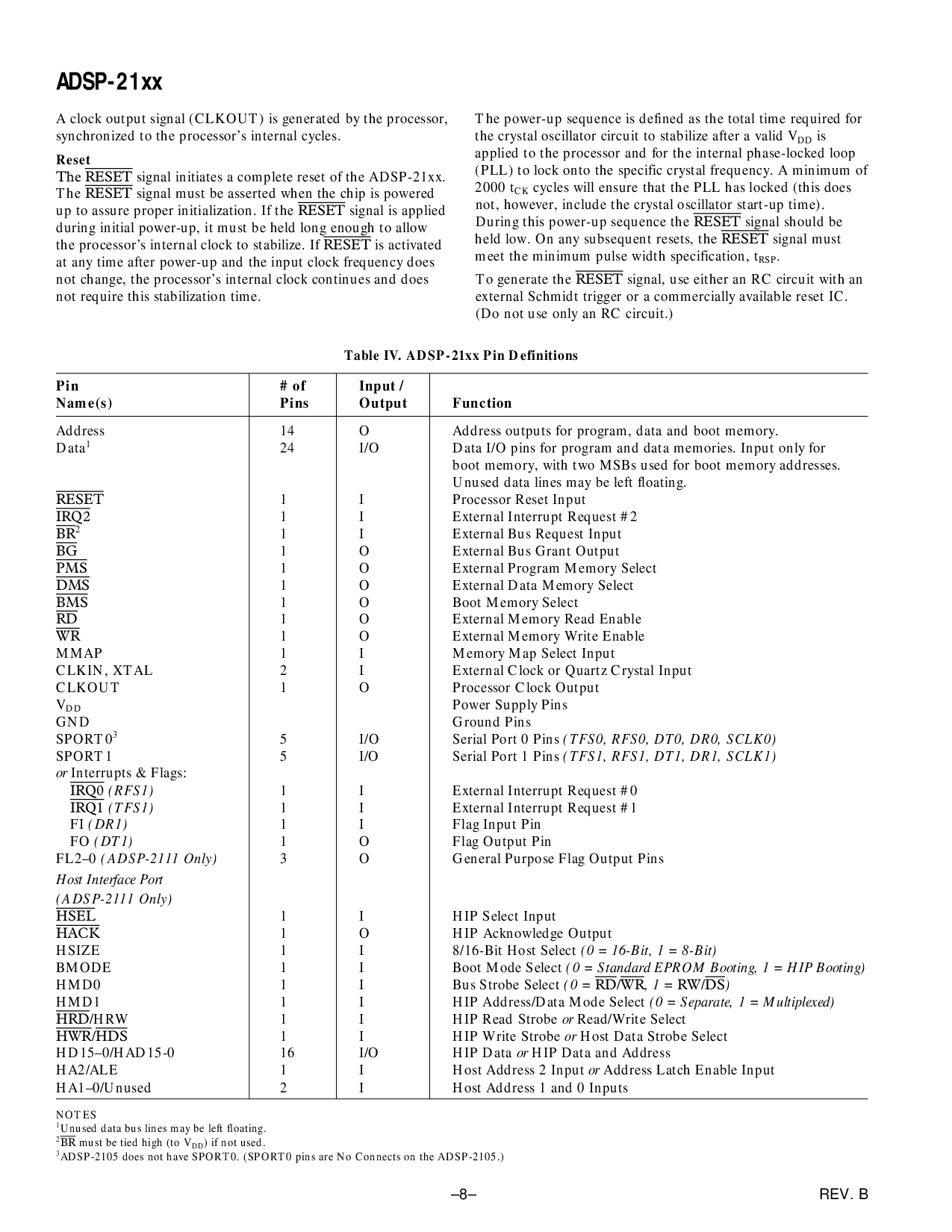

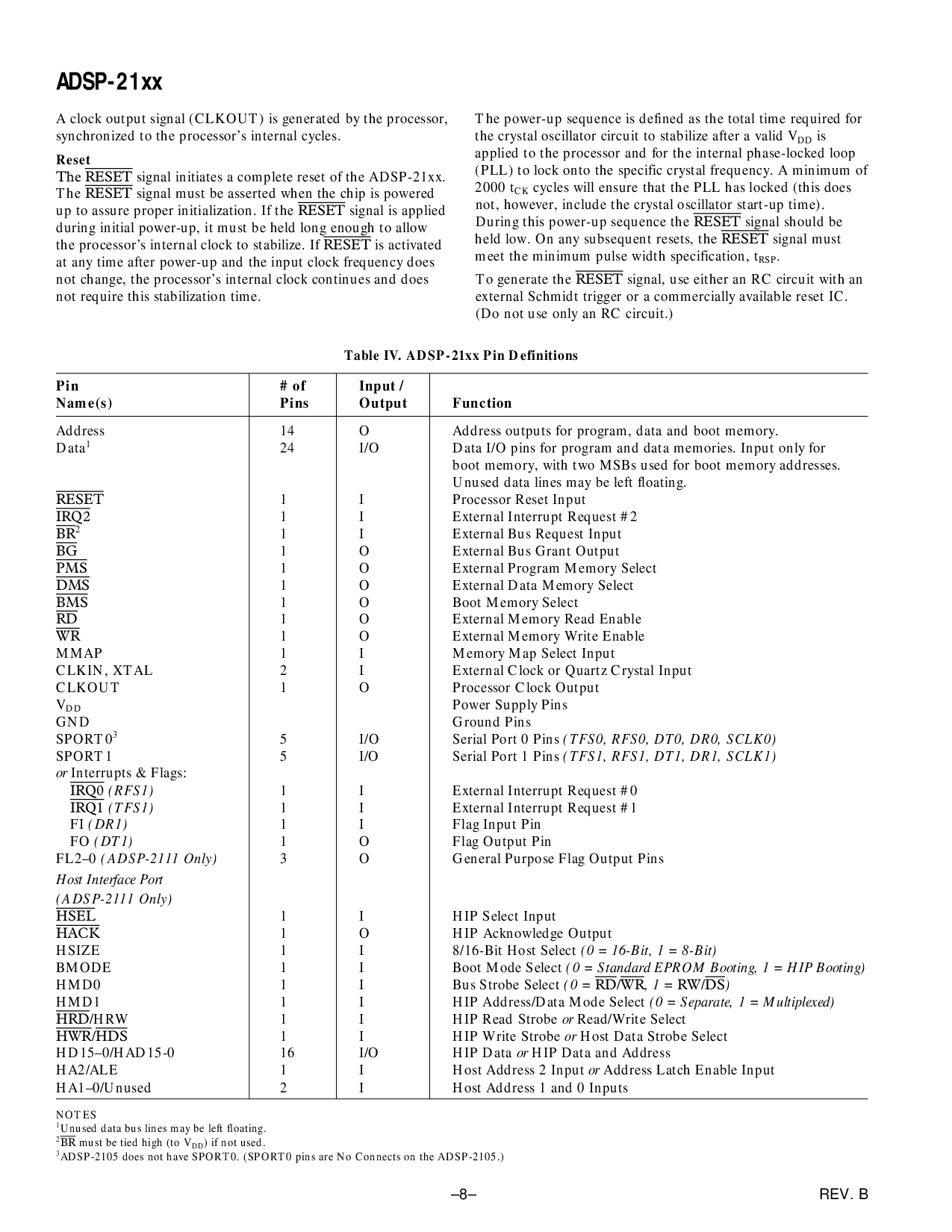

表格 iv. adsp-21xx 管脚 定义

管脚 # 的 输入 /

名字(s) 管脚 输出 函数

地址 14 O 地址 输出 为 程序, 数据 和 激励 记忆.

数据

1

24 i/o 数据 i/o 管脚 为 程序 和 数据 memories. 输入 仅有的 为

激励 记忆, 和 二 msbs 使用 为 激励 记忆 地址.

unused 数据 线条 将 是 left floating.

重置

1 I 处理器 重置 输入

IRQ2

1 I 外部 中断 要求 #2

BR

2

1 I 外部 总线 要求 输入

BG

1 O 外部 总线 grant 输出

PMS

1 O 外部 程序 记忆 选择

DMS

1 O 外部 数据 记忆 选择

BMS

1 O 激励 记忆 选择

RD

1 O 外部 记忆 读 使能

WR

1 O 外部 记忆 写 使能

MMAP 1 I 记忆 编排 选择 输入

clkin, xtal 2 I 外部 时钟 或者 quartz 结晶 输入

CLKOUT 1 O 处理器 时钟 输出

V

DD

电源 供应 管脚

地 地面 管脚

SPORT0

3

5 i/o 串行 端口 0 管脚

(tfs0, rfs0, dt0, dr0, sclk0)

SPORT1 5 i/o 串行 端口 1 管脚

(tfs1, rfs1, dt1, dr1, sclk1)

或者

中断 &放大; flags:

IRQ0

(rfs1)

1 I 外部 中断 要求 #0

IRQ1

(tfs1)

1 I 外部 中断 要求 #1

FI

(dr1)

1 I 标记 输入 管脚

FO

(dt1)

1 O 标记 输出 管脚

FL2–0

(adsp-2111 仅有的)

3 O 一般 目的 标记 输出 管脚

host 接口 端口

(adsp-2111 仅有的)

HSEL

1 I hip 选择 输入

HACK

1 O hip acknowledge 输出

HSIZE 1 I 8/16-位 host 选择

(0 = 16-位, 1 = 8-位)

BMODE 1 I 激励 模式 选择

(0 = 标准 非易失存储器 booting, 1 = hip booting)

HMD0 1 I 总线 strobe 选择

(0 =

RD

/

WR

, 1 =

RW

/

DS

)

HMD1 1 I hip 地址/数据 模式 选择

(0 = 独立的, 1 = 多路复用)

HRD

/hrw 1 I hip 读 strobe

或者

读/写 选择

HWR

/

HDS

1 I hip 写 strobe

或者

host 数据 strobe 选择

hd15–0/had15-0 16 i/o hip 数据

或者

hip 数据 和 地址

ha2/ale 1 I host 地址 2 输入

或者

地址 获得 使能 输入

ha1–0/unused 2 I host 地址 1 和 0 输入

注释

1

unused 数据 总线 线条 将 是 left floating.

2

BR

必须 是 系 高 (至 v

DD

) 如果 不 使用.

3

adsp-2105 做 不 有 sport0. (sport0 管脚 是 非 connects 在 这 adsp-2105.)