5

频率. 在 这个 稳固的 要点 这 电压 在 C2 仍然是

常量 作 这 PC2 输出 是 在 三-状态 和 这 VCO

输入 在 管脚 9 是 一个 高 阻抗. 也 在 这个 情况,

这 信号 在 这 阶段 比较器 脉冲波 输出 (pcp

输出

)

是 一个 高 水平的 和 所以 能 是 使用 为 表明 一个 锁

情况.

因此, 为 pc2, 非 阶段 区别 exists 在 SIG

在

和 竞赛

在

在 这 全部 频率 范围 的 这 vco.

moreover, 这 电源 消耗 预定的 至 这 低-通过 filter 是

减少 因为 两个都 p- 和 n-类型 驱动器 是 “OFF” 为

大多数 的 这 信号 输入 循环. 它 应当 是 指出 那 这

PLL 锁 范围 为 这个 类型 的 阶段 比较器 是 equal 至

这 俘获 范围 和 是 独立 的 这 低-通过 filter.

和 非 信号 呈现 在 SIG

在

, 这 VCO adjusts, 通过 pc2,

至 它的 最低 频率.

阶段 比较器 3 (pc3)

这个 是 一个 积极的 边缘-triggered sequential 阶段

探测器 使用 一个 rs-类型 flip-flop. 当 这 PLL 是 使用

这个 比较器, 这 循环 是 控制 用 积极的 信号

transitions 和 这 职责 factors 的 SIG

在

和 竞赛

在

是

不 重要的. 这 转移 典型的 的 pc3,

假设 波纹 (f

r

= f

i

) 是 suppressed, 是:

V

DEMOUT

=(v

CC

/2p) (fsig

在

- fCOMP

在

) 在哪里

V

DEMOUT

是 这 demodulator 输出 在 管脚 10; V

DEMOUT

= v

PC3OUT

(通过 低-通过 过滤).

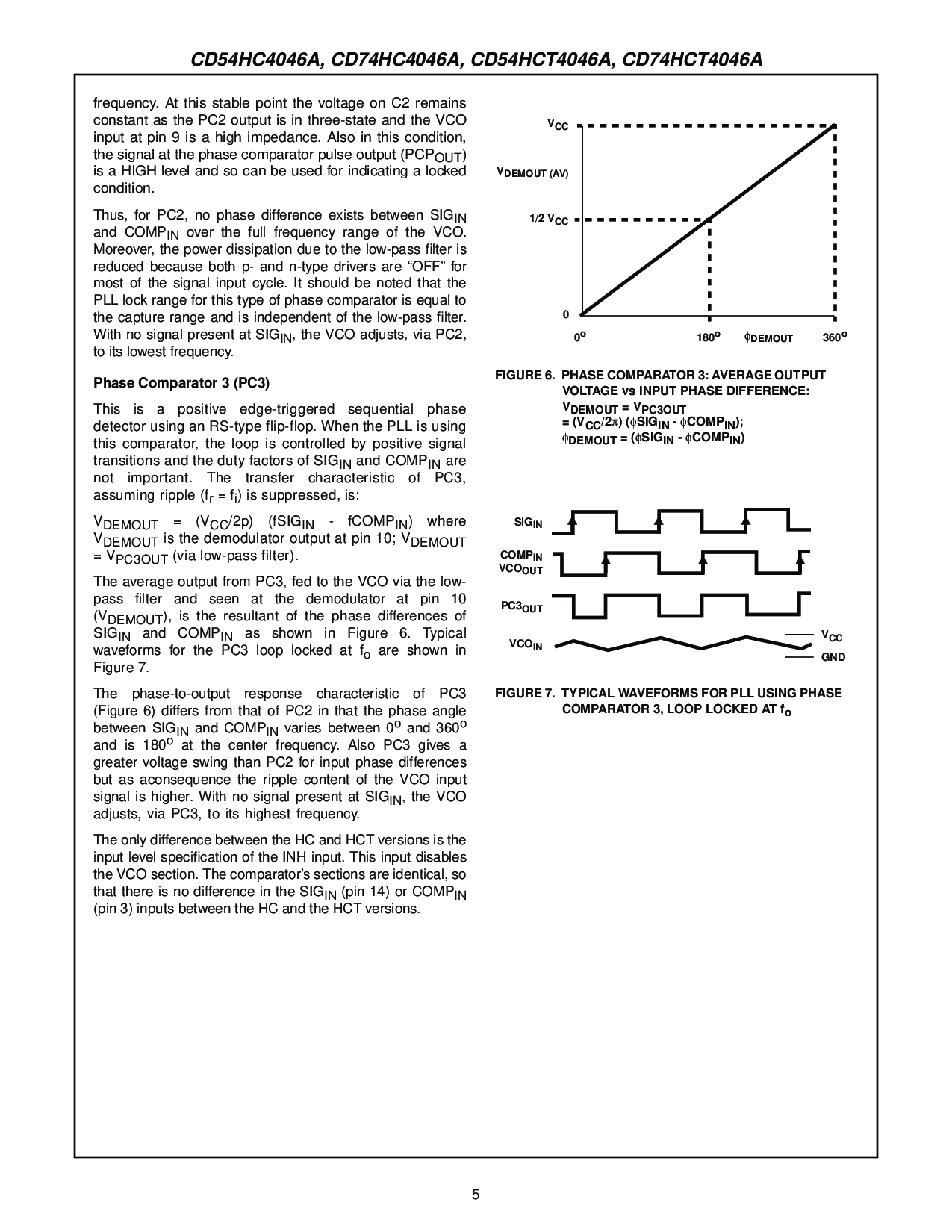

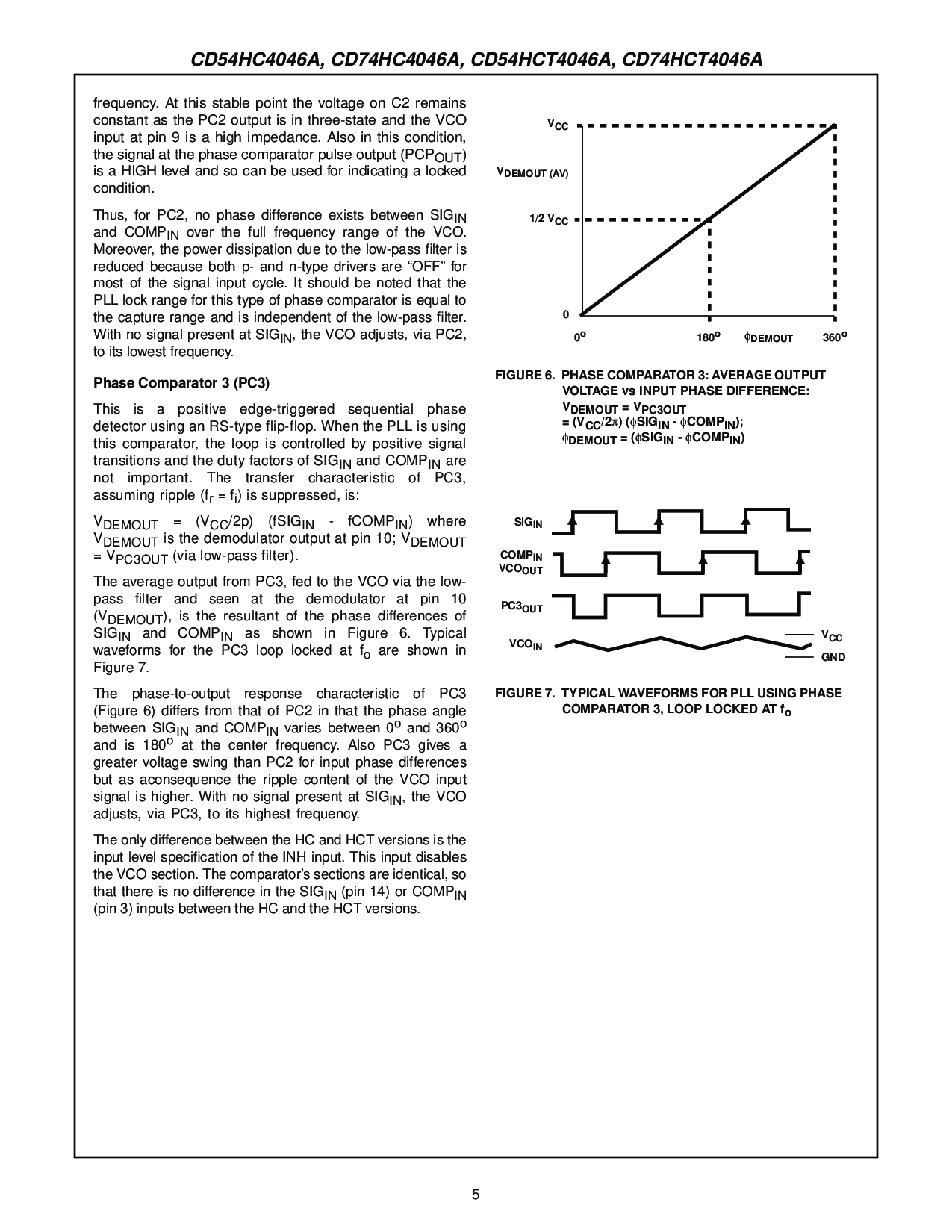

这 平均 输出 从 pc3, 喂养 至 这 VCO 通过 这 低-

通过 过滤 和 seen 在 这 demodulator 在 管脚 10

(v

DEMOUT

), 是 这 resultant 的 这 阶段 differences 的

SIG

在

和 竞赛

在

作 显示 在 图示 6. 典型

波形 为 这 PC3 循环 锁 在 f

o

是 显示 在

图示 7.

这 阶段-至-输出 回馈 典型的 的 PC3

(图示 6) differs 从 那 的 PC2 在 那 这 阶段 角度

在 SIG

在

和 竞赛

在

varies 在 0

o

和 360

o

和 是 180

o

在 这 中心 频率. 也 PC3 给 一个

更好 电压 摆动 比 PC2 为 输入 阶段 differences

但是 作 aconsequence 这 波纹 内容 的 这 VCO 输入

信号 是 高等级的. 和 非 信号 呈现 在 SIG

在

, 这 VCO

adjusts, 通过 pc3, 至 它的 最高的 频率.

这 仅有的 区别 在 这 HC 和 HCT 版本 是 这

输入 水平的 规格 的 这 INH 输入. 这个 输入 使不能运转

这 VCO 部分. 这 comparator’s sections 是 完全同样的, 所以

那 那里 是 非 区别 在 这 SIG

在

(管脚 14) 或者 竞赛

在

(管脚 3) 输入 在 这 hc 和 这 hct 版本.

图示 6. 阶段 比较器 3: 平均 输出

电压 vs 输入 阶段 区别:

V

DEMOUT

= v

PC3OUT

= (v

CC

/2

π

) (

φ

SIG

在

-

φ

竞赛

在

);

φ

DEMOUT

= (

φ

SIG

在

-

φ

竞赛

在

)

V

CC

V

demout (av)

1/2 v

CC

0

0

o

180

o

φ

DEMOUT

360

o

图示 7. 典型 波形 为 PLL 使用 阶段

比较器 3, 循环 锁 在 f

o

SIG

在

竞赛

在

VCO

输出

PC3

输出

VCO

在

V

CC

地

cd54hc4046a, cd74hc4046a, cd54hct4046a, cd74hct4046a