rev. b

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个 将 结果 从 它的 使用. 非 执照 是 准予 用 牵涉 或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

AD9884A

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 2000

100 msps/140 msps

相似物 flat 嵌板 接口

一般 描述

这 ad9884a 是 一个 完全 8-位 140 msps 大而单一的 相似物

接口 优化 为 capturing rgb graphics 信号 从

个人的 计算机 和 workstations. 它的 140 msps encode

比率 能力 和 全部-电源 相似物 带宽 的 500 mhz

支持 显示 resolutions 的 向上 至 1280

×

1024 (sxga) 在

75 hz 和 sufficient 输入 带宽 至 准确地 acquire 和

digitize 各自 pixel.

至 降低 系统 费用 和 电源 消耗, 这 ad9884a

包含 一个 内部的 +1.25 v 涉及, pll 至 发生 一个 pixel

时钟 从 hsync, 和 可编程序的 增益, 补偿 和 clamp

电路. 这 用户 提供 仅有的 一个 +3.3 v 电源 供应, 相似物

输入, 和 hsync 信号. 三-状态 cmos 输出 将 是

powered 用 一个 供应 在 2.5 v 和 3.3 v.

这 ad9884a’s 在-碎片 pll 发生 一个 pixel 时钟 从 这

hsync 输入. pixel 时钟 输出 发生率 范围 从

特性

140 msps 最大 转换 比率

500 mhz 相似物 带宽

0.5 v 至 1.0 v 相似物 输入 范围

400 ps p-p pll 时钟 jitter

电源-向下 模式

3.3 v 电源 供应

2.5 v 至 3.3 v 三-状态 cmos 输出

demultiplexed 输出 端口

数据 时钟 输出 提供

低 电源: 570 mw 典型

内部的 pll 发生 时钟 从 hsync

串行 端口 接口

全部地 可编程序的

支持 alternate pixel 抽样 为 高等级的-

决议 产品

产品

rgb graphics 处理

lcd monitors 和 projectors

plasma 显示 嵌板

scan 转换器

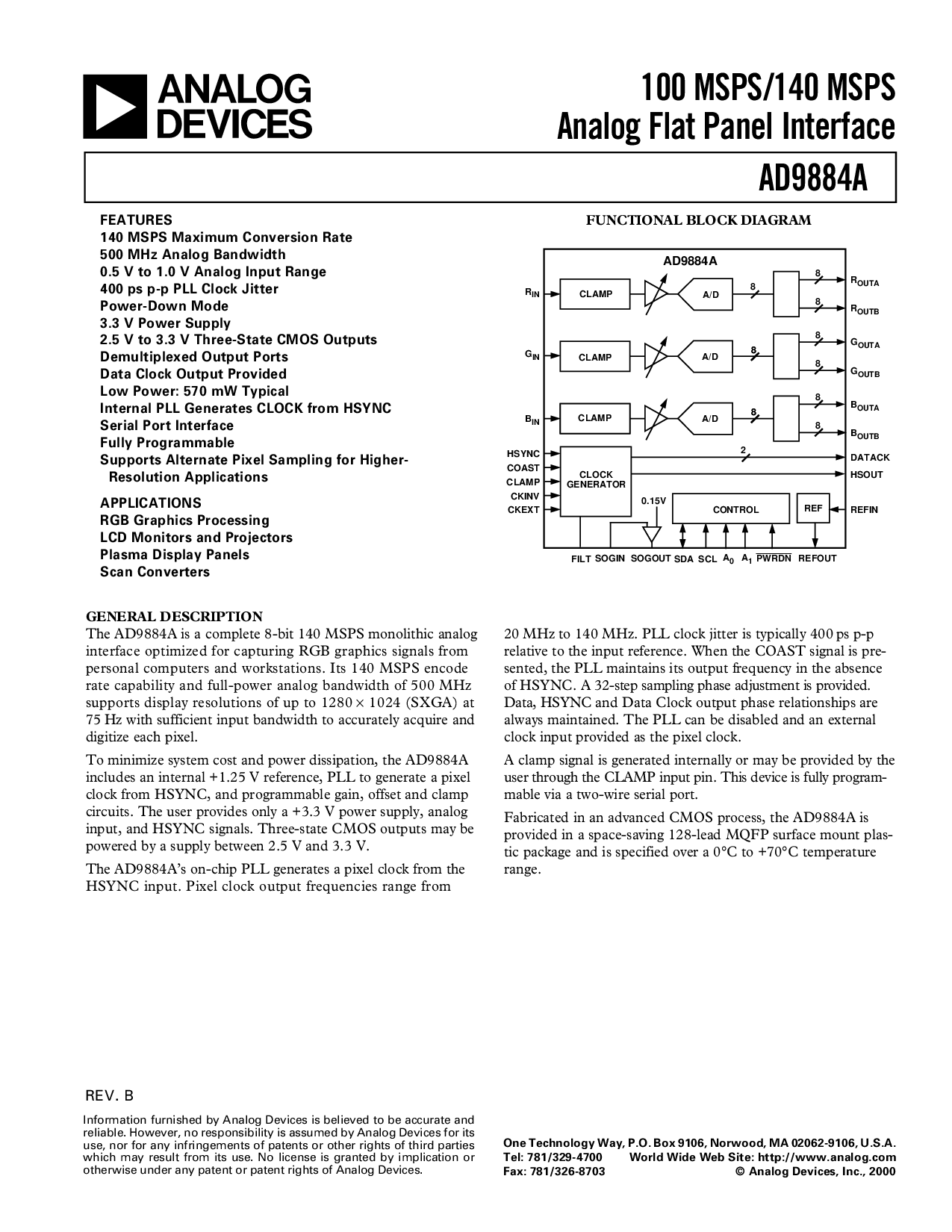

函数的 块 图解

SDA SCL

一个

0

一个

1

PWRDN

HSYNC

COAST

CLAMP

FILT

CKEXT REFIN

CKINV

REFOUT

8

一个/d

CLAMP

R

在

G

在

B

在

8

一个/d

CLAMP

8

8

一个/d

CLAMP

8

REF

8

8

8

8

8

8

SOGIN

0.15v

2

AD9884A

时钟

发生器

SOGOUT

DATACK

R

OUTA

R

OUTB

G

OUTA

G

OUTB

B

OUTA

B

OUTB

HSOUT

控制

20 mhz 至 140 mhz. pll 时钟 jitter 是 典型地 400 ps p-p

相关的 至 这 输入 涉及. 当 这 coast 信号 是 前-

sented, 这 pll 维持 它的 输出 频率 在 这 absence

的 hsync. 一个32-步伐 抽样 阶段 调整 是 提供.

数据, hsync 和 data 时钟 输出 阶段 relationships 是

总是 maintained. 这 pll 能 是 无能 和 一个 外部

时钟 输入 提供 作 这 pixel 时钟.

一个 clamp 信号 是 发生 内部 或者 将 是 提供 用 这

用户 通过 这 clamp 输入 管脚. 这个 设备 是 全部地 程序-

mable 通过 一个 二-线 串行 端口.

fabricated 在 一个 先进的 cmos 处理, 这 ad9884a 是

提供 在 一个 空间-节省 128-含铅的 mqfp 表面 挂载 plas-

tic 包装 和 是 指定 在 一个 0

°

c 至 +70

°

c 温度

范围.