初步的

频率 发生器 为 整体的 核心 逻辑

和 133-mhz fsb

W209C

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文档 #: 38-07171 rev. *a 修订 12月 15, 2002

特性

• maximized emi 抑制 使用 cypress’s 展开

spectrum 技术

• 低 jitter 和 tightly 控制 时钟 skew

• 高级地 整体的 设备 供应 clocks 必需的 为

cpu, 核心 逻辑, 和 sdram

• 二 copies 的 cpu 时钟

• nine copies 的 sdram 时钟

• 第八 copies 的 pci 时钟

• 一个 copy 的 同步的 apic 时钟

• 二 copies 的 66-mhz 输出

• 二 copies 的 48-mhz 输出

• 一个 copy 的 可选择的 24- 或者 48-mhz 时钟

• 一个 copy 的 翻倍 力量 14.31818-mhz 涉及

时钟

• 电源-向下 控制

• smbus 接口 为 turning 止 unused clocks

关键 规格

cpu, sdram 输出 循环-至-循环 jitter: ............. 250 ps

apic, 48-mhz, 3v66, pci 输出

循环-至-循环 jitter:................................................... 500 ps

cpu, 3v66 输出 skew: ........................................... 175 ps

sdram, apic, 48-mhz 输出 skew: ....................... 250 ps

pci 输出 skew: ....................................................... 500 ps

cpu 至 sdram skew (@ 133 mhz) .......................

± 0.5 ns

cpu 至 sdram skew (@ 100 mhz) ................. 4.5 至 5.5 ns

cpu 至 3v66 skew (@ 66 mhz)........................ 7.0 至 8.0 ns

3v66 至 pci skew (3v66 含铅的) .......................... 1.5 至 3.5 ns

pci 至 apic skew..................................................... ± 0.5 ns

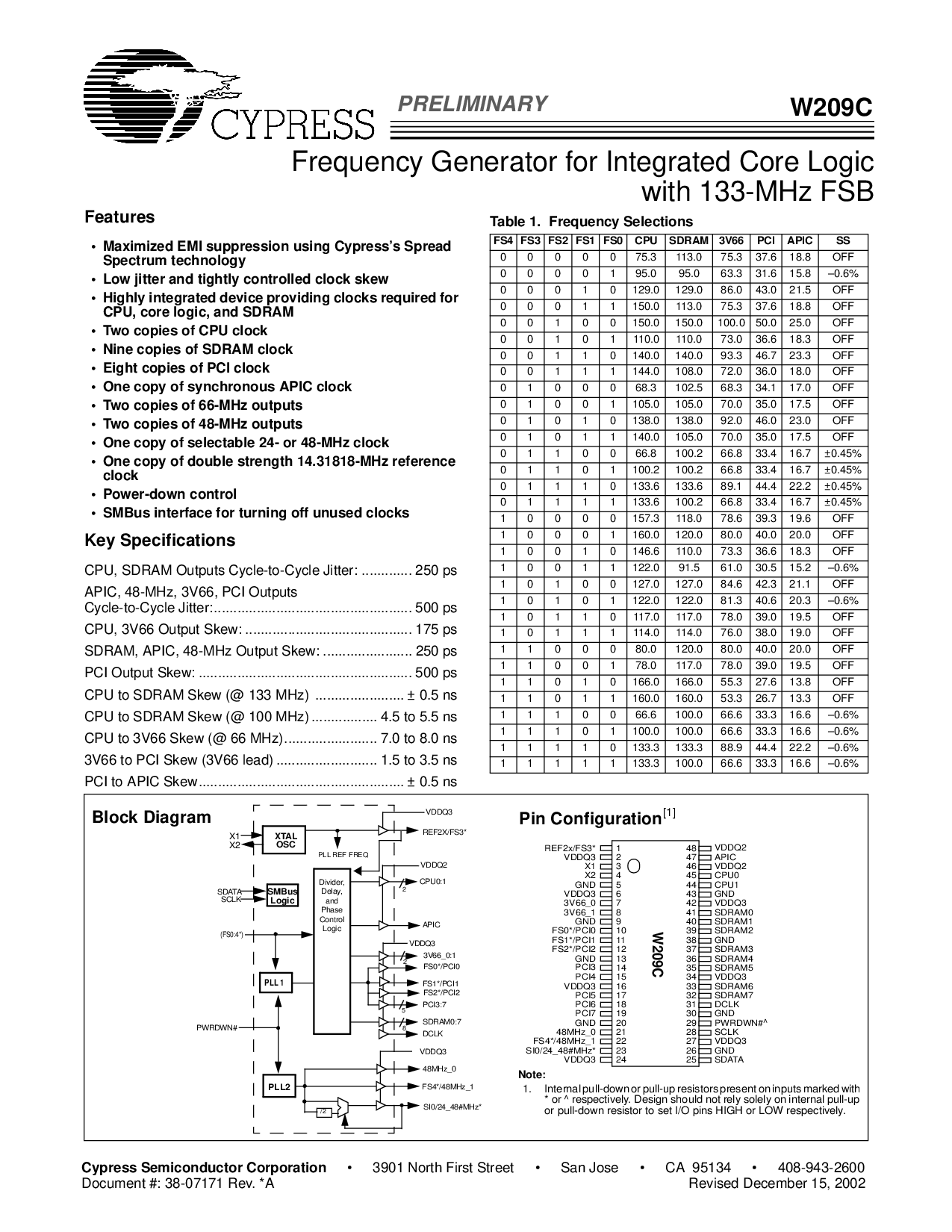

表格 1. 频率 selections

FS4 FS3 FS2 FS1 FS0 CPU SDRAM 3V66 PCI APIC SS

0 0 0 0 0 75.3 113.0 75.3 37.6 18.8 止

0 0 0 0 1 95.0 95.0 63.3 31.6 15.8

–

0.6%

0 0 0 1 0 129.0 129.0 86.0 43.0 21.5 止

0 0 0 1 1 150.0 113.0 75.3 37.6 18.8 止

0 0 1 0 0 150.0 150.0 100.0 50.0 25.0 止

0 0 1 0 1 110.0 110.0 73.0 36.6 18.3 止

0 0 1 1 0 140.0 140.0 93.3 46.7 23.3 止

0 0 1 1 1 144.0 108.0 72.0 36.0 18.0 止

0 1 0 0 0 68.3 102.5 68.3 34.1 17.0 止

0 1 0 0 1 105.0 105.0 70.0 35.0 17.5 止

0 1 0 1 0 138.0 138.0 92.0 46.0 23.0 止

0 1 0 1 1 140.0 105.0 70.0 35.0 17.5 止

0 1 1 0 0 66.8 100.2 66.8 33.4 16.7 ±0.45%

0 1 1 0 1 100.2 100.2 66.8 33.4 16.7 ±0.45%

0 1 1 1 0 133.6 133.6 89.1 44.4 22.2 ±0.45%

0 1 1 1 1 133.6 100.2 66.8 33.4 16.7 ±0.45%

1 0 0 0 0 157.3 118.0 78.6 39.3 19.6 止

1 0 0 0 1 160.0 120.0 80.0 40.0 20.0 止

1 0 0 1 0 146.6 110.0 73.3 36.6 18.3 止

1 0 0 1 1 122.0 91.5 61.0 30.5 15.2

–

0.6%

1 0 1 0 0 127.0 127.0 84.6 42.3 21.1 止

1 0 1 0 1 122.0 122.0 81.3 40.6 20.3

–

0.6%

1 0 1 1 0 117.0 117.0 78.0 39.0 19.5 止

1 0 1 1 1 114.0 114.0 76.0 38.0 19.0 止

1 1 0 0 0 80.0 120.0 80.0 40.0 20.0 止

1 1 0 0 1 78.0 117.0 78.0 39.0 19.5 止

1 1 0 1 0 166.0 166.0 55.3 27.6 13.8 止

1 1 0 1 1 160.0 160.0 53.3 26.7 13.3 止

1 1 1 0 0 66.6 100.0 66.6 33.3 16.6

–

0.6%

1 1 1 0 1 100.0 100.0 66.6 33.3 16.6

–

0.6%

1 1 1 1 0 133.3 133.3 88.9 44.4 22.2

–

0.6%

1 1 1 1 1 133.3 100.0 66.6 33.3 16.6

–

0.6%

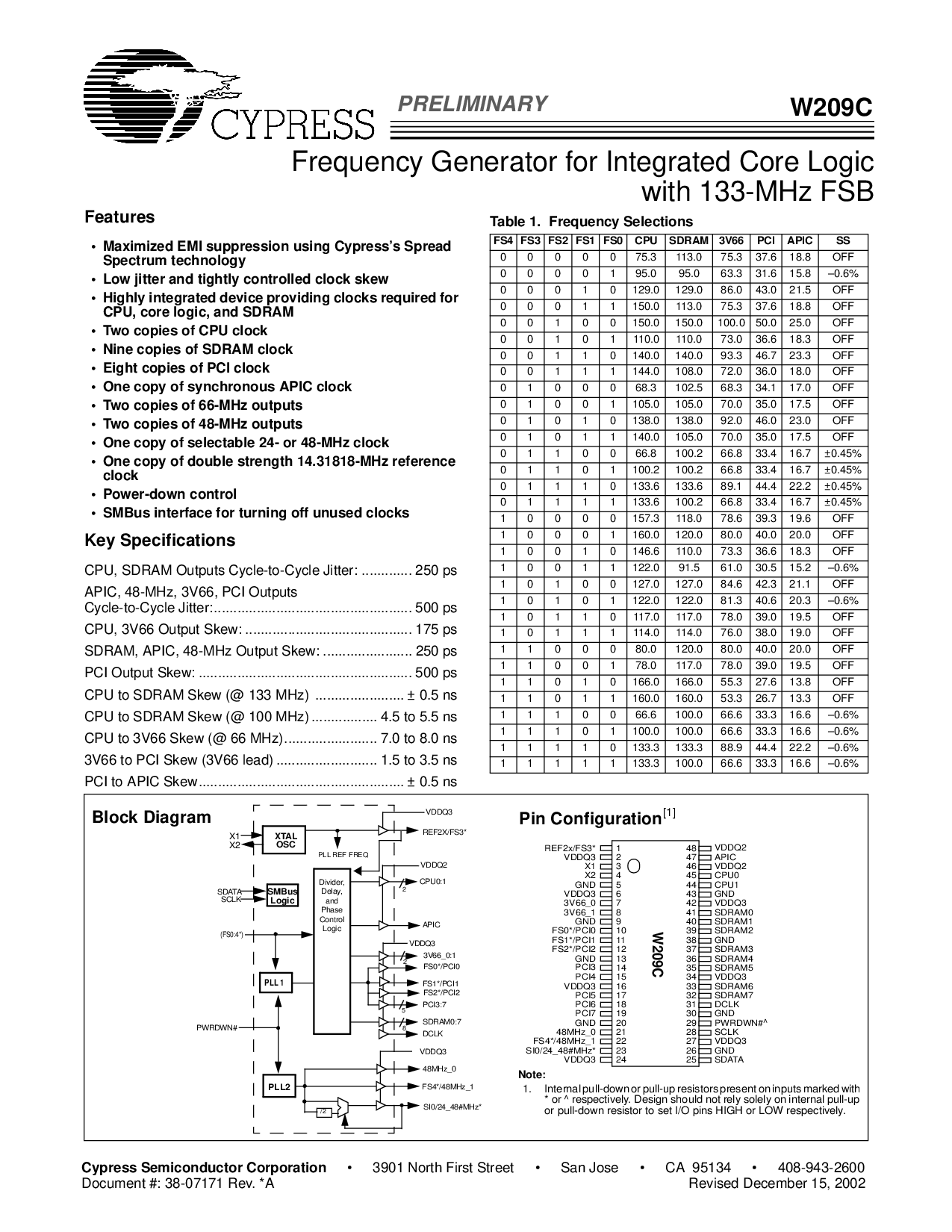

块 图解

管脚 配置

便条:

1. 内部的 拉-向下 或者 拉-向上 电阻器 呈现 在 输入 marked 和

* 或者 ^ 各自. 设计 应当 不 rely solely 在 内部的 拉-向上

或者 拉-向下 电阻 至 设置 i/o 管脚 高 或者 低 各自.

[1]

ref2x/fs3*

VDDQ3

X1

X2

地

VDDQ3

3v66_0

3v66_1

地

fs0*/pci0

fs1*/pci1

fs2*/pci2

地

PCI3

PCI4

VDDQ3

PCI5

PCI6

PCI7

地

48mhz_0

fs4*/48mhz_1

si0/24_48#mhz*

VDDQ3

W209C

VDDQ2

APIC

VDDQ2

CPU0

CPU1

地

VDDQ3

SDRAM0

SDRAM1

SDRAM2

地

SDRAM3

SDRAM4

SDRAM5

VDDQ3

SDRAM6

SDRAM7

DCLK

地

PWRDWN#

^

SCLK

VDDQ3

地

SDATA

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

VDDQ3

VDDQ2

fs1*/pci1

XTAL

pll ref freq

pll 1

X2

X1

ref2x/fs3*

pci3:7

fs4*/48mhz_1

si0/24_48#mhz*

PLL2

OSC

VDDQ3

SMBus

SDATA

逻辑

SCLK

3v66_0:1

cpu0:1

APIC

分隔物,

延迟,

和

阶段

控制

逻辑

2

VDDQ3

2

sdram0:7

8

PWRDWN#

fs0*/pci0

fs2*/pci2

/2

(fs0:4*)

5

48mhz_0

DCLK