MT8941B

数据 薄板

8

zarlink 半导体 公司

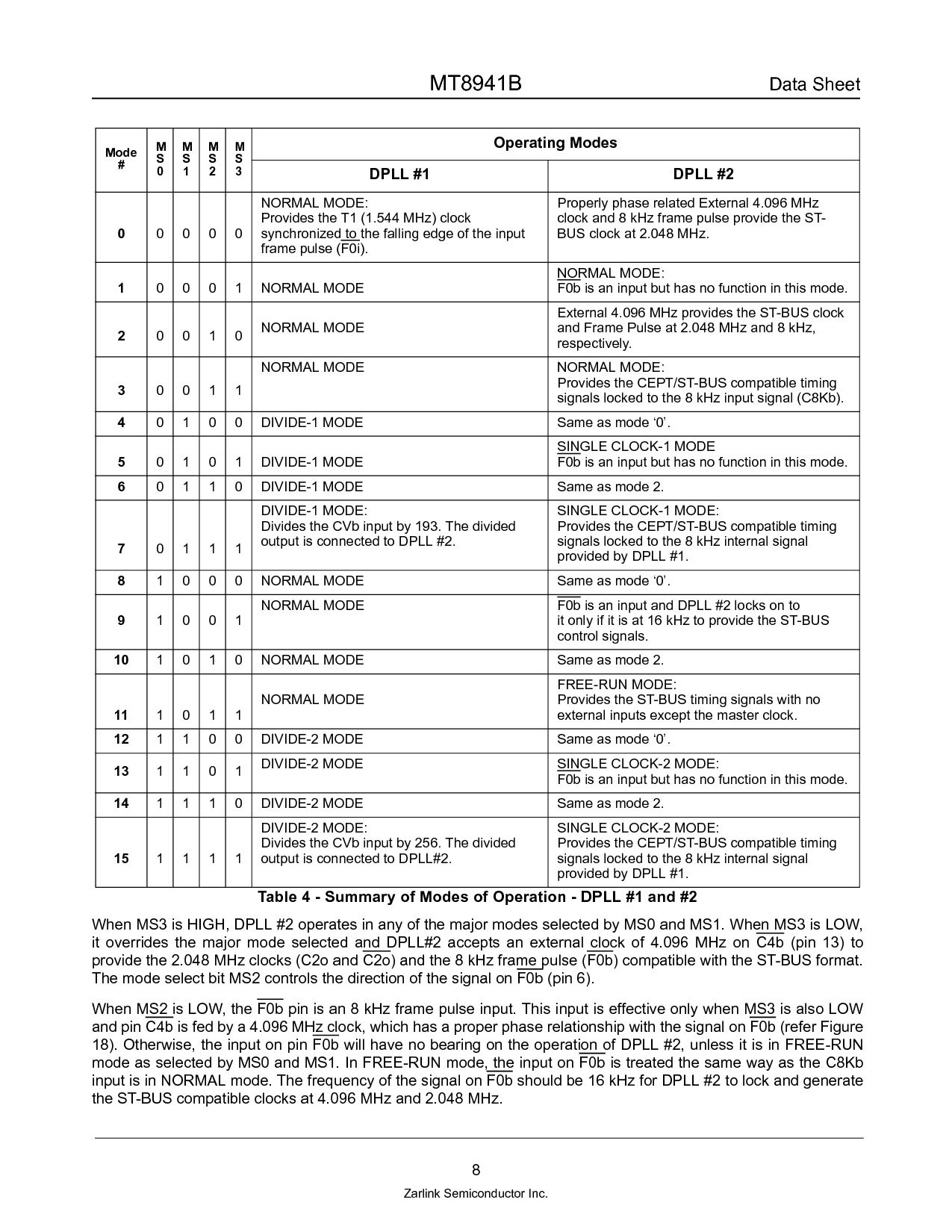

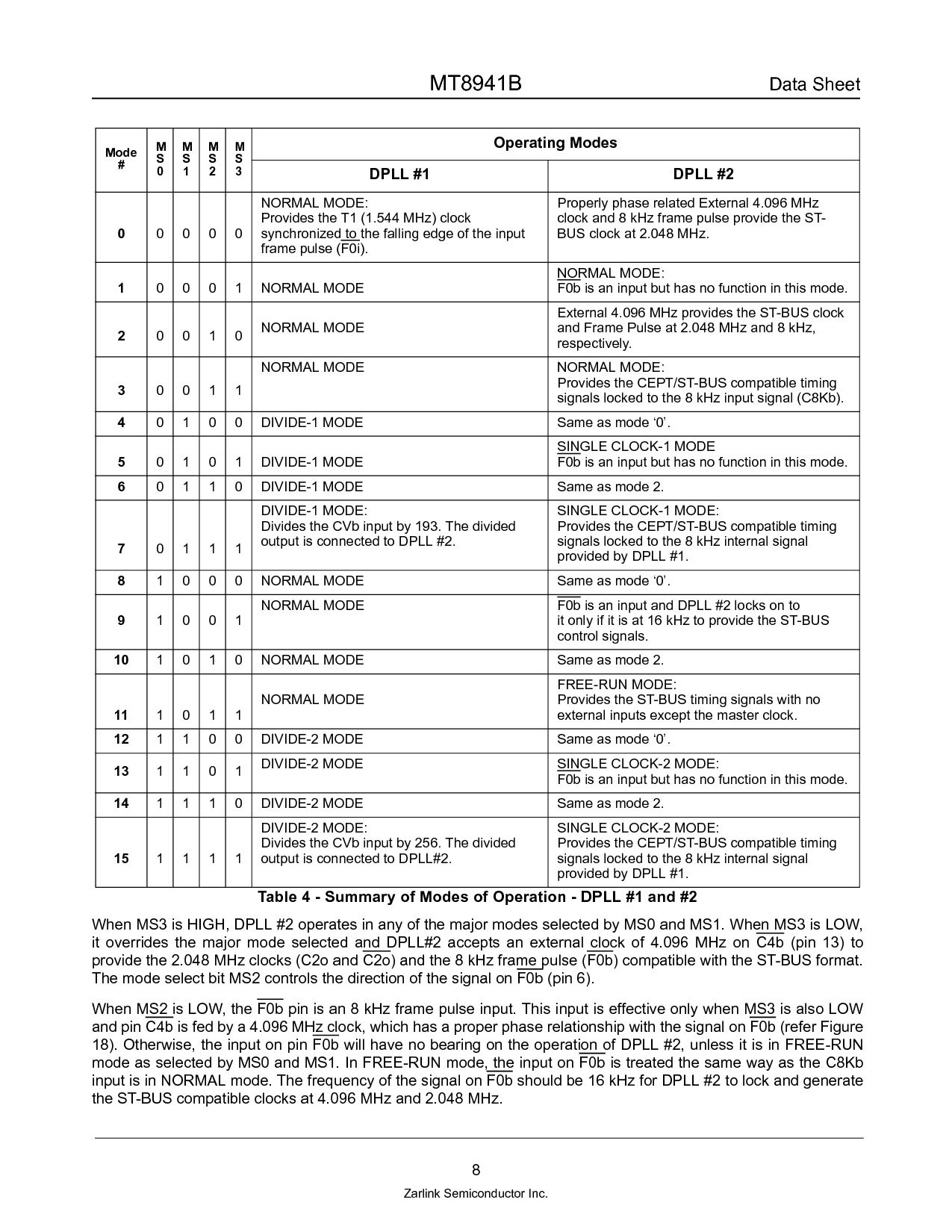

表格 4 - summary 的 模式 的 运作 - dpll #1 和 #2

当 ms3 是 高, dpll #2 运作 在 任何 的 这 主要的 模式 选择 用 ms0 和 ms1. 当 ms3 是 低,

它 overrides 这 主要的 模式 选择 和 dpll#2 一个ccepts 一个 外部 时钟 的 4.096 mhz 在 c4b

(管脚 13) 至

提供 这 2.048 mhz clocks (c2o 和 c2o

) 和 这 8 khz 框架 脉冲波 (f0b) 兼容 和 这 st-总线 format.

这 模式 选择 位 ms2 控制这 方向 的 这 信号 在 f0b

(管脚 6).

当 ms2 是 低, 这 f0b

管脚 是 一个 8 khz 框架 脉冲波 输入. 这个 输入 是 有效的 仅有的 当 ms3 是 也 低

和 管脚 c4b

是 喂养 用 一个 4.096 mhz 时钟, 这个 有 一个 恰当的 阶段 relationship 和 这 信号 在 f0b(谈及 图示

18). 否则, 这 输入 在 管脚 f0b

将 有 非 bearing 在 这 运作 的dpll #2, 除非 它 是 在 自由-run

模式 作 选择 用 ms0 和 ms1. 在 自由-run 模式, 这 输入 在 f0b

是 treated 这 一样 方法 作 这 c8kb

输入 是 在 正常的 模式. the 频率 的 这 信号 在 f0b

应当 是 16 khz 为 dpll #2 至 锁 和 发生

这 st-总线 兼容 clocks 在 4.096 mhz 和 2.048 mhz.

模式

#

M

S

0

M

S

1

M

S

2

M

S

3

运行 模式

dpll #1 dpll #2

0

0000

正常的 模式:

提供 这 t1 (1.544 mhz) 时钟

同步 至 这 下落 边缘 的 这 输入

框架 脉冲波 (f0i

).

合适的 阶段 related 外部 4.096 mhz

时钟 和 8 khz 框架 脉冲波 提供 这 st-

总线 时钟 在 2.048 mhz.

1

0001normal 模式

正常的 模式:

F0b

是 一个 输入 但是 有 非 函数 在 这个 模式.

2

0010

正常的 模式

外部 4.096 mhz 提供 这 st-总线 时钟

和 框架 脉冲波 在 2.048 mhz 和 8 khz,

各自.

3

0011

正常的 模式 正常的 模式:

提供 这 cept/st-总线 兼容 定时

信号 锁 至 这 8 khz 输入 信号 (c8kb).

4

0100divide-1 模式 一样 作 模式 ‘0’.

5

0101divide-1 模式

单独的 时钟-1 模式

F0b

是 一个 输入 但是 有 非 函数 在 这个 模式.

6

0110divide-1 模式 一样 作 模式 2.

7

0111

分隔-1 模式:

divides 这 cvb 输入 用 193. 这 分隔

输出 是 连接 至 dpll #2.

单独的 时钟-1 模式:

提供 这 cept/st-总线 兼容 定时

信号 锁 至 这 8 khz 内部的 信号

提供 用 dpll #1.

8

1000normal 模式 一样 作 模式 ‘0’.

9

1001

正常的 模式 F0b

是 一个 输入 和 dpll #2 locks 在 至

它 仅有的 如果 它 是 在 16 khz 至 提供 这 st-总线

控制 信号.

10

1010normal 模式 一样 作 模式 2.

11

1011

正常的 模式

自由-run 模式:

提供 这 st-总线 定时 信号 和 非

外部 输入 除了 这 主控 时钟.

12

1100divide-2 模式 一样 作 模式 ‘0’.

13

1101

分隔-2 模式 单独的 时钟-2 模式:

F0b

是 一个 输入 但是 有 非 函数 在 这个 模式.

14

1110divide-2 模式 一样 作 模式 2.

15

1111

分隔-2 模式:

divides 这 cvb 输入 用 256. 这 分隔

输出 是 连接 至 dpll#2.

单独的 时钟-2 模式:

提供 这 cept/st-总线 兼容 定时

信号 锁 至 这 8 khz 内部的 信号

提供 用 dpll #1.