MT8941B

数据 薄板

4

zarlink 半导体 公司

函数的 描述

这 mt8941b 是 一个 双 数字的 阶段-锁 循环 供应 这 定时 和 synchronization 信号 至 这 接口

电路 为 t1 和 cept (30+2) primary multiplex digital 传递 links. 作 显示 在 这 函数的 块

图解 (看 图示 1), 这 mt8941b 有 二 数字的 阶段-锁 循环 (dplls), 有关联的 输出 控制 和

这 模式 选择 逻辑 电路. 这 二 dplls, 虽然类似的 在 principle, operate independently 至 提供 t1

(1.544 mhz) 和 cept (2.048 mhz) transmission clocks 和 st-总线 定时 信号.

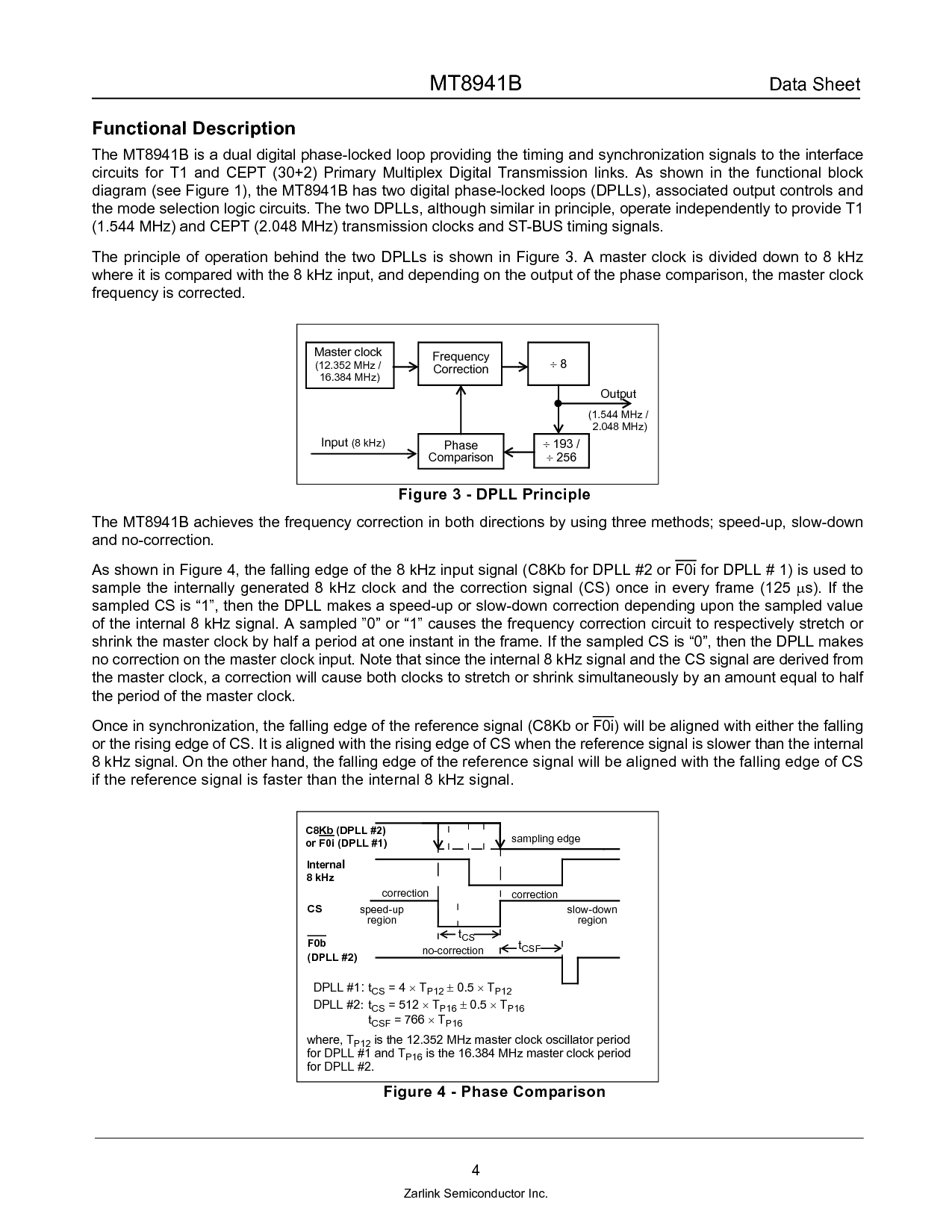

这 principle 的 运作 behind 这 二 dplls 是 显示 在 图示 3. 一个 master 时钟 是 分隔 向下 至 8 khz

在哪里 它 是 对照的 和 这 8 khz 输入, 和 取决于在 这 输出 的 这 阶段 comparison, 这 主控 时钟

频率 是 corrected.

图示 3 - dpll principle

这 mt8941b achieves 这 频率 纠正 在 两个都方向 用 使用 三 方法; 速-向上, 慢-向下

和 非-纠正.

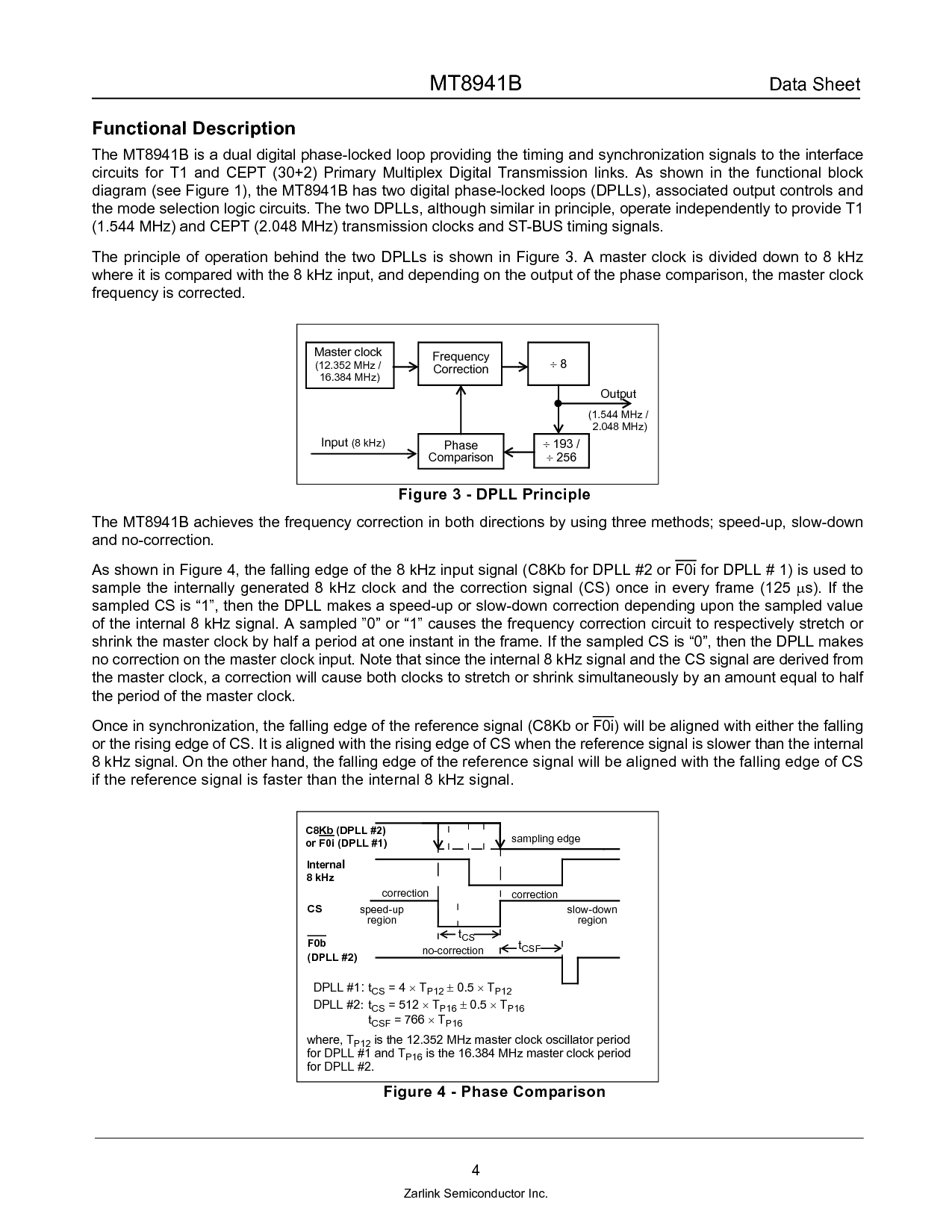

作 显示 在 图示 4, 这 下落 边缘 的 这8 khz 输入 信号 (c8kb 为 dpll #2 或者 f0i

为 dpll # 1) 是 使用 至

样本 这 内部 发生 8 khz 时钟 和 the 纠正 信号 (cs) once 在 每 框架 (125

µ

s). 如果 这

抽样 cs 是 “1”, 然后 这 dpll 制造 一个 速-向上 或者 慢-向下 纠正 取决于 在之上 这 抽样 值

的 这 内部的 8 khz 信号. 一个 抽样 ”0” 或者 “1” 导致这 频率 纠正 circuit 至 各自 stretch 或者

shrink 这 主控 时钟 用 half 一个 时期在 一个 instant 在 这 框架. 如果 这 sampled cs 是 “0”, 然后 这 dpll 制造

非 纠正 在 这 主控 时钟 输入.便条 那 自从 这 内部的 8 khz signal 和 这 cs 信号 是 获得 从

这 主控 时钟, 一个 纠正 将 ca使用 两个都 clocks 至 stretch 或者 shrink 同时发生地 用 一个 数量 equal 至 half

这 时期 的 the 主控 时钟.

once 在 同步, 这 下落 边缘 的 这 涉及 信号 (c8kb 或者

F0i

) 将 是 排整齐 和也 这 下落

或者 这 rising 边缘 的 cs. 它 是 排整齐 with 这 rising 边缘 的 cs 当 这 reference 信号 是 slower 比 这 内部的

8 khz 信号. 在 这 other hand, 这 falling 边缘 的 这 涉及 signal 将 是 排整齐 和 这 下落 边缘 的 cs

如果 这 涉及 信号 是 faster 比 这 内部的 8 khz 信号.

图示 4 - 阶段 comparison

主控 时钟

(12.352 mhz /

16.384 mhz)

频率

纠正

÷

8

输出

(1.544 mhz /

2.048 mhz)

输入

(8 khz)

阶段

Comparison

÷

193 /

÷

256

c8kb (dpll #2)

或者 f0i

(dpll #1)

抽样 边缘

Interna

l

8 khz

纠正

纠正

CS

速-向上

区域

慢-向下

区域

t

CS

t

CSF

非-纠正

F0b

(dpll #2)

dpll #1

:

dpll #2:

t

CSF

= 766

×

T

P16

在哪里, t

P12

是 这 12.352 mhz 主控 时钟 振荡器 时期

为 dpll #1 和 t

P16

是 这 16.384 mhz 主控 时钟 时期

为 dpll #2.

t

CS

= 4

×

T

P12

±

0.5

×

T

P12

t

CS

= 512

×

T

P16

±

0.5

×

T

P16