80C186XL80C188XL

DRAM Refresh 控制 单位

这 Refresh 控制 单位 (rcu) automatically gen-

erates DRAM refresh 总线 cycles 这 RCU 运作

仅有的 在 增强 Mode 之后 一个 可编程序的 peri-

od 的 time 这 RCU 发生 一个 记忆 读 re-

quest 至 这 BIU 如果 这 地址 发生 在 一个

refresh 总线 循环 是 在里面 这 范围 的 一个 合适的

编写程序 碎片 select 那 碎片 选择 将 是 acti-

vated 当 这 BIU executes 这 refresh 总线 cycle

电源-保存 控制

这 80C186XL 当 在 增强 Mode 能 enter

一个 电源 节省 状态 用 内部 dividing 这 proc-

essor 时钟 频率 用 一个 可编程序的 factor

这个 分隔 频率 是 也 有 在 这

CLKOUT pin

所有 内部的 logic 包含 这 Refresh 控制 单位

和 这 timers 有 它们的 clocks slowed 向下 用

这 分隔 factor 至 维持 一个 real 时间 计数 或者 一个

fixed DRAM refresh rate 这些 peripherals 必须 是

re-编写程序 当 进去 和 leaving 这 pow-

er-保存 mode

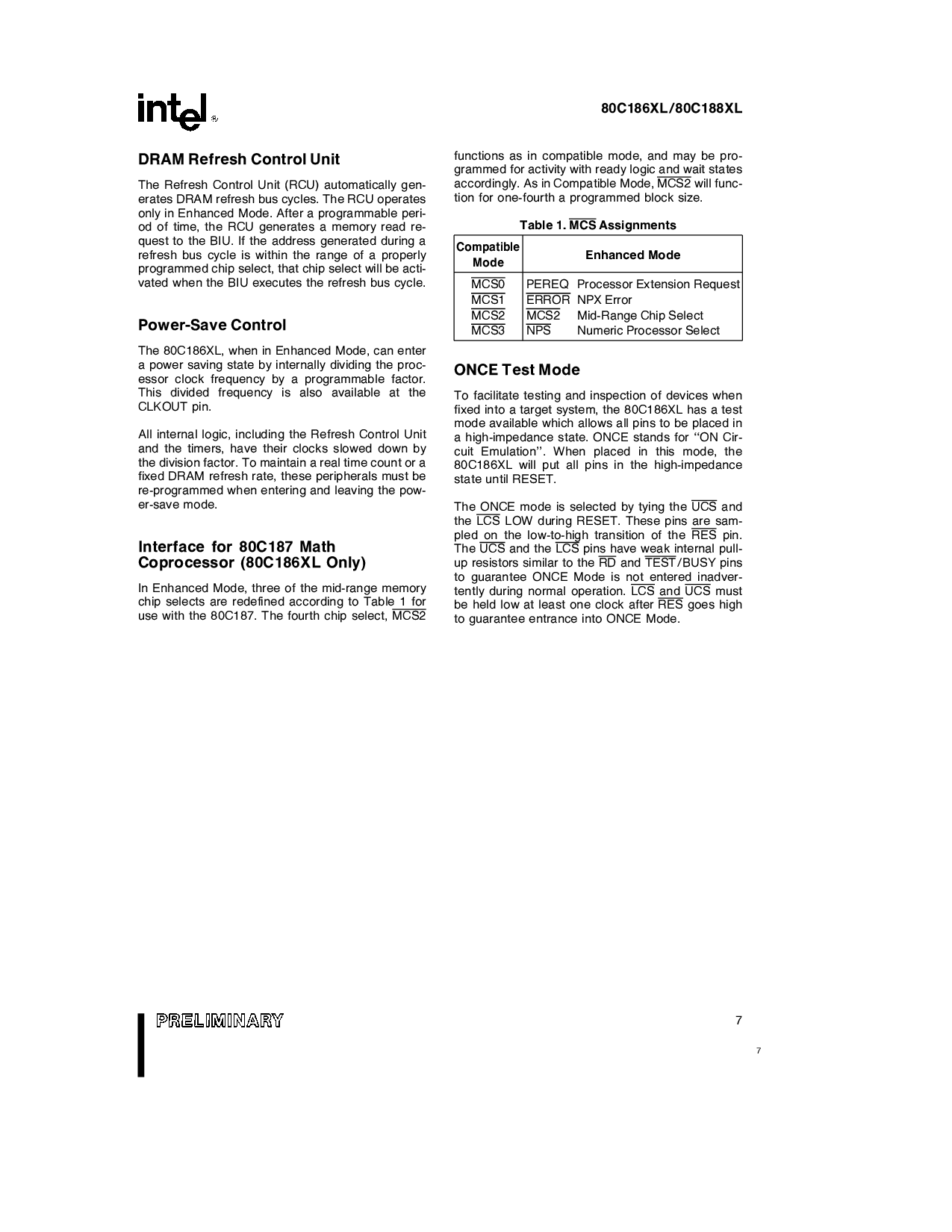

接口 为 80C187 Math

Coprocessor (80c186xl 仅有的)

在 增强 Mode 三 的 这 mid-范围 记忆

碎片 选择 是 redefined 符合 至 表格 1 为

使用 和 这 80C187 这 fourth 碎片 select MCS2

功能 作 在 兼容 mode 和 将 是 pro-

grammed 为 activity 和 准备好 逻辑 和 wait states

accordingly 作 在 兼容 Mode MCS2

将 func-

tion 为 一个-fourth 一个 编写程序 块 size

表格 1 MCS

Assignments

兼容

增强 模式

模式

MCS0 PEREQ 处理器 Extension 要求

MCS1

错误 NPX 错误

MCS2

MCS2 mid-范围 碎片 选择

MCS3

NPS Numeric 处理器 选择

ONCE 测试 模式

至 facilitate 测试 和 inspection 的 设备 当

fixed 在 一个 目标 system 这 80C186XL 有 一个 测试

模式 有 这个 准许 所有 管脚 至 是 放置 在

一个 高-阻抗 state ONCE stands 为 ‘‘ON cir-

cuit Emulation’’ 当 放置 在 这个 mode 这

80C186XL 将 放 所有 管脚 在 这 高-阻抗

状态 直到 RESET

这 ONCE 模式 是 选择 用 tying 这 UCS

和

这 LCS

低 在 RESET 这些 管脚 是 sam-

pled 在 这 低-至-高 转变 的 这 RES

pin

这 UCS

和 这 LCS 管脚 有 弱 内部的 拉-

向上 电阻器 类似的 至 这 RD

和 TESTBUSY 管脚

至 保证 ONCE 模式 是 不 entered inadver-

tently 在 正常的 operation LCS

和 UCS 必须

是 使保持 低 在 least 一个 时钟 之后 RES

变得 高

至 保证 entrance 在 ONCE Mode

7

7