ADS7832

10

®

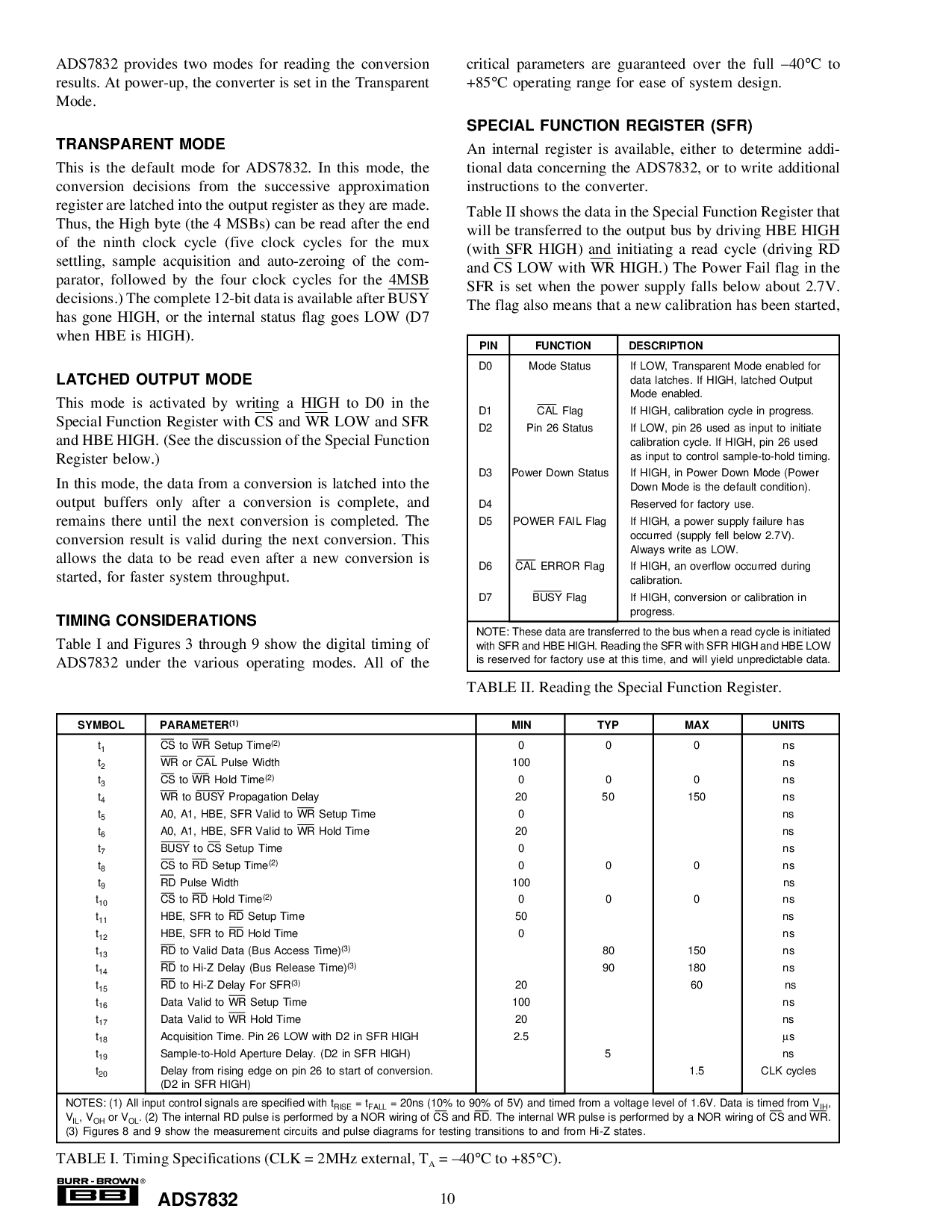

管脚 函数 描述

D0 模式 状态 如果 低, transparent 模式 使能 为

数据 latches. 如果 高, latched 输出

模式 使能.

D1 cal 标记 如果 高, 校准 循环 在 progress.

D2 管脚 26 状态 如果 低, 管脚 26 使用 作 输入 至 initiate

校准 循环. 如果 高, 管脚 26 使用

作 输入 至 控制 样本-至-支撑 定时.

D3 电源 向下 状态 如果 高, 在 电源 向下 模式 (电源

向下 模式 是 这 default 情况).

D4 保留 为 工厂 使用.

D5 电源 失败 标记 如果 高, 一个 电源 供应 失败 有

occurred (供应 fell 在下 2.7v).

总是 写 作 低.

D6 cal 错误 标记 如果 高, 一个 overflow occurred 在

校准.

D7 busy 标记 如果 高, 转换 或者 校准 在

progress.

便条: 这些 数据 是 transferred 至 这 总线 当 一个 读 循环 是 initiated

和 sfr 和 hbe 高. 读 这 sfr 和 sfr 高 和 hbe 低

是 保留 为 工厂 使用 在 这个 时间, 和 将 yield unpredictable 数据.

核心的 参数 是 有保证的 在 这 全部 –40

°

c 至

+85

°

c 运行 范围 为 使容易 的 系统 设计.

特定的 函数 寄存器 (sfr)

一个 内部的 寄存器 是 有, 也 至 决定 addi-

tional 数据 涉及 这 ads7832, 或者 至 写 额外的

说明 至 这 转换器.

表格 ii 显示 这 数据 在 这 特定的 函数 寄存器 那

将 是 transferred 至 这 输出 总线 用 驱动 hbe 高

(和 sfr 高) 和 初始的 一个 读 循环 (驱动 rd

和 cs 低 和 wr 高.) 这 电源 失败 标记 在 这

sfr 是 设置 当 这 电源 供应 falls 在下 关于 2.7v.

这 标记 也 意思 那 一个 新 校准 有 被 started,

ads7832 提供 二 模式 为 读 这 转换

结果. 在 电源-向上, 这 转换器 是 设置 在 这 transparent

模式.

transparent 模式

这个 是 这 default 模式 为 ads7832. 在 这个 模式, 这

转换 decisions 从 这 successive approximation

寄存器 是 latched 在 这 输出 寄存器 作 它们 是 制造.

因此, 这 高 字节 (这 4 msbs) 能 是 读 之后 这 终止

的 这 ninth 时钟 循环 (five 时钟 循环 为 这 mux

安排好, 样本 acquisition 和 自动-zeroing 的 这 com-

parator, followed 用 这 四 时钟 循环 为 这 4msb

decisions.) 这 完全 12-位 数据 是 有 之后 busy

有 gone 高, 或者 这 内部的 状态 标记 变得 低 (d7

当 hbe 是 高).

latched 输出 模式

这个 模式 是 使活动 用 writing 一个 高 至 d0 在 这

特定的 函数 寄存器 和 cs 和 wr 低 和 sfr

和 hbe 高. (看 这 discussion 的 这 特定的 函数

寄存器 在下.)

在 这个 模式, 这 数据 从 一个 转换 是 latched 在 这

输出 缓存区 仅有的 之后 一个 转换 是 完全, 和

仍然是 那里 直到 这 next 转换 是 完成. 这

转换 结果 是 有效的 在 这 next 转换. 这个

准许 这 数据 至 是 读 甚至 之后 一个 新 转换 是

started, 为 faster 系统 throughput.

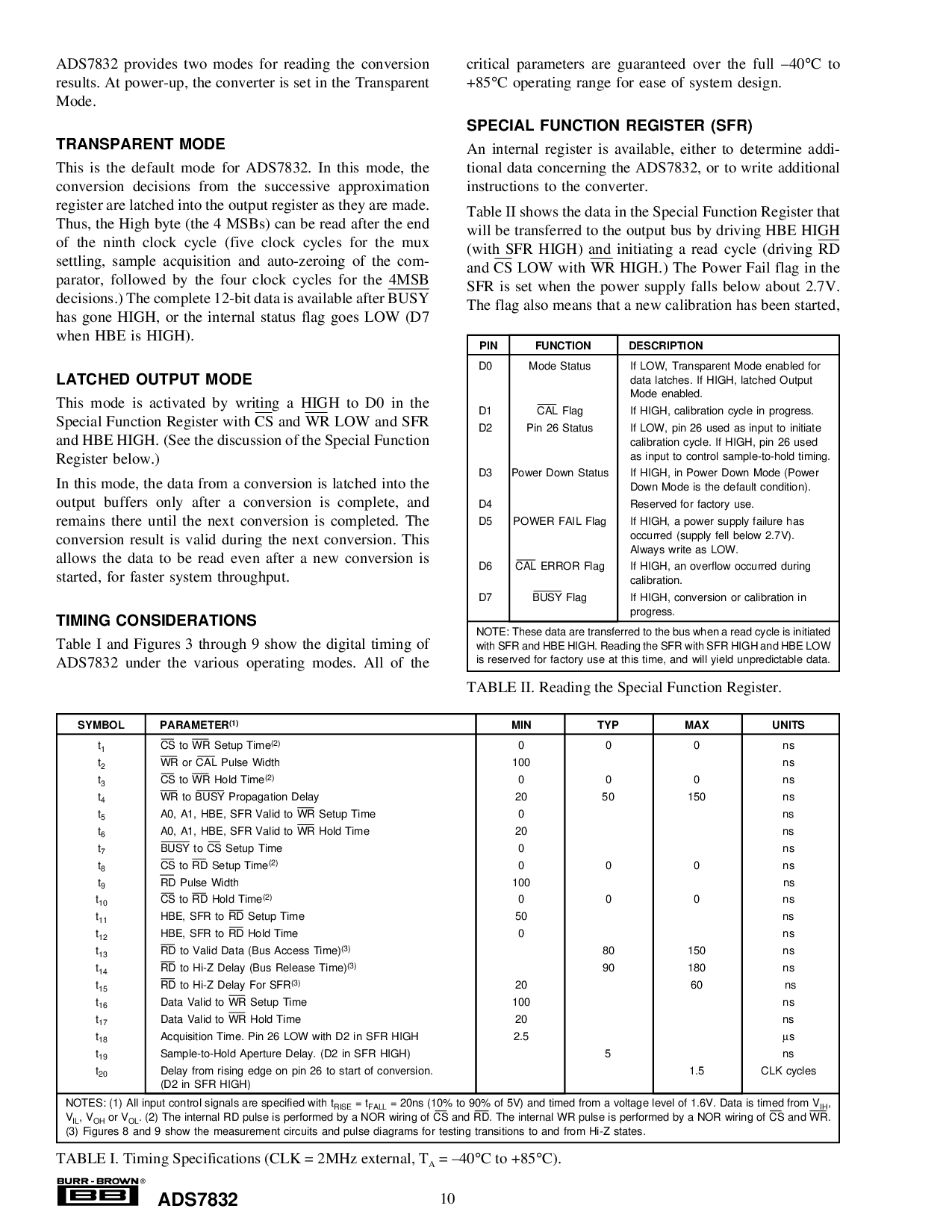

定时 仔细考虑

表格 i 和 计算数量 3 通过 9 显示 这 数字的 定时 的

ads7832 下面 这 各种各样的 运行 模式. 所有 的 这

表格 ii. 读 这 特定的 函数 寄存器.

标识 参数

(1)

最小值 典型值 最大值 单位

t

1

cs 至 wr 建制 时间

(2)

00 0 ns

t

2

wr 或者 cal 脉冲波 宽度 100 ns

t

3

cs 至 wr 支撑 时间

(2)

00 0 ns

t

4

wr 至 busy 传播 延迟 20 50 150 ns

t

5

a0, a1, hbe, sfr 有效的 至 wr 建制 时间 0 ns

t

6

a0, a1, hbe, sfr 有效的 至 wr 支撑 时间 20 ns

t

7

busy 至 cs 建制 时间 0 ns

t

8

cs 至 rd 建制 时间

(2)

00 0 ns

t

9

rd 脉冲波 宽度 100 ns

t

10

cs 至 rd 支撑 时间

(2)

00 0 ns

t

11

hbe, sfr 至 rd 建制 时间 50 ns

t

12

hbe, sfr 至 rd 支撑 时间 0 ns

t

13

rd 至 有效的 数据 (总线 进入 时间)

(3)

80 150 ns

t

14

rd 至 hi-z 延迟 (总线 释放 时间)

(3)

90 180 ns

t

15

rd 至 hi-z 延迟 为 sfr

(3)

20 60 ns

t

16

数据 有效的 至 wr 建制 时间 100 ns

t

17

数据 有效的 至 wr 支撑 时间 20 ns

t

18

acquisition 时间. 管脚 26 低 和 d2 在 sfr 高 2.5

µ

s

t

19

样本-至-支撑 aperture 延迟. (d2 在 sfr 高) 5 ns

t

20

延迟 从 rising 边缘 在 管脚 26 至 开始 的 转换. 1.5 clk 循环

(d2 在 sfr 高)

注释: (1) 所有 输入 控制 信号 是 指定 和 t

上升

= t

下降

= 20ns (10% 至 90% 的 5v) 和 安排时间 从 一个 电压 水平的 的 1.6v. 数据 是 安排时间 从 v

IH

,

V

IL

, v

OH

或者 v

OL

. (2) 这 内部的 rd 脉冲波 是 执行 用 一个 也不 线路 的 cs 和 rd. 这 内部的 wr 脉冲波 是 执行 用 一个 也不 线路 的 cs 和 wr.

(3) 计算数量 8 和 9 显示 这 度量 电路 和 脉冲波 图解 为 测试 transitions 至 和 从 hi-z states.

表格 i. 定时 规格 (clk = 2mhz 外部, t

一个

= –40

°

c 至 +85

°

c).