AD7679

rev. 0 | 页 8 的 28

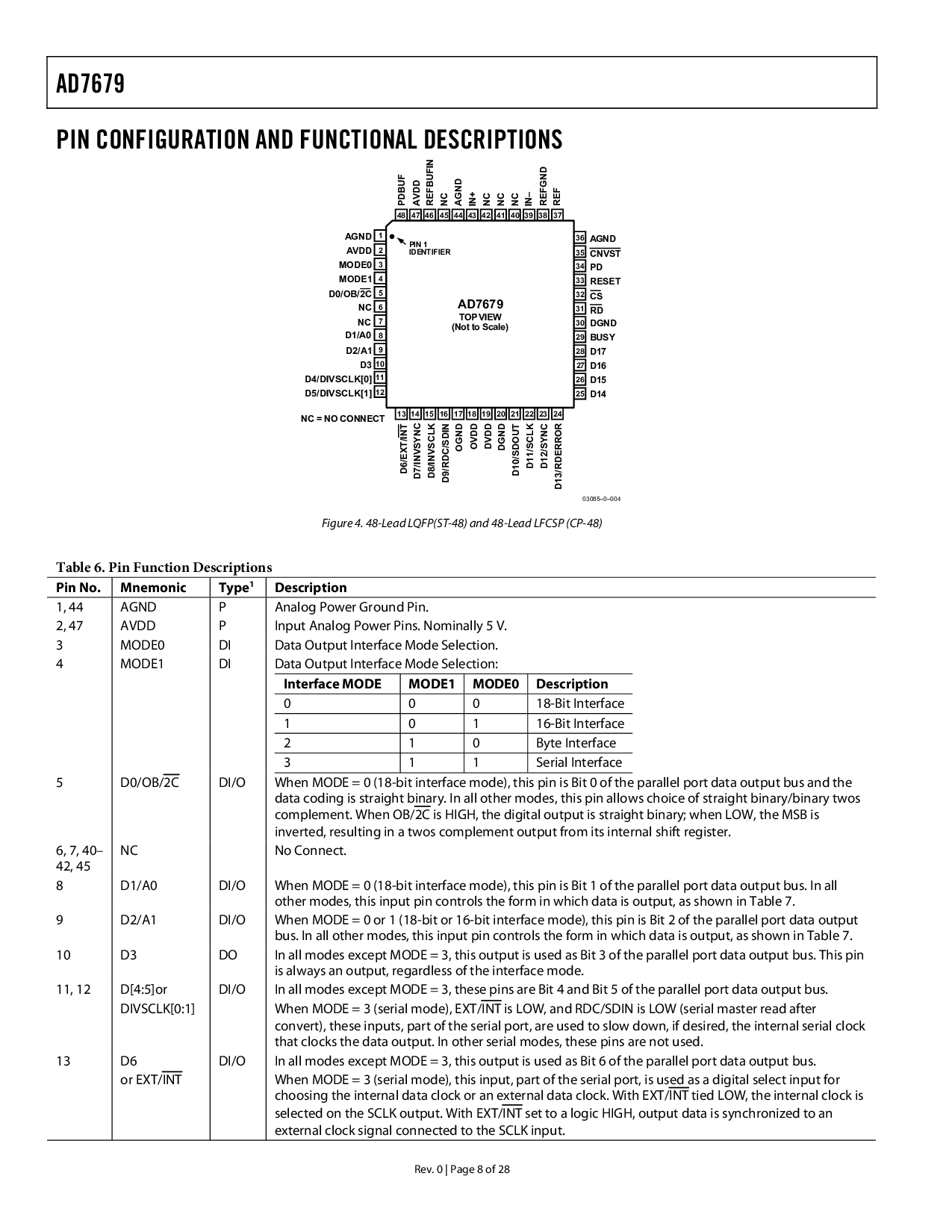

管脚 配置 和 functional 描述

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

48 47 46 45 44 39 38 3743 42 41 40

管脚 1

IDENTIFIER

顶 视图

(不 至 规模)

AGND

CNVST

PD

重置

CS

RD

DGND

AGND

AVDD

MODE0

MODE1

d0/ob/2c

NC

NC

NC = 非 连接

d1/a0

d2/a1

D3

d4/divsclk[0]

BUSY

D17

D16

D15

AD7679

d5/divsclk[1]

D14

PDBUF

AVDD

REFBUFIN

NC

AGND

IN+

NC

NC

NC

IN–

REFGND

REF

d6/ext/int

d7/invsync

d8/invsclk

d9/rdc/sdin

OGND

OVDD

DVDD

DGND

d10/sdout

d11/sclk

d12/同步

d13/rderror

03085–0–004

图示 4. 48-含铅的 lqfp(st-48) 和 48-含铅的 lfcsp (cp-48)

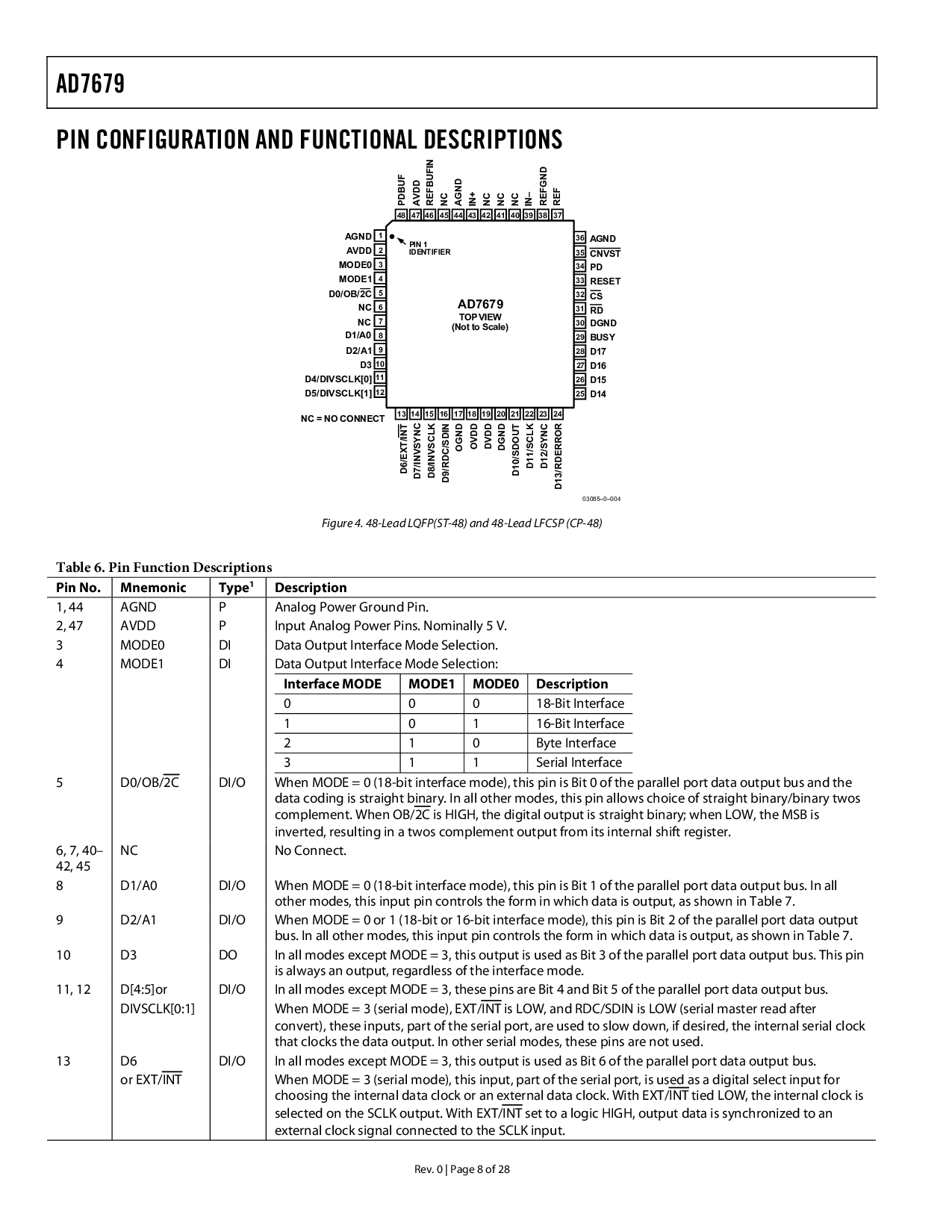

表格 6. 管脚 函数 描述

管脚 非. Mnemonic 类型

1

描述

1, 44 AGND P 相似物 电源 地面 管脚.

2, 47 AVDD P 输入 相似物 电源 管脚. nominally 5 v.

3 MODE0 DI 数据 输出 在terface 模式 选择.

4 MODE1 DI 数据 输出 interface 模式 选择:

接口 模式 MODE1 MODE0 描述

0 0 0 18-位 接口

1 0 1 16-位 接口

2 1 0 字节 接口

3 1 1 串行 接口

5

d0/ob/2c

di/o

当 模式 = 0 (18-位 接口 模式), 这个 管脚 是 位 0 的 这 并行的 端口数据 输出 总线 和 这

数据 编码 是 笔直地 二进制的. 在 所有 其它 模式, th是 管脚 准许 选择 的 笔直地 二进制的/二进制的 twos

complement. 当 ob/2c

是 高, 这 数字的 输出 是 straight 二进制的; 当 低, 这 msb 是

inverted, 结果 在 一个 twos complement输出 从 它的 内部的 变换 寄存器.

6, 7, 40–

42, 45

nc 非 连接.

8 d1/a0 di/o

当 模式 = 0 (18-位 接口 模式), 这个 管脚 是 位 1 的 这 并行的 端口数据 输出 总线. 在 所有

其它 模式, 这个 输入 管脚 控制 这 表格 在 这个 数据 是 输出, 作 显示 在 表格 7.

9 d2/a1 di/o

当 模式 = 0 或者 1 (18-位 或者 16-位 接口 模式),这个 管脚 是 位 2 的 这 并行的 端口 数据 输出

总线. 在 所有 其它 模式, 这个 输入 管脚 控制 这 form 在 这个 数据 是 output, 作 显示 在 表格 7.

10 d3 做

在 所有 模式 除了 模式 = 3, 这个输出 是 使用 作 位 3的 这 并行的 端口 data 输出 总线. 这个 管脚

是 总是 一个 输出, 关于较少 的 这 接口 模式.

11, 12 d[4:5]or

divsclk[0:1]

di/o 在 所有 模式 除了 模式 = 3, 这些 管脚 是位 4 和 位 5 的 这 parallel 端口 数据 输出 总线.

当 模式 = 3 (串行 模式), ext/int

是 低, 和 rdc/sdin 是 低 (串行 主控 读 之后

转变), 这些 输入, 部分 的 这 串行 端口, 是 使用至 慢 向下, 如果 desired, 这 内部的 串行 时钟

那 clocks 这 数据 output. 在 其它 串行 模式,这些 管脚 是 不 使用.

13 d6

或者 ext/int

di/o 在 所有 模式 除了 模式 = 3,这个 输出 是 使用 作 位 6 的这 并行的 端口数据 输出 总线.

当 模式 = 3 (串行 模式), 这个 在放, 部分 的 这 串行 端口, 是 使用 作 一个 数字的 选择 输入 为

choosing 这 内部的 数据 时钟 或者 一个外部 数据 clock. 和 ext/int

系 低, 这 内部的 时钟 是

选择 在 这 sclk 输出. 和 ext/int 设置 至 一个 逻辑 高, 输出 data 是 同步 至 一个

外部 时钟 信号 connected 至 这 sclk 输入.