rev. 0

–2–

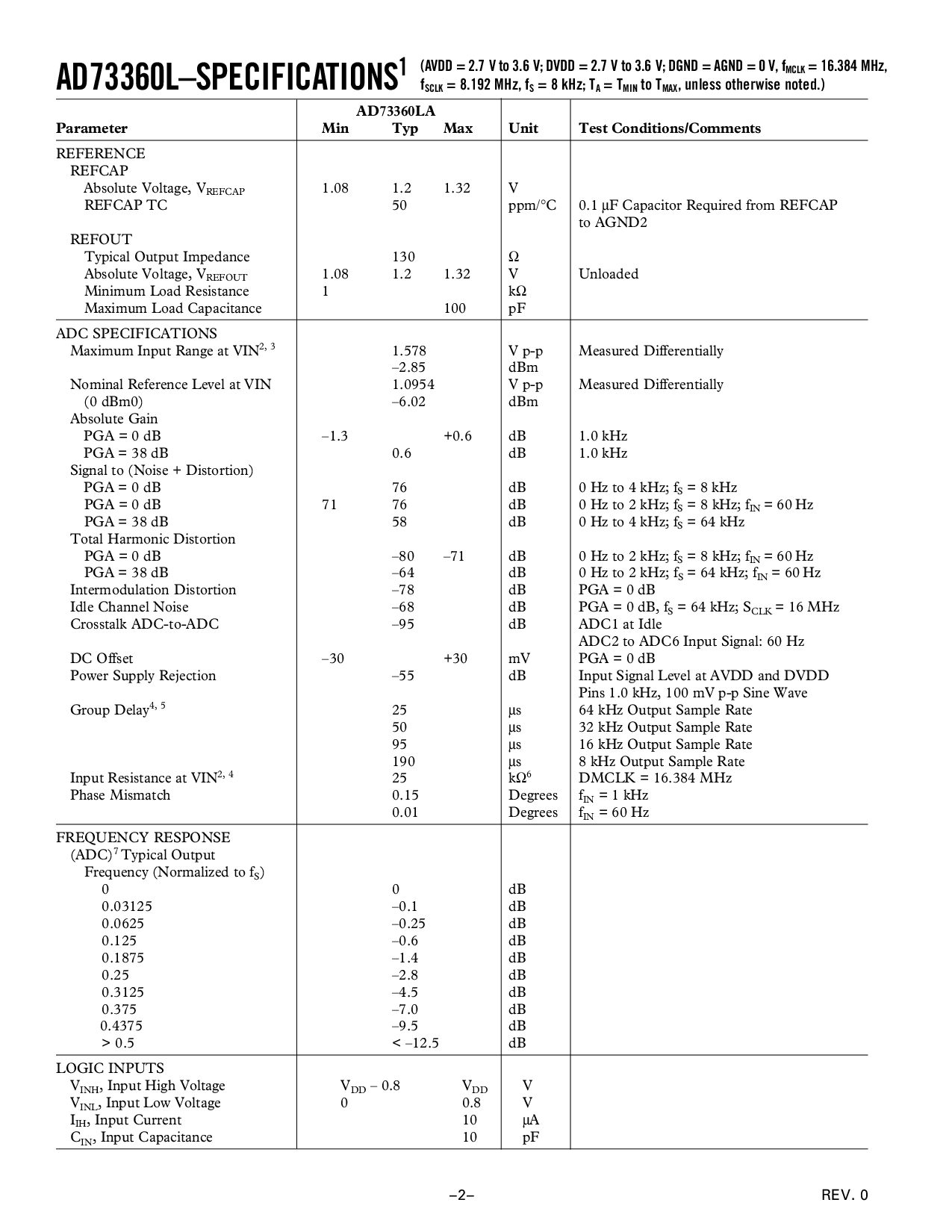

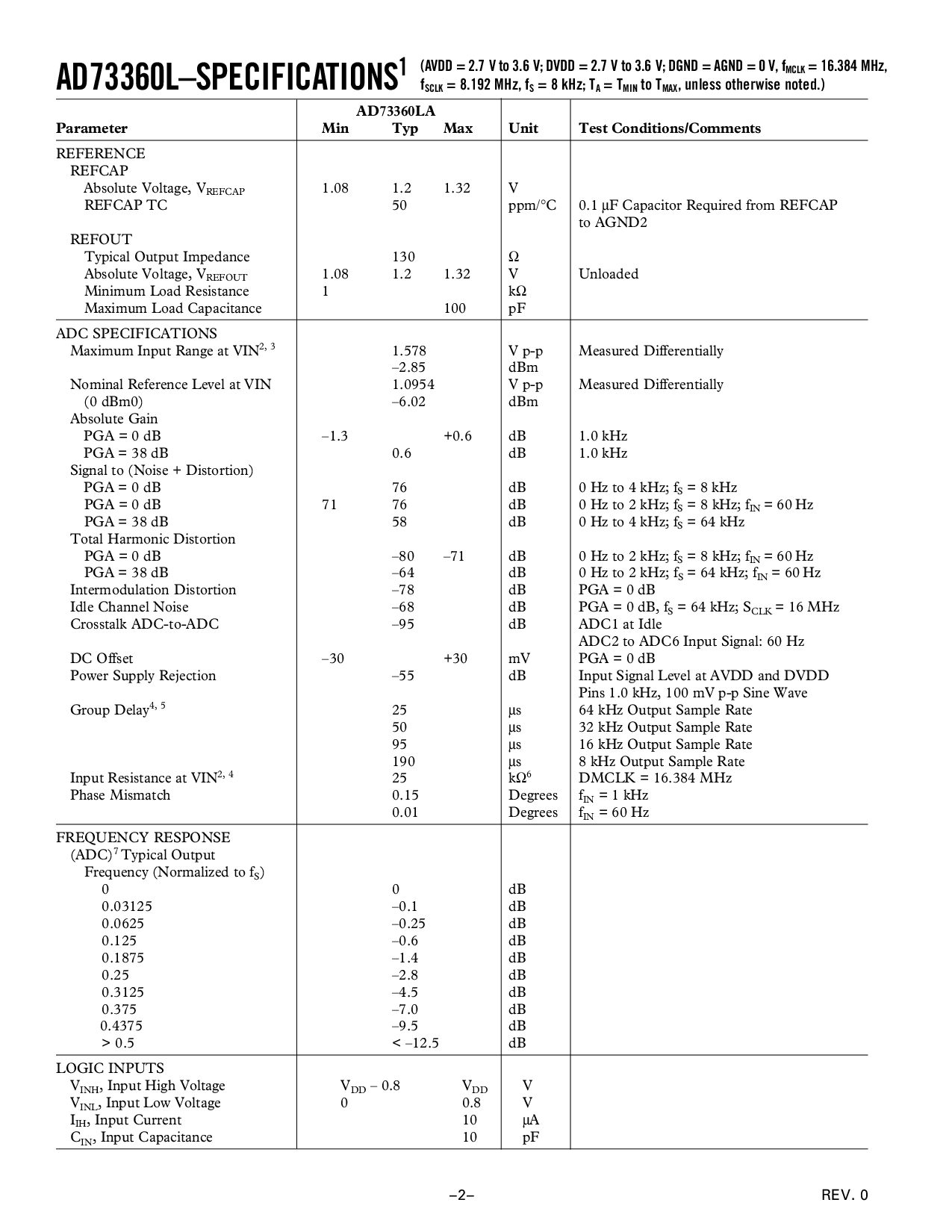

AD73360L–SPECIFICATIONS

1

(avdd = 2.7 v 至 3.6 v; dvdd = 2.7 v 至 3.6 v; dgnd = agnd = 0 v, f

MCLK

= 16.384 mhz,

f

SCLK

= 8.192 mhz, f

S

= 8 khz; t

一个

= t

最小值

至 t

最大值

, 除非 否则 指出.)

AD73360LA

参数 最小值 典型值 最大值 单位 测试 情况/comments

涉及

REFCAP

绝对 电压, v

REFCAP

1.08 1.2 1.32 V

refcap tc 50 ppm/

°

C 0.1

µ

f 电容 必需的 从 refcap

至 agnd2

REFOUT

典型 输出 阻抗 130

Ω

绝对 电压, v

REFOUT

1.08 1.2 1.32 V Unloaded

最小 加载 阻抗 1 k

Ω

最大 加载 电容 100 pF

模数转换器 规格

最大 输入 范围 在 vin

2, 3

1.578 v p-p 量过的 differentially

–

2.85 dBm

名义上的 涉及 水平的 在 vin 1.0954 v p-p 量过的 differentially

(0 dbm0)

–

6.02 dBm

绝对 增益

pga = 0 db

–

1.3 +0.6 dB 1.0 khz

pga = 38 db 0.6 dB 1.0 khz

信号 至 (噪音 + 扭曲量)

pga = 0 db 76 dB 0 hz 至 4 khz; f

S

= 8 khz

pga = 0 db 71 76 dB 0 hz 至 2 khz; f

S

= 8 khz; f

在

= 60 Hz

pga = 38 db 58 dB 0 hz 至 4 khz; f

S

= 64 khz

总的 调和的 扭曲量

pga = 0 db

–

80

–

71 dB 0 hz 至 2 khz; f

S

= 8 khz; f

在

= 60 Hz

pga = 38 db

–

64 dB 0 hz 至 2 khz; f

S

= 64 khz; f

在

= 60 Hz

交调 扭曲量

–

78 dB pga = 0 db

空闲 频道 噪音

–

68 dB pga = 0 db, f

S

= 64 khz; s

CLK

= 16 MHz

串扰 模数转换器-至-模数转换器

–

95 dB adc1 在 空闲

adc2 至 adc6 输入 信号: 60 hz

直流 补偿

–

30 +30 mV pga = 0 db

电源 供应 拒绝

–

55 dB 输入 信号 水平的 在 avdd 和 dvdd

管脚 1.0 khz, 100 mv p-p sine 波

组 延迟

4, 5

25

µ

s 64 khz 输出 样本 比率

50

µ

s 32 khz 输出 样本 比率

95

µ

s 16 khz 输出 样本 比率

190

µ

s 8 khz 输出 样本 比率

输入 阻抗 在 vin

2, 4

25 k

Ω

6

dmclk = 16.384 mhz

阶段 mismatch 0.15 Degrees f

在

= 1 khz

0.01 Degrees f

在

= 60 hz

频率 回馈

(模数转换器)

7

典型 输出

频率 (normalized 至 f

S

)

00dB

0.03125

–

0.1 dB

0.0625

–

0.25 dB

0.125

–

0.6 dB

0.1875

–

1.4 dB

0.25

–

2.8 dB

0.3125

–

4.5 dB

0.375

–

7.0 dB

0.4375

–

9.5 dB

> 0.5 <

–

12.5 dB

逻辑 输入

V

INH

, 输入 高 电压 V

DD

–

0.8 V

DD

V

V

INL

, 输入 低 电压 0 0.8 V

I

IH

, 输入 电流 10

µ

一个

C

在

, 输入 电容 10 pF