1

ispGDX

TM

160v/va

在-系统 可编程序的

3.3v generic 数字的 crosspoint

TM

函数的 块 图解特性

• 在-系统 可编程序的 generic 数字的

crosspoint 家族

— 先进的 architecture 地址 可编程序的

pcb interconnect, 总线 接口 integration 和

跳越者/转变 替换

— “any 输入 至 任何 output” routing

— fixed 高 或者 低 输出 选项 为 跳越者/插件

转变 emulation

— 空间-节省 pqfp 和 bga 包装

— 专心致志的 ieee 1149.1-一致的 boundary scan

测试

• 高 效能 e

2

CMOS

®

技术

— 3.3v 核心 电源 供应

— 3.5ns 输入-至-输出/3.5ns 时钟-至-输出 delay*

— 250mhz 最大 时钟 frequency*

— ttl/3.3v/2.5v 兼容 输入 门槛 和

输出 水平 (individually 可编程序的)*

— 低-电源: 16.5ma 安静的 icc*

— 24ma i

OL

驱动 和 可编程序的 回转 比率

控制 选项

— pci 兼容 驱动 capability*

— 施密特 触发 输入 为 噪音 免除

— 用电气 可擦掉的 和 reprogrammable

— 非-易变的 e

2

cmos 技术

• ispgdxv™ 提供 这 下列的 有利因素

— 3.3v 在-系统 可编程序的 使用 boundary scan

测试 进入 端口 (tap)

— 改变 interconnects 在 秒

• 有伸缩性的 architecture

— combinatorial/latched/注册 输入 或者 输出

— 单独的 i/o 触发-状态 控制 和 极性 控制

— 专心致志的 时钟/时钟 使能 输入 管脚 (四) 或者

可编程序的 clocks/时钟 使能 从 i/o 管脚

(40)

— 单独的 水平的 4:1 动态 path 选择(tpd = 3.5ns)

— 可编程序的 宽-mux cascade 特性

支持 向上 至 16:1 mux

— 可编程序的 拉-ups, 总线 支撑 获得 和 打开

流 在 i/o 管脚

— 输出 触发-状态 在 电源-向上 (“live insertion”

friendly)

• 设计 支持 通过 lattice’s ispgdx

开发 软件

— ms windows 或者 nt / pc-为基础 或者 sun o/s

— 容易 text-为基础 设计 entry

— 自动 信号 routing

— 程序 向上 至 100 isp 设备 concurrently

— simulator netlist 一代 为 容易 板-水平的

Simulation

* “va” 版本 仅有的

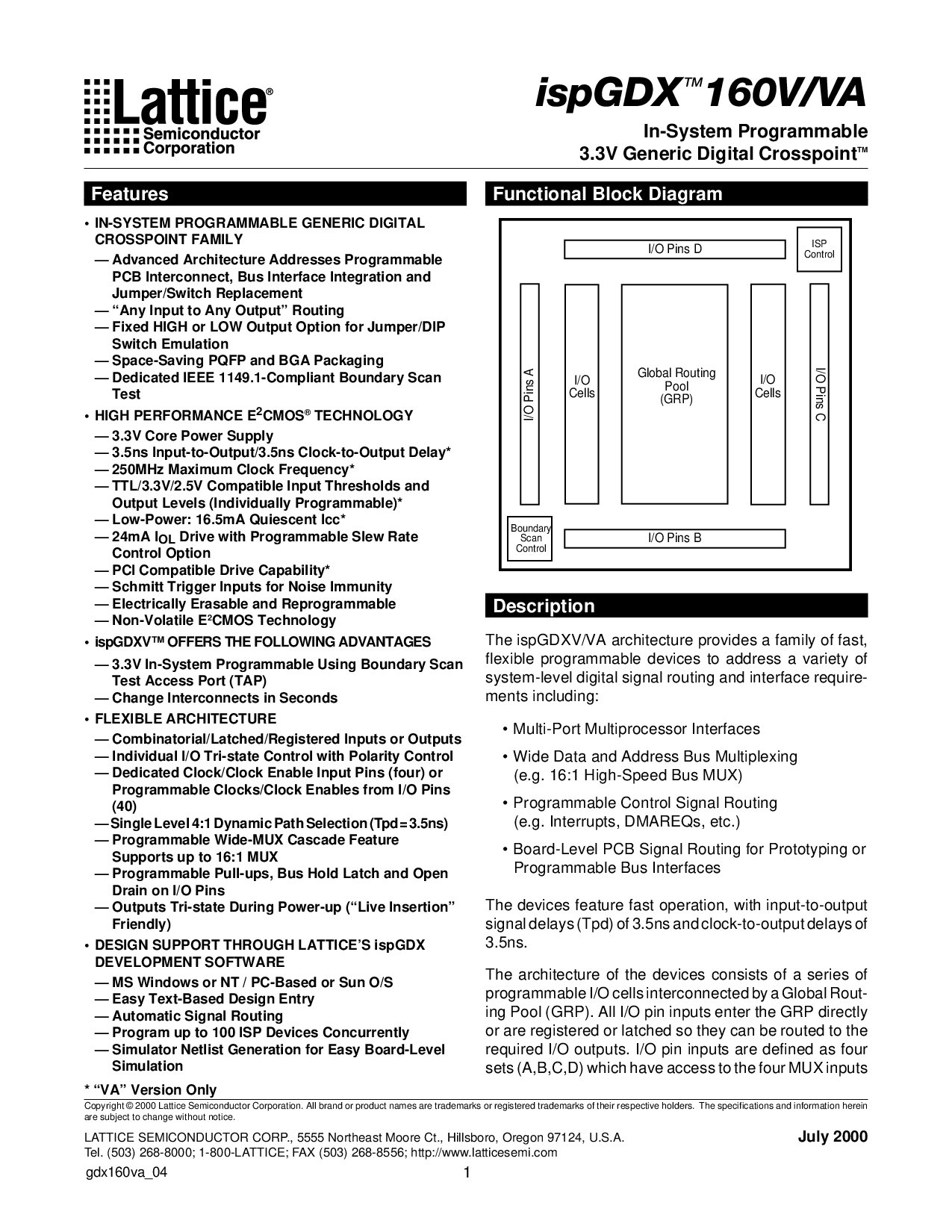

global routing

Pool

(grp)

i/o

Cells

i/o 管脚 b

Boundary

Scan

控制

i/o

Cells

ISP

控制

i/o 管脚 一个

i/o 管脚 c

i/o 管脚 d

描述

这 ispgdxv/va architecture 提供 一个 家族 的 快,

有伸缩性的 可编程序的 设备 至 地址 一个 多样性 的

系统-水平的 数字的 信号 routing 和 接口 需要-

ments 包含:

• multi-端口 multiprocessor 接口

• 宽 数据 和 地址 总线 multiplexing

(e.g. 16:1 高-速 总线 mux)

• 可编程序的 控制 信号 routing

(e.g. 中断, dmareqs, 等.)

• 板-水平的 pcb 信号 routing 为 prototyping 或者

可编程序的 总线 接口

这 设备 特性 快 运作, 和 输入-至-输出

信号 延迟 (tpd) 的 3.5ns 和 时钟-至-输出 延迟 的

3.5ns.

这 architecture 的 这 设备 组成 的 一个 序列 的

可编程序的 i/o cells interconnected 用 一个 global rout-

ing pool (grp). 所有 i/o 管脚 输入 enter 这 grp 直接地

或者 是 注册 或者 latched 所以 它们 能 是 routed 至 这

必需的 i/o 输出. i/o 管脚 输入 是 定义 作 四

sets (一个,b,c,d) 这个 有 进入 至 这 四 mux 输入

gdx160va_04

版权 © 2000 lattice 半导体 公司. 所有 brand 或者 产品 names 是 商标 或者 注册 商标 的 它们的 各自的 holders. 这 规格 和 信息 在此处

是 主题 至 改变 没有 注意.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

july 2000

电话. (503) 268-8000; 1-800-lattice; 传真 (503) 268-8556; http://www.latticesemi.com