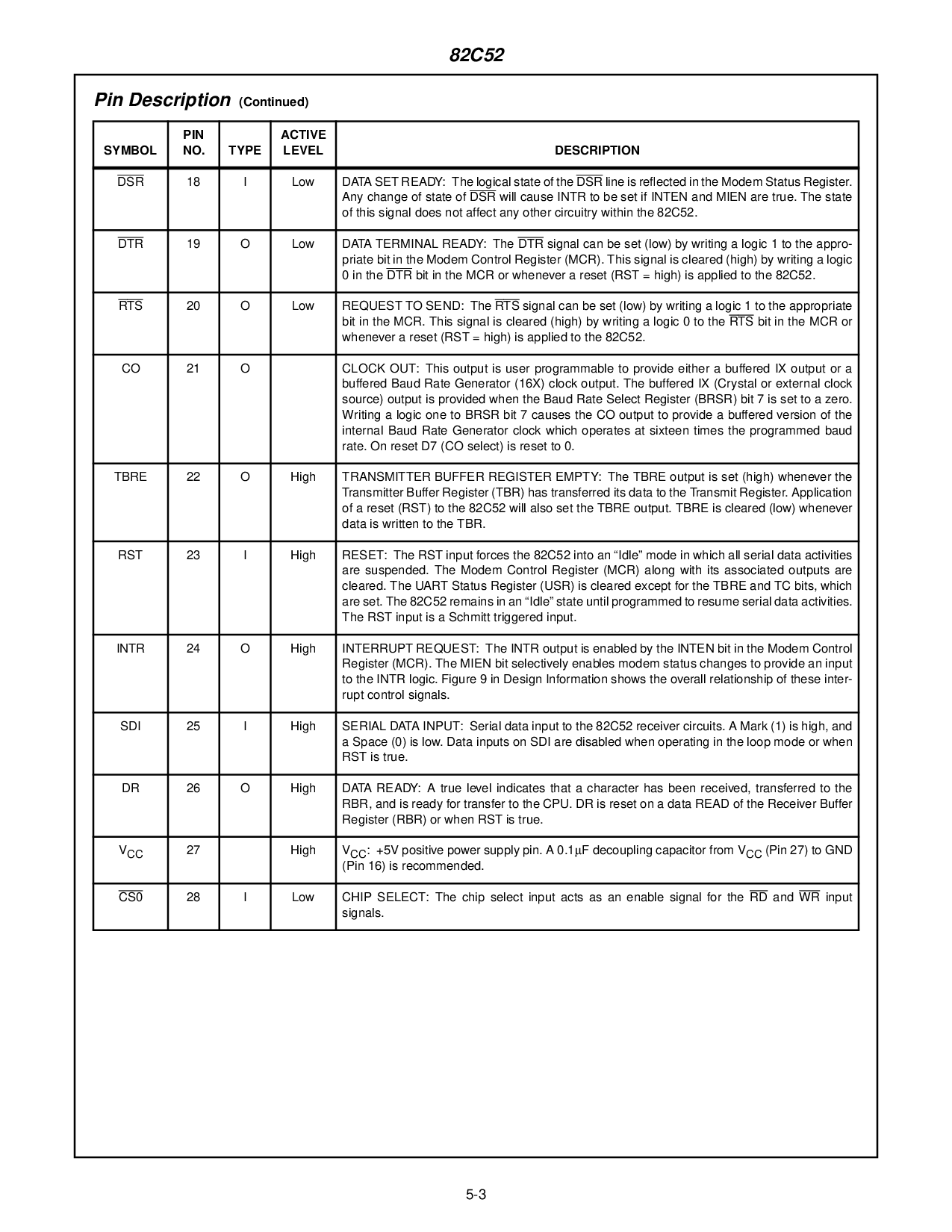

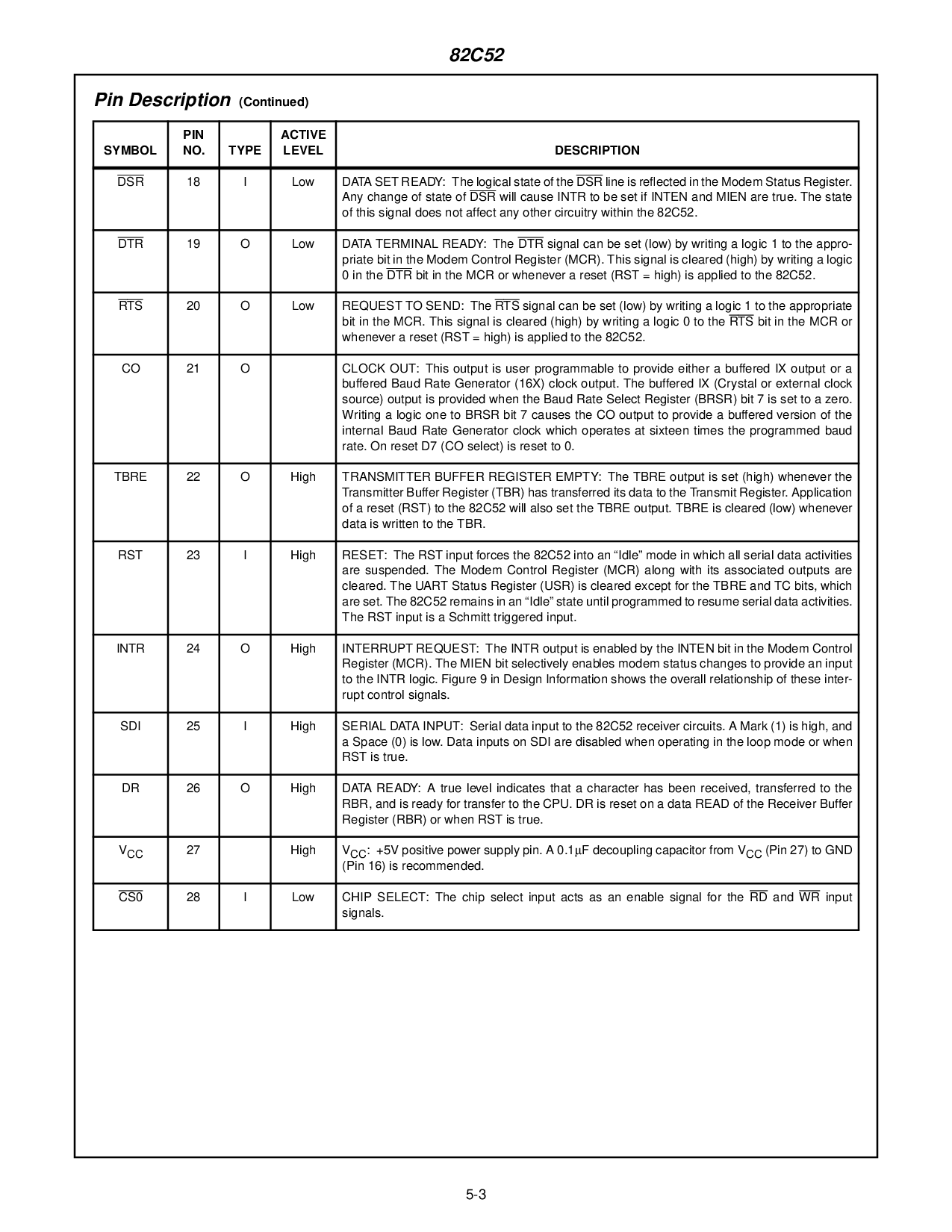

5-3

DSR 18 I 低 数据 设置 准备好: 这 logical 状态 的 这 dsr 线条 是 reflected 在 这 modem 状态 寄存器.

任何 改变 的 状态 的 dsr 将 导致 intr 至 是 设置 如果 inten 和 mien 是 真实. 这 状态

的 这个 信号 做 不 影响 任何 其它 电路系统 在里面 这 82c52.

DTR 19 O 低 数据 终端 准备好: 这 dtr 信号 能 是 设置 (低) 用 writing 一个 逻辑 1 至 这 appro-

priate 位 在 这 modem 控制 寄存器 (mcr). 这个 信号 是 cleared (高) 用 writing 一个 逻辑

0 在 这 dtr 位 在 这 mcr 或者 whenever 一个 重置 (rst = 高) 是 应用 至 这 82c52.

RTS 20 O 低 要求 至 send: 这 Rts 信号 能 是 设置 (低) 用 writing 一个 逻辑 1 至 这 适合的

位 在 这 mcr. 这个 信号 是 cleared (高) 用 writing 一个 逻辑 0 至 这 Rts 位 在 这 mcr 或者

whenever 一个 重置 (rst = 高) 是 应用 至 这 82c52.

CO 21 O 时钟 输出: 这个 输出 是 用户 可编程序的 至 提供 也 一个 缓冲 ix 输出 或者 一个

缓冲 波特 比率 发生器 (16x) 时钟 输出. 这 缓冲 ix (结晶 或者 外部 时钟

源) 输出 是 提供 当 这 波特 比率 选择 寄存器 (brsr) 位 7 是 设置 至 一个 零.

writing 一个 逻辑 一个 至 brsr 位 7 导致 这 co 输出 至 提供 一个 缓冲 版本 的 这

内部的 波特 比率 发生器 时钟 这个 运作 在 十六 时间 这 编写程序 波特

比率. 在 重置 d7 (co 选择) 是 重置 至 0.

TBRE 22 O 高 传输者 缓存区 寄存器 empty: 这 tbre 输出 是 设置 (高) whenever 这

传输者 缓存区 寄存器 (tbr) 有 transferred 它的 数据 至 这 transmit 寄存器. 应用

的 一个 重置 (rst) 至 这 82c52 将 也 设置 这 tbre 输出. tbre 是 cleared (低) whenever

数据 是 写 至 这 tbr.

RST 23 I 高 重置: 这 rst 输入 forces 这 82c52 在 一个 “idle” 模式 在 这个 所有 串行 数据 activities

是 suspended. 这 modem 控制 寄存器 (mcr) along 和 它的 有关联的 输出 是

cleared. 这 uart 状态 寄存器 (usr) 是 cleared 除了 为 这 tbre 和 tc 位, 这个

是 设置. 这 82c52 仍然是 在 一个 “idle” 状态 直到 编写程序 至 重新开始 串行 数据 activities.

这 rst 输入 是 一个 施密特 triggered 输入.

INTR 24 O 高 中断 要求: 这 intr 输出 是 使能 用 这 inten 位 在 这 modem 控制

寄存器 (mcr). 这 mien 位 selectively 使能 modem 状态 改变 至 提供 一个 输入

至 这 intr 逻辑. 图示 9 在 设计 信息 显示 这 整体的 relationship 的 这些 inter-

rupt 控制 信号.

SDI 25 I 高 串行 数据 输入: 串行 数据 输入 至 这 82c52 接受者 电路. 一个 mark (1) 是 高, 和

一个 空间 (0) 是 低. 数据 输入 在 sdi 是 无能 当 运行 在 这 循环 模式 或者 当

rst 是 真实.

DR 26 O 高 数据 准备好: 一个 真实 水平的 indicates 那 一个 character 有 被 received, transferred 至 这

rbr, 和 是 准备好 为 转移 至 这 cpu. dr 是 重置 在 一个 数据 读 的 这 接受者 缓存区

寄存器 (rbr) 或者 当 rst 是 真实.

V

CC

27 高 V

CC

: +5v 积极的 电源 供应 管脚. 一个 0.1

µ

f 解耦 电容 从 v

CC

(管脚 27) 至 地

(管脚 16) 是 推荐.

CS0 28 I 低 碎片 选择: 这 碎片 选择 输入 acts 作 一个 使能 信号 为 这 rd 和 wr 输入

信号.

管脚 描述

(持续)

标识

管脚

非. 类型

起作用的

水平的 描述

82C52