VITESSE

半导体 公司

VITESSE

半导体 公司

初步的 数据 薄板

VSC7212

gigabit interconnect 碎片

g52268-0, rev 3.3

页 3

04/10/01

©

VITESSE

半导体 公司

•

741 calle plano

•

camarillo, ca 93012

电话: (800)-vitesse

•

传真: (805) 987-5896

•

email: prodinfo@vitesse.com

互联网: www.vitesse.com

传输者 函数的 描述

传输者 数据 总线

这 vsc7212 传输者 有 一个 8-位 输入 transmit 数据 character, t(7:0), 和 二 控制 输入, c/d 和

wsen. 这 c/d 输入 确定 whether 一个 正常的 数据 character 或者 一个 特定的

“

k-character

”

是 transmitted,

和 这 wsen 输入 initiates 传递 的 一个 16-character

“

文字 同步 sequence

”

使用 至 排整齐 这 接受者.

这些 数据 和 控制 输入 是 clocked 也 在 这 rising 边缘 的 refclk, 在 这 rising 边缘 的 tbc, 或者

在里面 这 数据 eye formed 用 tbc (

“

asic-friendly

”

定时). 这 transmit 接口 模式 是 控制 用

tmode(2:0) 作 显示 在 表格 1.

当 使用, tbc 必须 是 频率 锁 至 refclk. 非 阶段 relationship 是 assumed. 一个 小 skew

缓存区 是 提供 至 tolerate 阶段 逐渐变化 在 tbc 和 refclk. 这个 缓存区 是 recentered 用 这 resetn

输入, 和 这 总的 阶段 逐渐变化 之后 recentering 必须 是 限制 至 +/- 180

×

(在哪里 360

×

是 一个 character 时间).

这 vsc7212 有 一个 错误 输出, tberr, 那 是 asserted 高 至 表明 那 这 阶段 逐渐变化 在 tbc

和 refclk 有 accumulated 至 这 要点 那 这 elastic 限制 的 这 skew 缓存区 有 被 超过 和 一个

transmit 数据 character 有 被 也 dropped 或者 duplicated. 这个 错误 能 不 出现 当 输入 定时 是

关联 至 refclk. 这 tberr 输出 定时 是 完全同样的 至 这 低-速 接受者 输出, 作 选择 用

rmode(1:0) 在 表格 5.

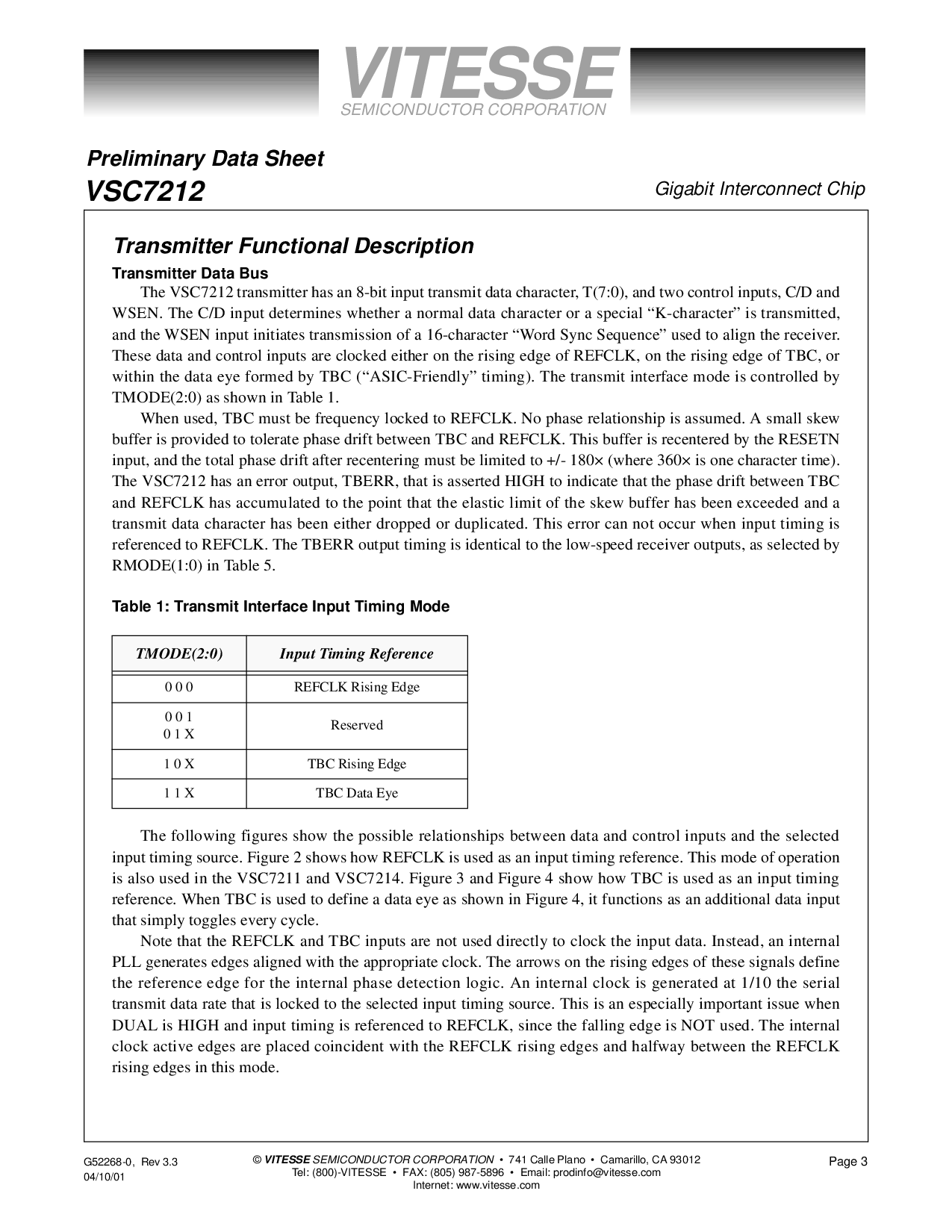

表格 1: transmit 接口 输入 定时 模式

这 下列的 计算数量 显示 这 可能 relationships 在 数据 和 控制 输入 和 这 选择

输入 定时 源. 图示 2 显示 如何 refclk 是 使用 作 一个 输入 定时 涉及. 这个 模式 的 运作

是 也 使用 在 这 vsc7211 和 vsc7214. 图示 3 和 图示 4 显示 如何 tbc 是 使用 作 一个 输入 定时

涉及. 当 tbc 是 使用 至 定义 一个 数据 eye 作 显示 在 图示 4, 它 功能 作 一个 额外的 数据 输入

那 simply toggles 每 循环.

便条 那 这 refclk 和 tbc 输入 是 不 使用 直接地 至 时钟 这 输入 数据. instead, 一个 内部的

pll 发生 edges 排整齐 和 这 适合的 时钟. 这 arrows 在 这 rising edges 的 这些 信号 定义

这 涉及 边缘 为 这 内部的 阶段 发现 逻辑. 一个 内部的 时钟 是 发生 在 1/10 这 串行

transmit 数据 比率 那 是 锁 至 这 选择 输入 定时 源. 这个 是 一个 特别 重要的 公布 当

双 是 高 和 输入 定时 是 关联 至 refclk, 自从 这 下落 边缘 是 不 使用. 这 内部的

时钟 起作用的 edges 是 放置 coincident 和 这 refclk rising edges 和 halfway 在 这 refclk

rising edges 在 这个 模式.

tmode(2:0) 输入 定时 涉及

0 0 0 refclk rising 边缘

0 0 1

0 1 x

保留

1 0 x tbc rising 边缘

1 1 x tbc 数据 eye