4/29

¡ 半导体

msm80c85ahrs/gs/js

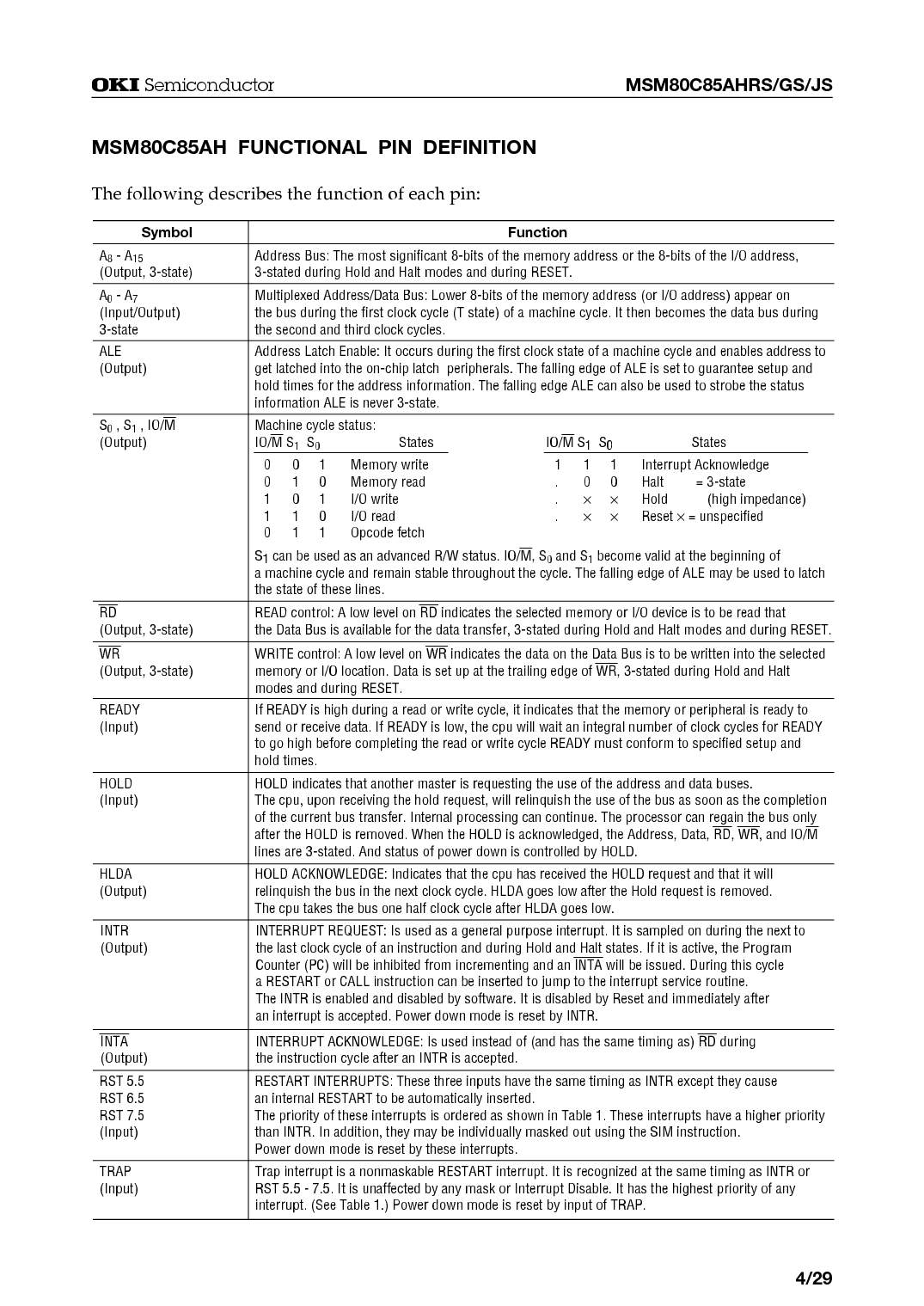

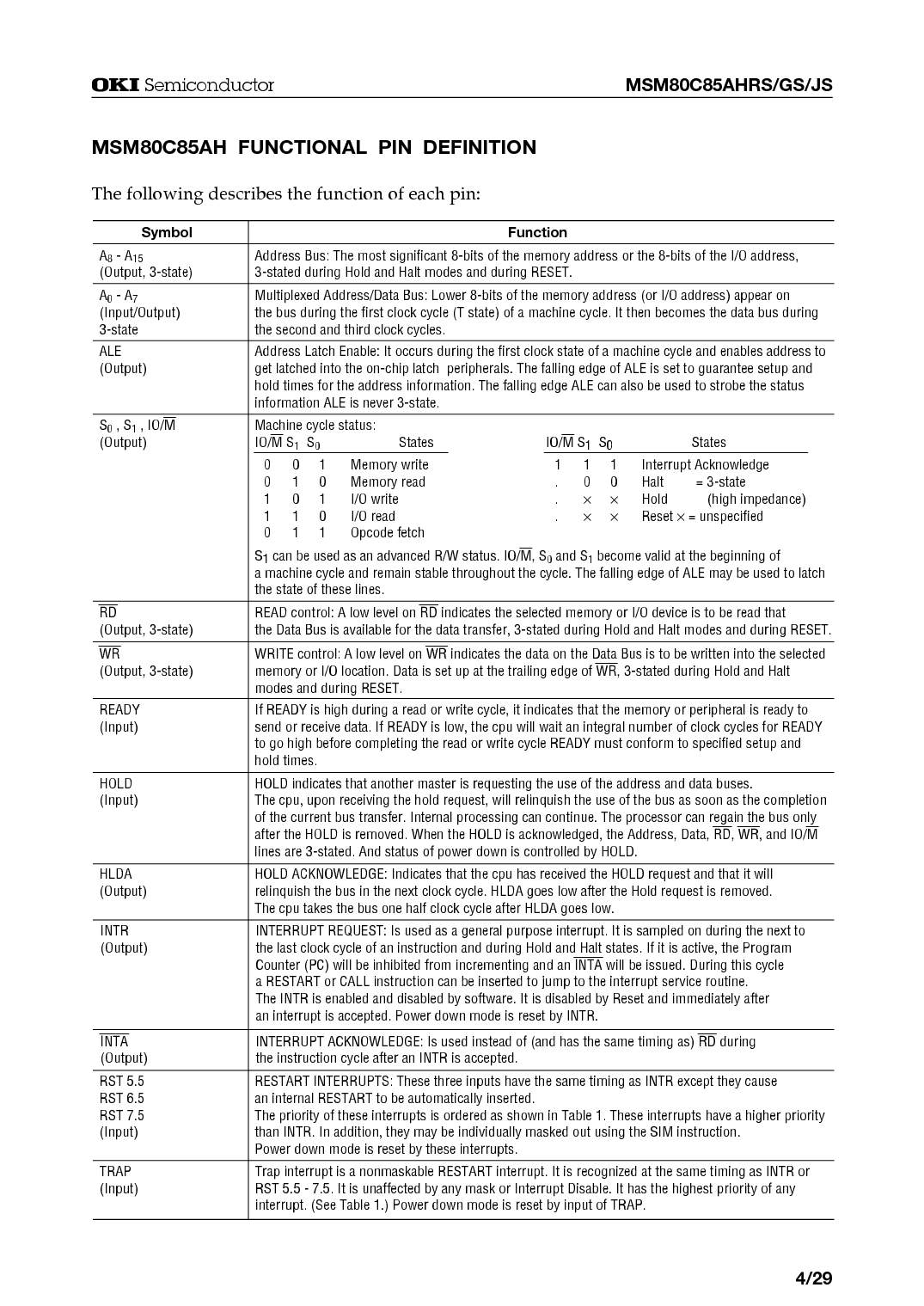

msm80c85ah 函数的 管脚 定义

这 下列的 describes 这 函数 的 各自 管脚:

一个

0

- 一个

7

(输入/输出)

3-状态

一个

8

- 一个

15

(输出, 3-状态)

多路复用 地址/数据 总线: 更小的 8-位 的 这 记忆 地址 (或者 i/o address) 呈现 在

这 总线 在 这 第一 时钟 循环 (t 状态) 的 一个 机器 循环. 它 然后 变为 这 数据 总线 在

这 第二 和 第三 时钟 循环.

地址 总线: 这 大多数 重大的 8-位 的 这 记忆 地址 或者 这 8-位 的 这 i/o address,

3-陈述 在 支撑 和 halt 模式 和 在 重置.

标识 函数

ALE

(输出)

地址 获得 使能: 它 occurs 在 这 第一 时钟 状态 的 一个 机器 循环 和 使能 地址 至

得到 latched 在 这 在-碎片 获得 peripherals. 这 下落 边缘 的 ale 是 设置 至 保证 建制 和

支撑 时间 为 这 地址 信息. 这 下落 边缘 ale 能 也 是 使用 至 strobe 这 状态

信息 ale 是 从不 3-状态.

S

0

, s

1

, io/

M

(输出)

机器 循环 状态:

io/

M

S

1

S

0

States

S

1

能 是 使用 作 一个 先进的 r/w 状态. io/

M

, s

0

和 s

1

变为 有效的 在 这 beginning 的

一个 机器 循环 和 仍然是 稳固的 全部地 这 循环. 这 下落 边缘 的 ale 将 是 使用 至 获得

这 状态 的 这些 线条.

RD

(输出, 3-状态)

读 控制: 一个 低 水平的 在

RD

indicates 这 选择 记忆 或者 i/o 设备 是 至 是 读 那

这 数据 总线 是 有 为 这 数据 转移, 3-陈述 在 支撑 和 halt 模式 和 在 重置.

WR

(输出, 3-状态)

写 控制: 一个 低 水平的 在

WR

indicates 这 数据 在 这 数据 总线 是 至 是 写 在 这 选择

记忆 或者 i/o location. 数据 是 设置 向上 在 这 trailing 边缘 的

WR

, 3-陈述 在 支撑 和 halt

模式 和 在 重置.

准备好

(输入)

如果 准备好 是 高 在 一个 读 或者 写 循环, 它 indicates 那 这 记忆 或者 附带的 是 准备好 至

send 或者 receive 数据. 如果 准备好 是 低, 这 cpu 将 wait 一个 integral 号码 的 时钟 循环 为 准备好

至 go 高 在之前 完成 这 读 或者 写 循环 准备好 必须 遵从 至 指定 建制 和

支撑 时间.

支撑

(输入)

HLDA

(输出)

支撑 acknowledge: indicates 那 这 cpu 有 received 这 支撑 要求 和 那 它 将

relinquish 这 总线 在 这 next 时钟 循环. hlda 变得 低 之后 这 支撑 要求 是 移除.

这 cpu takes 这 总线 一个 half 时钟 循环 之后 hlda 变得 低.

支撑 indicates 那 另一 主控 是 requesting 这 使用 的 这 地址 和 数据 buses.

这 cpu, 在之上 接到 这 支撑 要求, 将 relinquish 这 使用 的 这 总线 作 soon 作 这 completion

的 这 电流 总线 转移. 内部的 处理 能 continue. 这 处理器 能 regain 这 总线 仅有的

之后 这 支撑 是 移除. 当 这 支撑 是 acknowledged, 这 地址, 数据,

RD

,

WR

, 和 io/

M

线条 是 3-陈述. 和 状态 的 电源 向下 是 控制 用 支撑.

INTR

(输出)

中断 要求: 是 使用 作 一个 一般 目的 中断. 它 是 抽样 在 在 这 next 至

这 last 时钟 循环 的 一个 操作指南 和 在 支撑 和 halt states. 如果 它 是 起作用的, 这 程序

计数器 (pc) 将 是 inhibited 从 incrementing 和 一个

INTA

将 是 issued. 在 这个 循环

一个 重新开始 或者 call 操作指南 能 是 inserted 至 jump 至 这 中断 维护 routine.

这 intr 是 使能 和 无能 用 软件. 它 是 无能 用 重置 和 立即 之后

一个 中断 是 accepted. 电源 向下 模式 是 重置 用 intr.

INTA

(输出)

中断 acknowledge: 是 使用 instead 的 (和 有 这 一样 定时 作)

RD

在

这 操作指南 循环 之后 一个 intr 是 accepted.

rst 5.5

rst 6.5

rst 7.5

(输入)

重新开始 中断: 这些 三 输入 有 这 一样 定时 作 intr 除了 它们 导致

一个 内部的 重新开始 至 是 automatically inserted.

这 priority 的 这些 中断 是 ordered 作 显示 在 表格 1. 这些 中断 有 一个 高等级的 priority

比 intr. 在 增加, 它们 将 是 individually masked 输出 使用 这 sim 操作指南.

电源 向下 模式 是 重置 用 这些 中断.

TRAP

(输入)

trap 中断 是 一个 nonmaskable 重新开始 中断. 它 是 公认的 在 这 一样 定时 作 intr 或者

rst 5.5 - 7.5. 它 是 unaffected 用 任何 掩饰 或者 中断 使不能运转. 它 有 这 最高的 priority 的 任何

中断. (看 表格 1.) 电源 向下 模式 是 重置 用 输入 的 trap.

0

0

1

1

0

0

1

0

1

1

1

0

1

0

1

记忆 写

记忆 读

i/o 写

i/o 读

opcode fetch

io/

M

S

1

S

0

States

1

.

.

.

1

0

¥

¥

1

0

¥

¥

中断 acknowledge

halt = 3-状态

支撑 (高 阻抗)

重置

¥

= 未说明的