30 程序编制 和 Resetting

预定的 至 这 多样性 在 电源 供应 电源-向上 times 这

内部的 电源 向上 重置 电路 将 不 工作 在 每 design

therefore 一个 外部 重置 必须 是 执行 在之前

这 DRAM 控制 能 是 编写程序 和 used

之后 going 通过 这 重置 procedure 这

DP8420A21A22A 能 是 编写程序 用 也 的 二

methods 模式 加载 仅有的 程序编制 或者 碎片 选择 交流-

cess Programming 之后 程序编制 这 DRC 为 这 第一

时间 之后 reset 这 碎片 enters 一个 60 ms initialization period

在 这个 时期 这 控制 执行 refreshes 每

13

m

sor15

m

s 这个 制造 更远 DRAM warm 向上 循环

unnecessary 之后 这个 平台 这 碎片 能 是 repro-

grammed 作 许多 时间 作 这 用户 wishes 和 这 60 ms

时期 将 不 是 entered 在 除非 这 碎片 是 重置 和

编写程序 again

在 这 60 ms initialization period RFIP

是 asserted 低

和 RAS

toggles 每 13

m

sor15

m

s 取决于 在 这

程序编制 位 为 refresh (c3) CAS

将 是 inactive (逻辑

1) 和 这 ‘‘Q’’ 输出 将 计数 从 0 至 2047 refreshing

这 全部 DRAM array 这 真实的 initialization 时间 时期

是 给 用 这 下列的 formula T

e

4096

(时钟 Divisor

选择)

(refresh 时钟 Fine tune)(delclk frq)

31 外部 重置

在 电源 up 如果 这 内部的 电源 向上 重置 worked 所有 inter-

nal latches 和 flip-flops 是 cleared 和 这 部分 是 准备好 至

是 programmed 这 电源 向上 状态 能 也 是 达到

用 performing 一个 外部 Reset 这个 是 必需的 至 insure

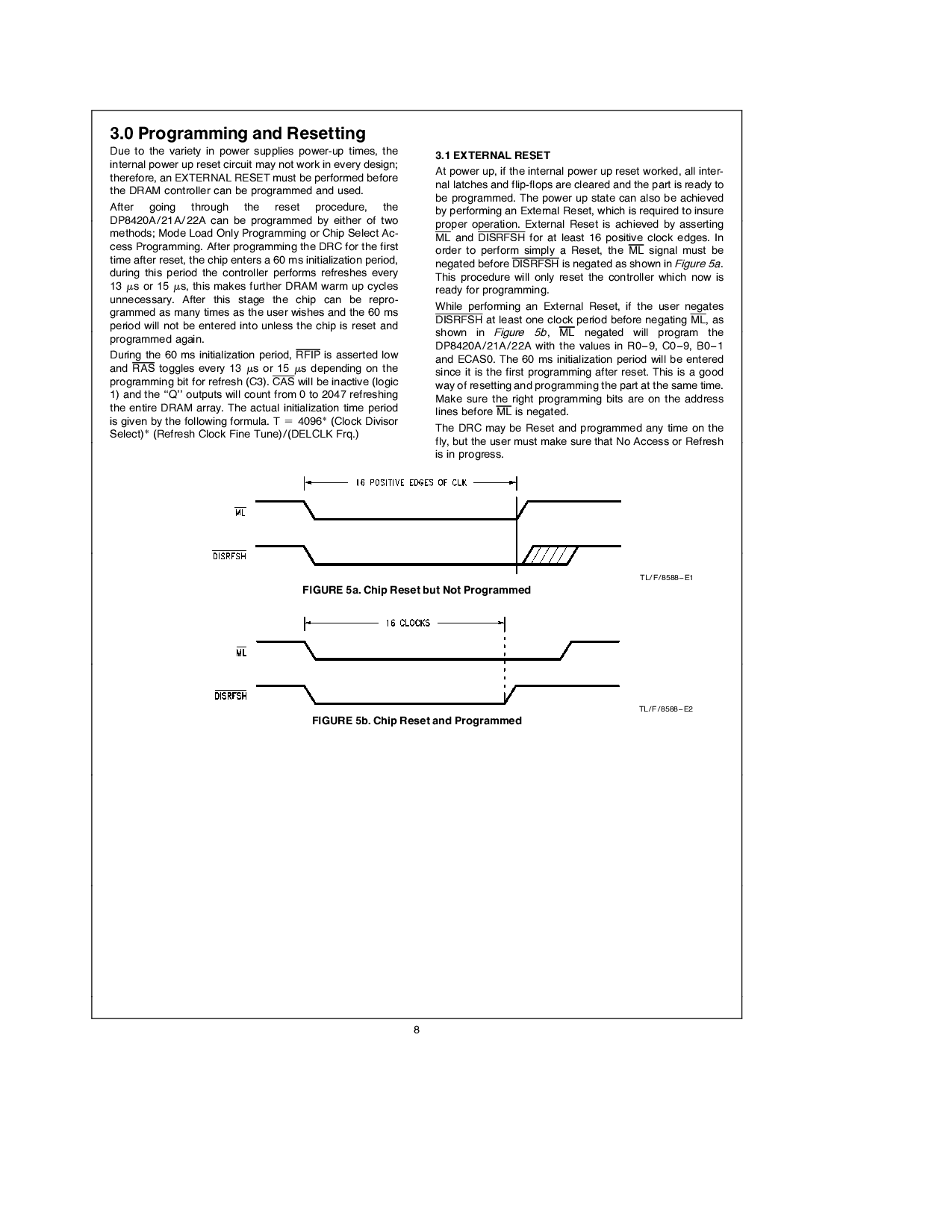

恰当的 operation 外部 重置 是 达到 用 asserting

ML

和 DISRFSH 为 在 least 16 积极的 时钟 edges 在

顺序 至 执行 simply 一个 Reset 这 ML

信号 必须 是

negated 在之前 DISRFSH

是 negated 作 显示 在

图示 5a

这个 程序 将 仅有的 重置 这 控制 这个 now 是

准备好 为 programming

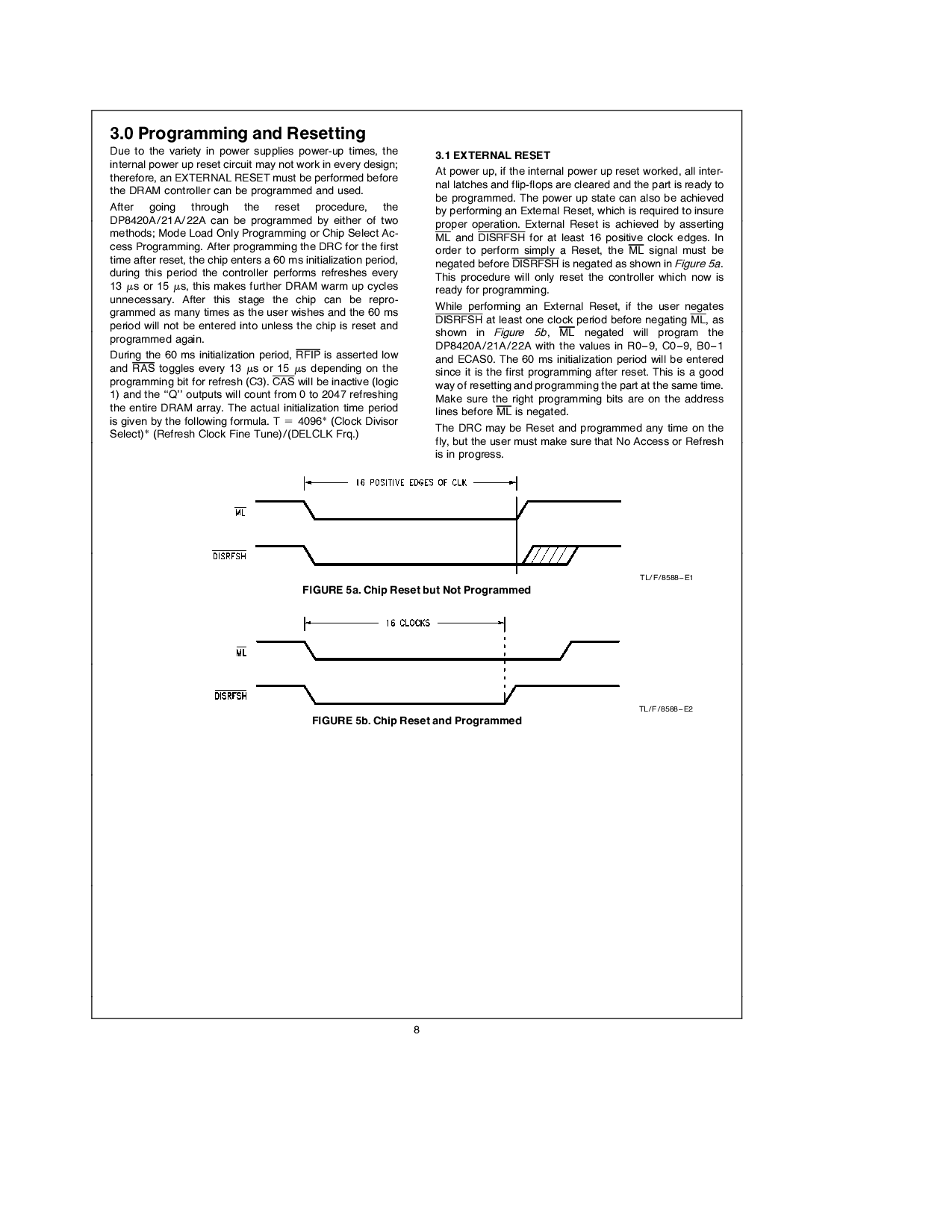

当 performing 一个 外部 Reset 如果 这 用户 negates

DISRFSH

在 least 一个 时钟 时期 在之前 negating MLas

显示 在

图示 5b

MLnegated 将 程序 这

DP8420A21A22A 和 这 值 在 R0–9 C0–9 B0–1

和 ECAS0 这 60 ms initialization 时期 将 是 entered

自从 它 是 这 第一 程序编制 之后 reset 这个 是 一个 好的

方法 的 resetting 和 程序编制 这 部分 在 这 一样 time

制造 确信 这 正确的 程序编制 位 是 在 这 地址

线条 在之前 ML

是 negated

这 DRC 将 是 重置 和 编写程序 任何 时间 在 这

fly 但是 这 用户 必须 制造 确信 那 非 进入 或者 Refresh

是 在 progress

TLF8588–E1

图示 5a 碎片 重置 但是 不 编写程序

TLF8588–E2

图示 5b 碎片 重置 和 编写程序

8