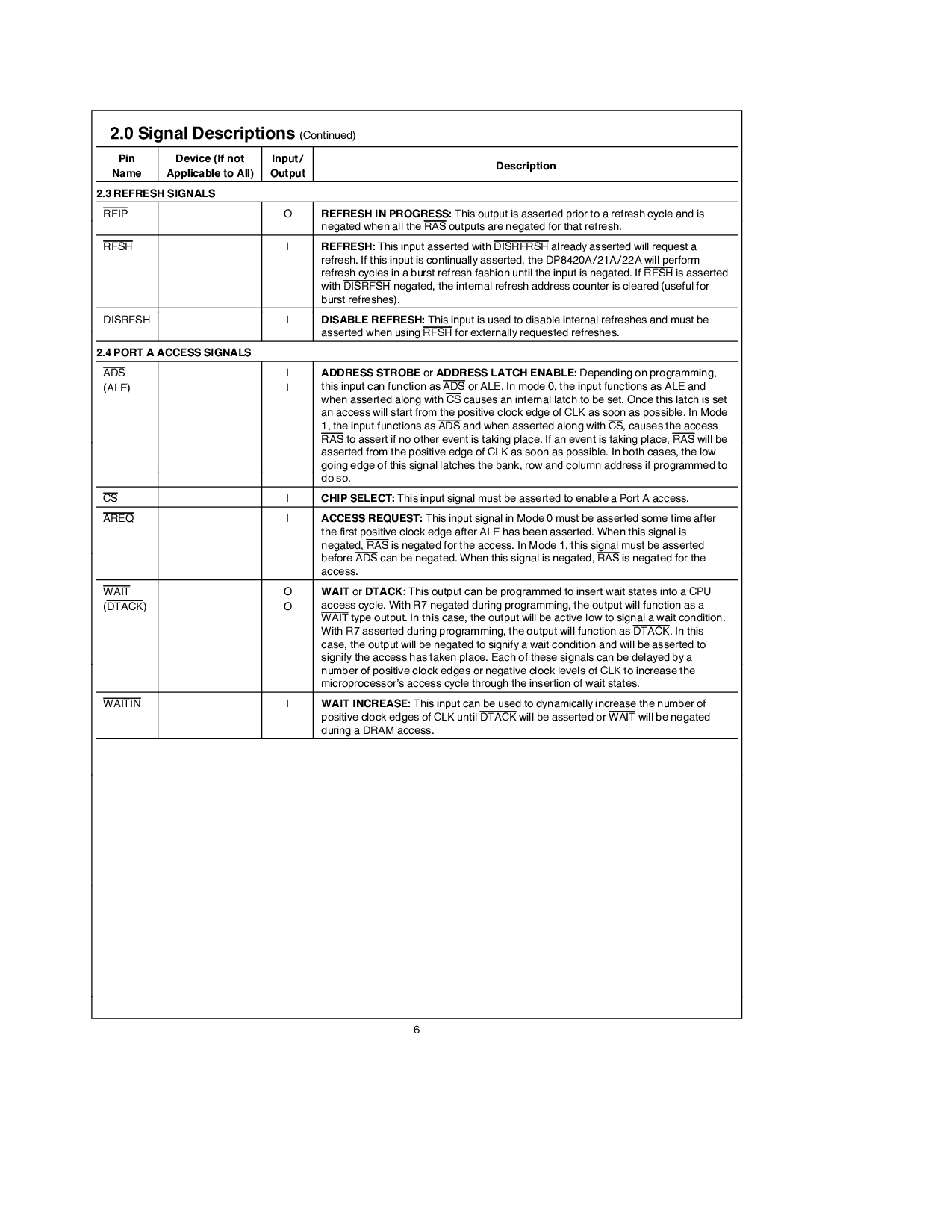

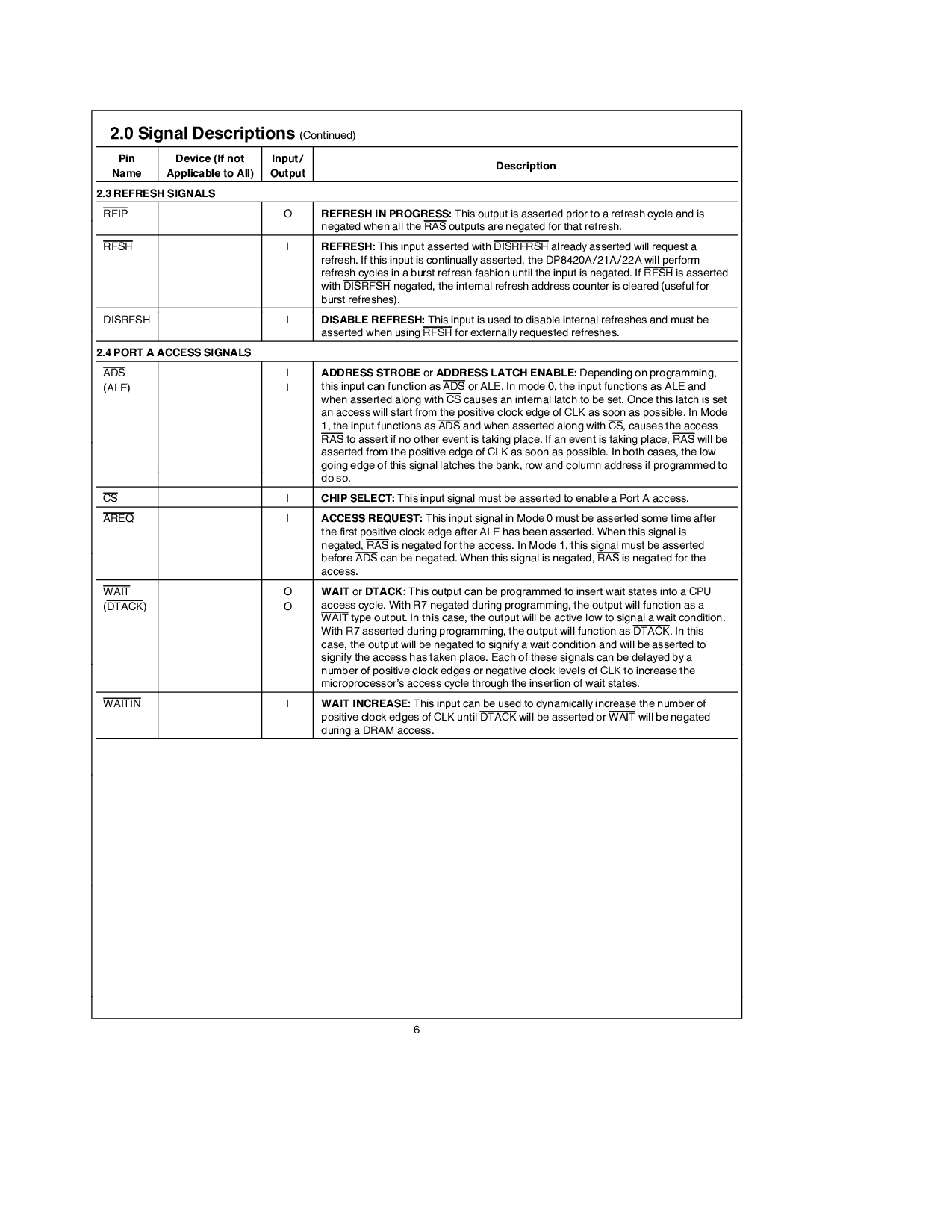

20 信号 描述

(持续)

管脚 设备 (如果 不 Input

描述

名字 适用 至 所有) 输出

23 REFRESH 信号

RFIP O

REFRESH 在 PROGRESS

这个 输出 是 asserted 较早的 至 一个 refresh 循环 和 是

negated 当 所有 这 RAS

输出 是 negated 为 那 refresh

RFSH I

REFRESH

这个 输入 asserted 和 DISRFRSH already asserted 将 要求 一个

refresh 如果 这个 输入 是 continually asserted 这 DP8420A21A22A 将 执行

refresh 循环 在 一个 burst refresh fashion 直到 这 输入 是 negated 如果 RFSH

是 asserted

和 DISRFSH

negated 这 内部的 refresh 地址 计数器 是 cleared (有用的 为

burst refreshes)

DISRFSH I

使不能运转 REFRESH

这个 输入 是 使用 至 使不能运转 内部的 refreshes 和 必须 是

asserted 当 使用 RFSH

为 externally 要求 refreshes

24 端口 一个 进入 信号

ADS I

地址 STROBE

或者

地址 获得 ENABLE

取决于 在 programming

这个 输入 能 函数 作 ADS

或者 ALE 在 模式 0 这 输入 功能 作 ALE 和

(ale) I

当 asserted along 和 CS

导致 一个 内部的 获得 至 是 set Once 这个 获得 是 设置

一个 进入 将 开始 从 这 积极的 时钟 边缘 的 CLK 作 soon 作 possible 在 模式

1 这 输入 功能 作 ADS

和 当 asserted along 和 CS 导致 这 进入

RAS

至 assert 如果 非 其它 事件 是 带去 place 如果 一个 事件 是 带去 place RAS 将 是

asserted 从 这 积极的 边缘 的 CLK 作 soon 作 possible 在 两个都 cases 这 低

going 边缘 的 这个 信号 latches 这 bank 行 和 column 地址 如果 编写程序 至

做 so

CS I

碎片 SELECT

这个 输入 信号 必须 是 asserted 至 使能 一个 端口 一个 access

AREQ I

进入 REQUEST

这个 输入 信号 在 模式 0 必须 是 asserted 一些 时间 之后

这 第一 积极的 时钟 边缘 之后 ALE 有 被 asserted 当 这个 信号 是

negated RAS

是 negated 为 这 access 在 模式 1 这个 信号 必须 是 asserted

在之前 ADS

能 是 negated 当 这个 信号 是 negated RAS 是 negated 为 这

access

WAIT O

WAIT

或者

DTACK

这个 输出 能 是 编写程序 至 insert wait states 在 一个 CPU

进入 cycle 和 R7 negated 在 programming 这 输出 将 函数 作 一个

(dtack

)o

WAIT

类型 output 在 这个 case 这 输出 将 是 起作用的 低 至 信号 一个 wait condition

和 R7 asserted 在 programming 这 输出 将 函数 作 DTACK

在 这个

case 这 输出 将 是 negated 至 signify 一个 wait 情况 和 将 是 asserted 至

signify 这 进入 有 带去 place 各自 的 这些 信号 能 是 delayed 用 一个

号码 的 积极的 时钟 edges 或者 负的 时钟 水平 的 CLK 至 增加 这

microprocessor’s 进入 循环 通过 这 嵌入 的 wait states

WAITIN I

WAIT INCREASE

这个 输入 能 是 使用 至 dynamically 增加 这 号码 的

积极的 时钟 edges 的 CLK 直到 DTACK

将 是 asserted 或者 WAIT 将 是 negated

在 一个 DRAM access

6