coolrunner-ii cpld 家族

ds090 (v1.7) october 2, 2003

www.xilinx.com

5

初步的 产品 规格

1-800-255-7778

R

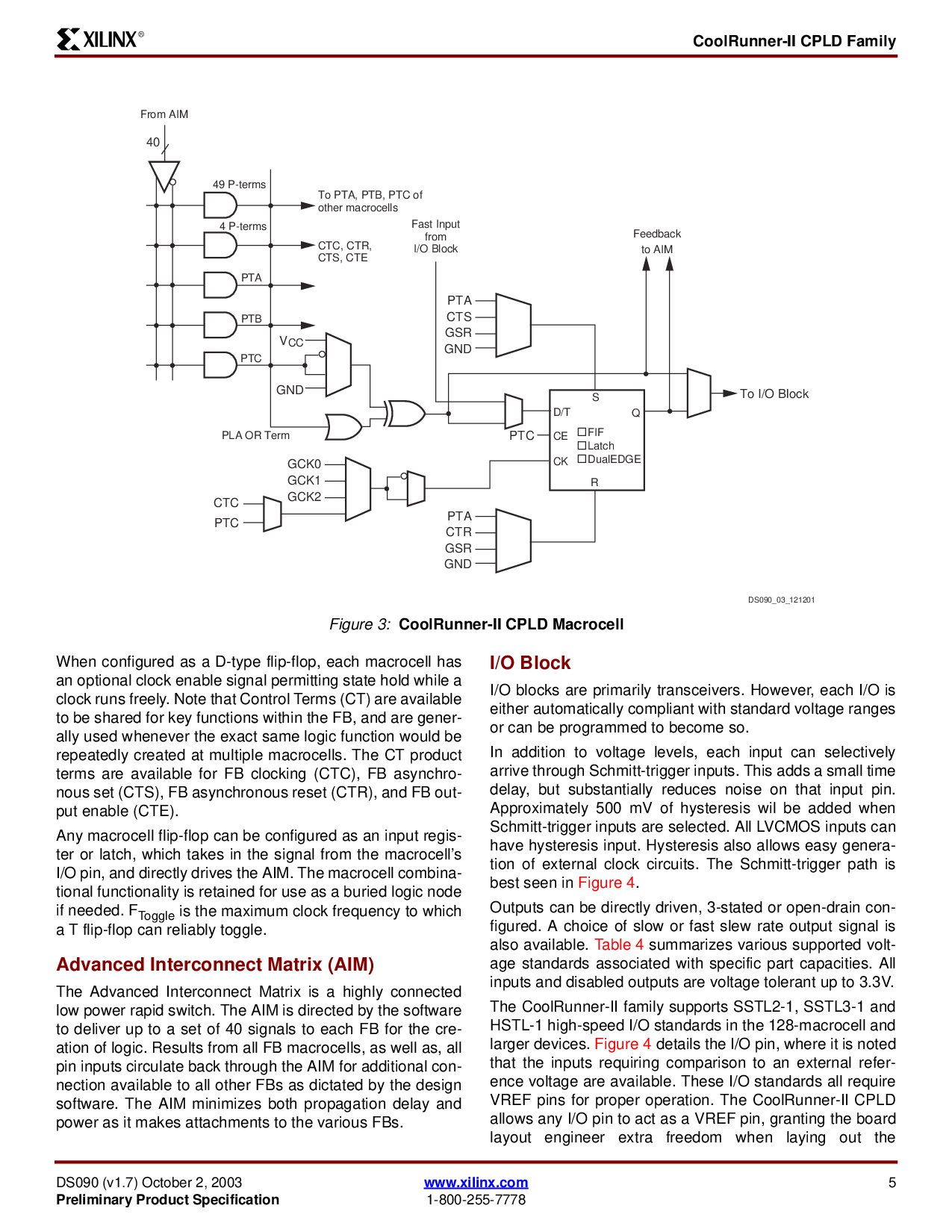

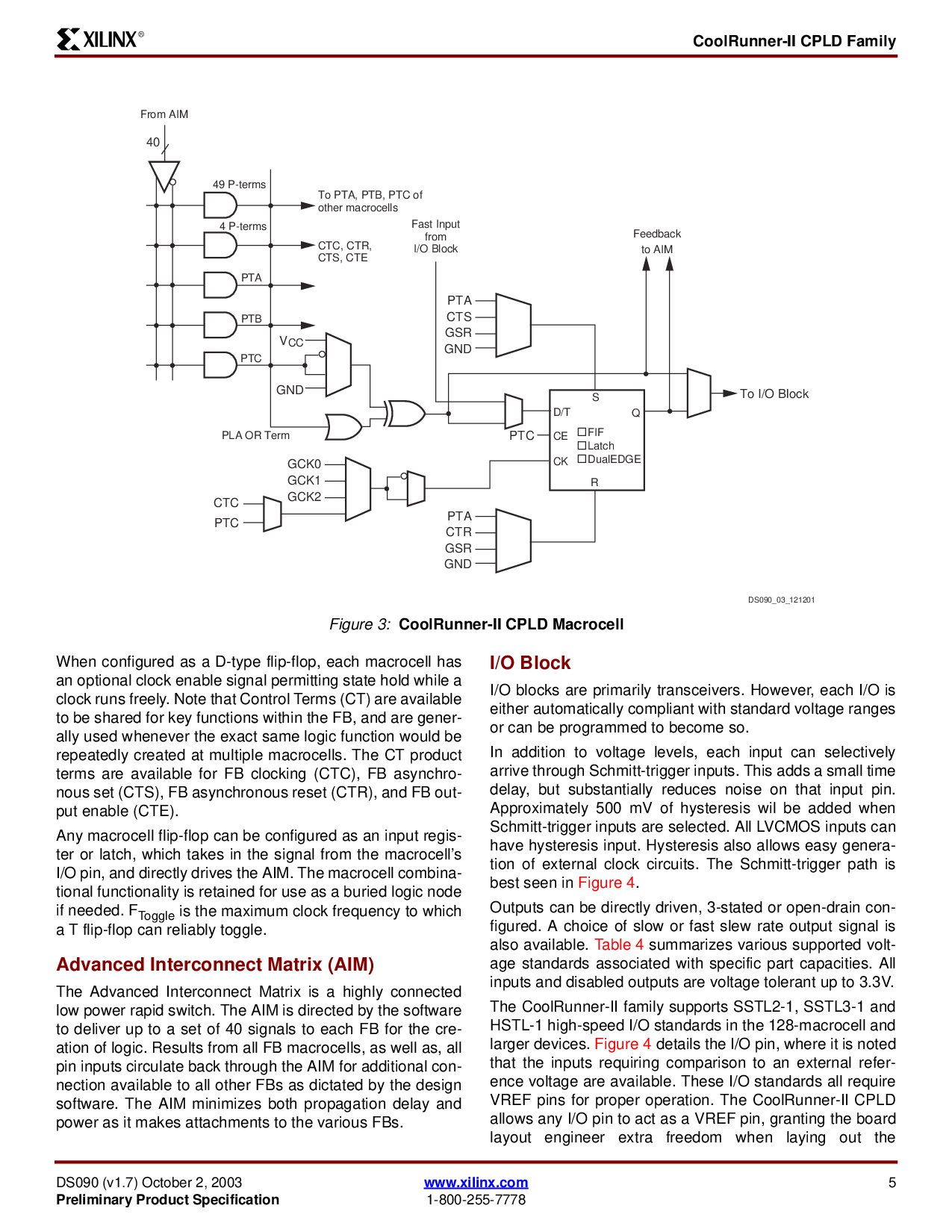

当 配置 作 一个 d-类型 flip-flop, 各自 macrocell 有

一个 optional 时钟 使能 信号 permitting 状态 支撑 当 一个

时钟 runs freely. 便条 那 控制 条款 (ct) 是 有

至 是 shared 为 关键 功能 在里面 这 fb, 和 是 gener-

ally 使用 whenever 这 精确的 一样 逻辑 函数 将 是

repeatedly 创建 在 多样的 macrocells. 这 ct 产品

条款 是 有 为 fb clocking (ctc), fb asynchro-

nous 设置 (cts), fb 异步的 重置 (ctr), 和 fb 输出-

放 使能 (cte).

任何 macrocell flip-flop 能 是 配置 作 一个 输入 regis-

ter 或者 获得, 这个 takes 在 这 信号 从 这 macrocell’s

i/o 管脚, 和 直接地 驱动 这 aim. 这 macrocell combina-

tional 符合实际 是 retained 为 使用 作 一个 buried 逻辑 node

如果 需要. f

至g gle

是 这 最大 时钟 频率 至 这个

一个 t flip-flop 能 reliably toggle.

先进的 interconnect 矩阵变换 (aim)

这 先进的 interconnect 矩阵变换 是 一个 高级地 连接

低 电源 迅速 转变. 这 aim 是 directed 用 这 软件

至 deliver 向上 至 一个 设置 的 40 信号 至 各自 fb 为 这 cre-

ation 的 逻辑. 结果 从 所有 fb macrocells, 作 好 作, 所有

管脚 输入 circulate 后面的 通过 这 aim 为 额外的 con-

nection 有 至 所有 其它 fbs 作 dictated 用 这 设计

软件. 这 aim 降低 两个都 传播 延迟 和

电源 作 它 制造 attachments 至 这 各种各样的 fbs.

i/o 块

i/o blocks 是 primarily transceivers. 不管怎样, 各自 i/o 是

也 automatically 一致的 和 标准 电压 范围

或者 能 是 编写程序 至 变为 所以.

在 增加 至 电压 水平, 各自 输入 能 selectively

arrive 通过 施密特-触发 输入. 这个 adds 一个 小 时间

延迟, 但是 substantially 减少 噪音 在 那 输入 管脚.

大概 500 mv 的 hysteresis wil 是 增加 当

施密特-触发 输入 是 选择. 所有 lvcmos 输入 能

有 hysteresis 输入. hysteresis 也 准许 容易 genera-

tion 的 外部 时钟 电路. 这 施密特-触发 path 是

最好的 seen 在图示 4.

输出 能 是 直接地 驱动, 3-陈述 或者 打开-流 con-

figured. 一个 选择 的 慢 或者 快 回转 比率 输出 信号 是

也 有.Ta bl e 4summarizes 各种各样的 supported volt-

age standards 有关联的 和 明确的 部分 capacities. 所有

输入 和 无能 输出 是 电压 tolerant 向上 至 3.3v.

这 coolrunner-ii 家族 支持 sstl2-1, sstl3-1 和

hstl-1 高-速 i/o standards 在 这 128-macrocell 和

大 设备.图示 4详细信息 这 i/o 管脚, 在哪里 它 是 指出

那 这 输入 需要 comparison 至 一个 外部 谈及-

ence 电压 是 有. 这些 i/o standards 所有 需要

vref 管脚 为 恰当的 运作. 这 coolrunner-ii cpld

准许 任何 i/o 管脚 至 act 作 一个 vref 管脚, granting 这 板

布局 engineer extra 自由 当 laying 输出 这

图示 3:

coolrunner-ii cpld macrocell

GCK0

GCK1

GCK2

CTC

PTC

PTC

ds090_03_121201

49 p-条款

至 pta, ptb, ptc 的

其它 macrocells

ctc, ctr,

cts, cte

从 aim

4 p-条款

PTA

快 输入

从

i/o 块

反馈

至 aim

PTB

PTC

pla 或者 期

PTA

CTS

GSR

地

地

V

CC

R

d/t

CE

CK

FIF

获得

DualEDGE

Q

S

40

至 i/o 块

PTA

CTR

GSR

地