coolrunner-ii cpld 家族

6

www.xilinx.com

ds090 (v1.7) october 2, 2003

1-800-255-7778

初步的 产品 规格

R

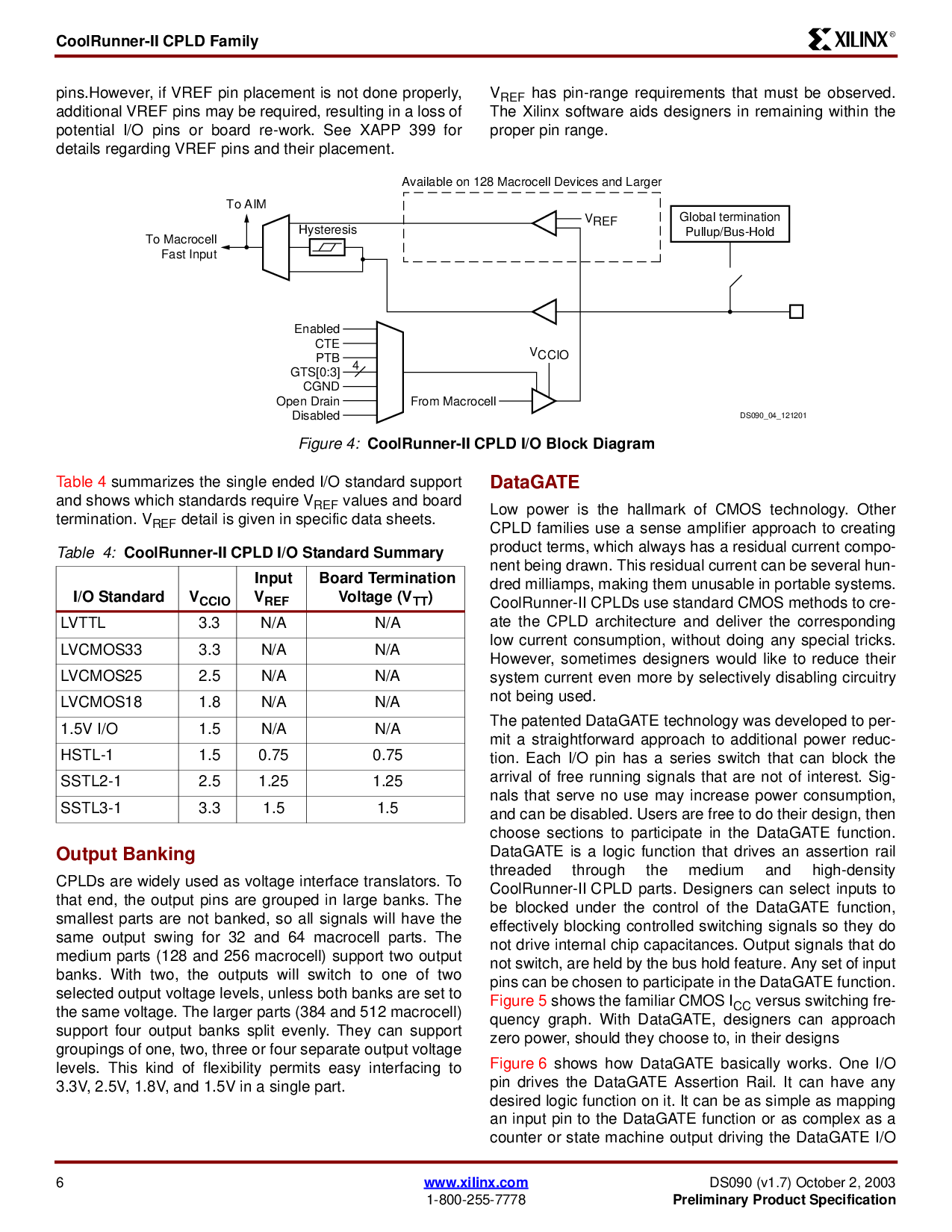

管脚.不管怎样, 如果 vref 管脚 placement 是 不 完毕 合适的,

额外的 vref 管脚 将 是 必需的, 结果 在 一个 丧失 的

潜在的 i/o 管脚 或者 板 re-工作. 看 xapp 399 为

详细信息 关于 vref 管脚 和 它们的 placement.

V

REF

有 管脚-范围 (所需的)东西 那 必须 是 observed.

这 xilinx 软件 aids designers 在 remaining 在里面 这

恰当的 管脚 范围.

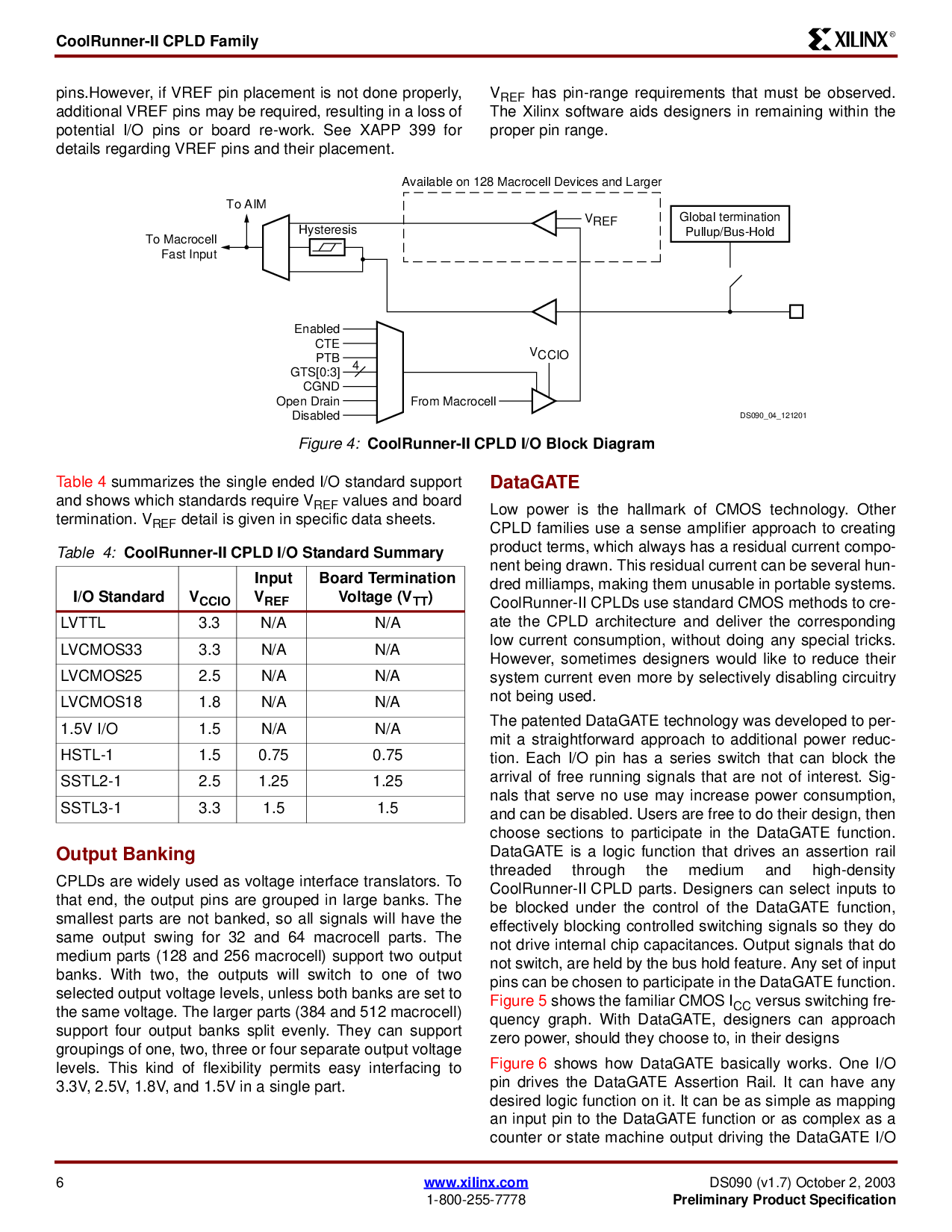

Ta ble 4summarizes 这 单独的 结束 i/o 标准 支持

和 显示 这个 standards 需要 v

REF

值 和 板

末端. v

REF

detail 是 给 在 明确的 数据 薄板.

输出 banking

cplds 是 widely 使用 作 电压 接口 翻译. 至

那 终止, 这 输出 管脚 是 grouped 在 大 banks. 这

smallest 部分 是 不 banked, 所以 所有 信号 将 有 这

一样 输出 摆动 为 32 和 64 macrocell 部分. 这

中等 部分 (128 和 256 macrocell) 支持 二 输出

banks. 和 二, 这 输出 将 转变 至 一个 的 二

选择 输出 电压 水平, 除非 两个都 banks 是 设置 至

这 一样 电压. 这 大 部分 (384 和 512 macrocell)

支持 四 输出 banks 分割 evenly. 它们 能 支持

groupings 的 一个, 二, 三 或者 四 独立的 输出 电压

水平. 这个 kind 的 flexibility 准许 容易 接合 至

3.3v, 2.5v, 1.8v, 和 1.5v 在 一个 单独的 part.

DataGATE

低 电源 是 这 hallmark 的 cmos 技术. 其它

cpld families 使用 一个 sense 放大器 approach 至 creating

产品 条款, 这个 总是 有 一个 residual 电流 混合-

nent 正在 描绘. 这个 residual 电流 能 是 一些 hun-

dred milliamps, 制造 它们 unusable 在 可携带的 系统.

coolrunner-ii cplds 使用 标准 cmos 方法 至 cre-

ate 这 cpld architecture 和 deliver 这 相应的

低 电流 消耗量, 没有 做 任何 特定的 tricks.

不管怎样, sometimes designers 将 像 至 减少 它们的

系统 电流 甚至 更多 用 selectively disabling 电路系统

不 正在 使用.

这 专利的 datagate 技术 是 开发 至 每-

mit 一个 straightforward approach 至 额外的 电源 reduc-

tion. 各自 i/o 管脚 有 一个 序列 转变 那 能 块 这

arrival 的 自由 运动 信号 那 是 不 的 interest. sig-

nals 那 提供 非 使用 将 增加 电源 消耗量,

和 能 是 无能. 用户 是 自由 至 做 它们的 设计, 然后

choose sections 至 participate 在 这 datagate 函数.

datagate 是 一个 逻辑 函数 那 驱动 一个 assertion 栏杆

threaded 通过 这 中等 和 高-密度

coolrunner-ii cpld 部分. designers 能 选择 输入 至

是 blocked 下面 这 控制 的 这 datagate 函数,

effectively blocking 控制 切换 信号 所以 它们 做

不 驱动 内部的 碎片 capacitances. 输出 信号 那 做

不 转变, 是 使保持 用 这 总线 支撑 特性. 任何 设置 的 输入

管脚 能 是 选择 至 participate 在 这 datagate 函数.

图示 5显示 这 familiar cmos i

CC

相比 切换 fre-

quency 图表. 和 datagate, designers 能 approach

零 电源, 应当 它们 choose 至, 在 它们的 设计

图示 6显示 如何 datagate basically 工作. 一个 i/o

管脚 驱动 这 datagate assertion 栏杆. 它 能 有 任何

desired 逻辑 函数 在 它. 它 能 是 作 简单的 作 mapping

一个 输入 管脚 至 这 datagate 函数 或者 作 complex 作 一个

计数器 或者 状态 机器 输出 驱动 这 datagate i/o

图示 4:

coolrunner-ii cpld i/o 块 图解

使能

至 macrocell

快 输入

至 aim

4

CTE

PTB

gts[0:3]

CGND

打开 流

从 macrocell

V

CCIO

V

REF

无能

Hysteresis

有 在 128 macrocell 设备 和 大

global 末端

pullup/总线-支撑

ds090_04_121201

表格 4:

coolrunner-ii cpld i/o 标准 summary

i/o 标准 V

CCIO

输入

V

REF

板 末端

电压 (v

TT

)

LVTTL 3.3 n/一个 n/一个

LVCMOS33 3.3 n/一个 n/一个

LVCMOS25 2.5 n/一个 n/一个

LVCMOS18 1.8 n/一个 n/一个

1.5v i/o 1.5 n/一个 n/一个

hstl-1 1.5 0.75 0.75

sstl2-1 2.5 1.25 1.25

sstl3-1 3.3 1.5 1.5