K4S161622D cmos sdram

交流 运行 测试 情况

(vDD= 3.3v

±

0.3v

*2

, t一个= 0 至 70

°

c)

参数 值 单位

输入 水平 (vih/vil) 2.4 / 0.4 V

输入 定时 度量 涉及 水平的 1.4 V

输入 上升 和 下降 时间 tr / tf = 1 / 1 ns

输出 定时 度量 涉及 水平的 1.4 V

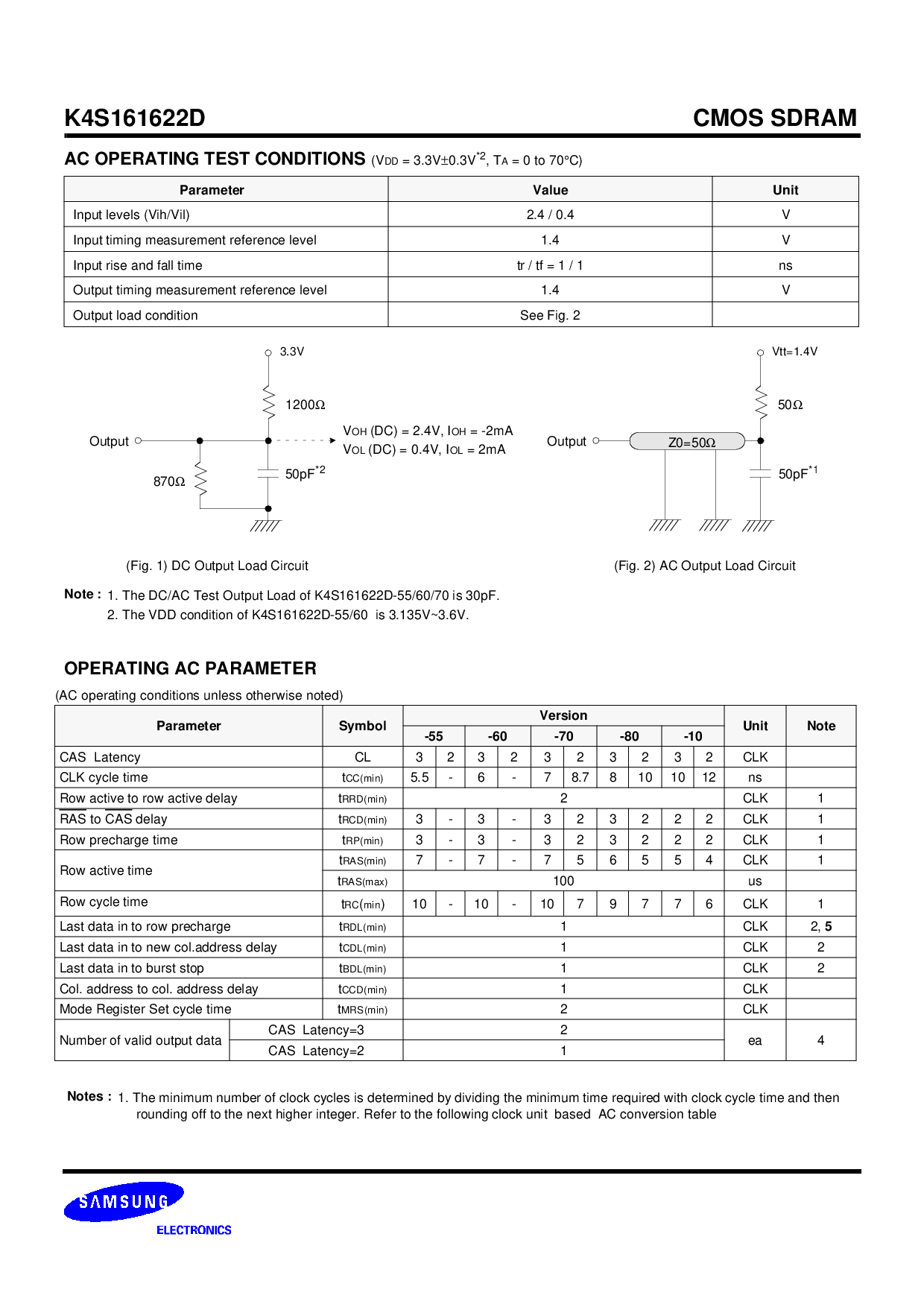

输出 加载 情况 看 图. 2

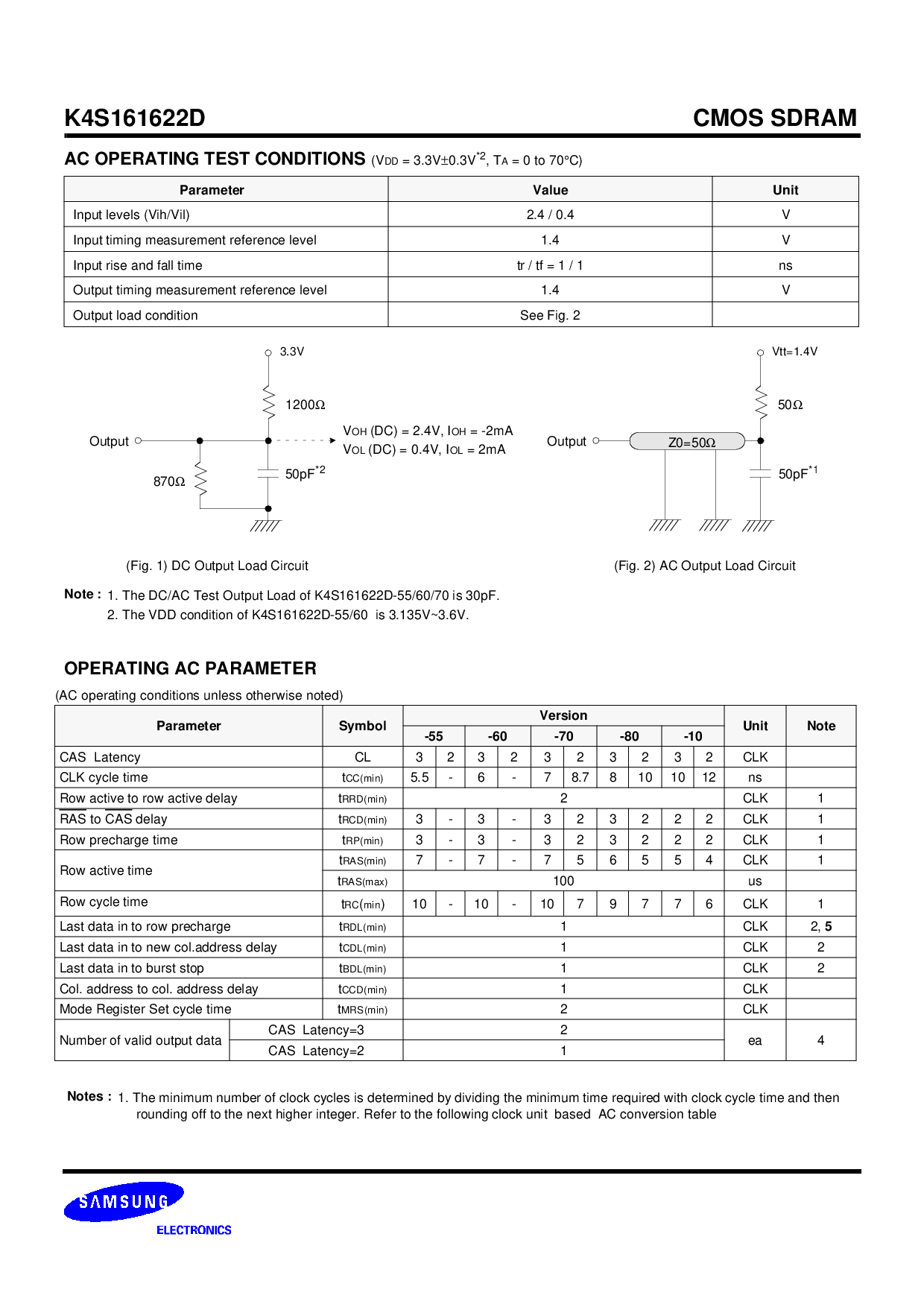

3.3v

1200

Ω

870

Ω

输出

VOH(直流) = 2.4v, iOH= -2ma

VOL(直流) = 0.4v, iOL= 2ma

vtt=1.4v

50

Ω

输出

Z0=50

Ω

(图. 2) 交流 输出 加载 电路(图. 1) 直流 输出 加载 电路

1. 这 直流/交流 测试 输出 加载 的 k4s161622d-55/60/70 是 30pf.

2. 这 vdd 情况 的 k4s161622d-55/60 是 3.135v~3.6v.

便条 :

50pF

*2

50pF

*1

1. 这 最小 号码 的 时钟 循环 是 决定 用 dividing 这 最小 时间 必需的 和 时钟 循环 时间 和 然后

rounding 止 至 这 next 高等级的 integer. 谈及 至 这 下列的 时钟 单位 为基础 交流 转换 表格

注释 :

运行 交流 参数

(交流 运行 情况 除非 否则 指出)

参数 标识

版本

单位 便条

-55 -60 -70 -80 -10

cas latency CL 3 2 3 2 3 2 3 2 3 2 CLK

clk 循环 时间 tcc(最小值) 5.5 - 6 - 7 8.7 8 10 10 12 ns

行 起作用的 至 行 起作用的 延迟 trrd(最小值) 2 CLK 1

RAS至CAS延迟 trcd(最小值) 3 - 3 - 3 2 3 2 2 2 CLK 1

行 precharge 时间 trp(最小值) 3 - 3 - 3 2 3 2 2 2 CLK 1

行 起作用的 时间

tras(最小值) 7 - 7 - 7 5 6 5 5 4 CLK 1

tras(最大值) 100 美国

行 循环 时间

tRC(最小值) 10 - 10 - 10 7 9 7 7 6 CLK 1

last 数据 在 至 行 precharge trdl(最小值) 1 CLK 2,

5

last 数据 在 至 新 col.地址 延迟 tcdl(最小值) 1 CLK 2

last 数据 在 至 burst 停止 tbdl(最小值) 1 CLK 2

col. 地址 至 col. 地址 延迟 tccd(最小值) 1 CLK

模式 寄存器 设置 循环 时间 tmrs(最小值) 2 CLK

号码 的 有效的 输出 数据

cas latency=3 2

ea 4

cas latency=2 1