VITESSE

半导体 公司

数据 薄板

VSC8140

2.48832gb/s 16:1 sonet/sdh

transceiver 和 整体的 时钟 发生器

页 4

VITESSE

半导体 公司

741 calle plano, camarillo, ca 93012 • 805/388-3700 • 传真: 805/987-5896 9/6/00

g52251-0, rev. 4.0

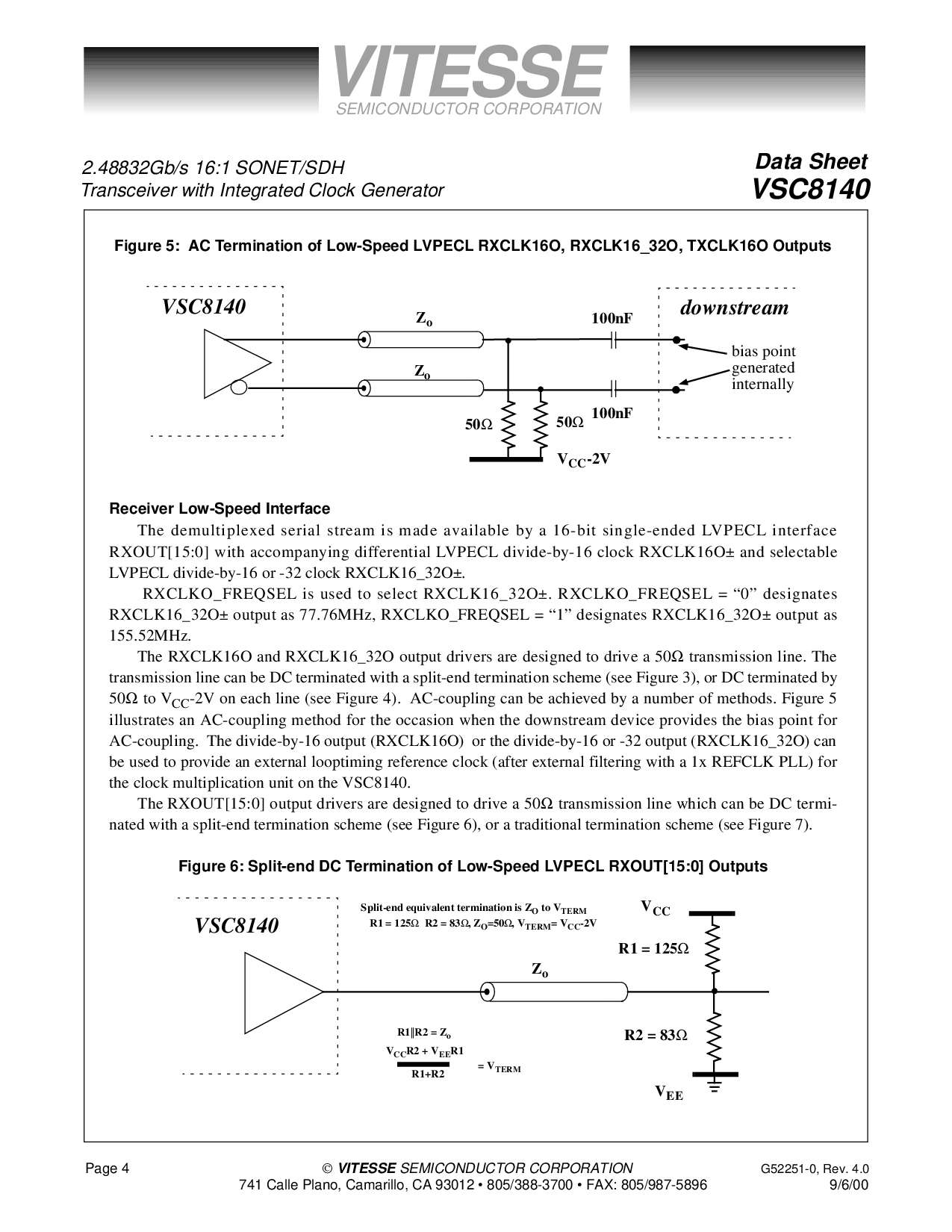

图示 5: 交流 末端 的 低-速 lvpecl rxclk16o, rxclk16_32o, txclk16o 输出

接受者 低-速 接口

这 demultiplexed 串行 stream 是 制造 有 用 一个 16-位 单独的-结束 lvpecl 接口

rxout[15:0] 和 accompanying 差别的 lvpecl 分隔-用-16 时钟 rxclk16o

±

和 可选择的

lvpecl 分隔-用-16 或者 -32 时钟 rxclk16_32o

±

.

rxclko_freqsel 是 使用 至 选择 rxclk16_32o

±

. rxclko_freqsel = “0” designates

rxclk16_32o

±

输出 作 77.76mhz, rxclko_freqsel = “1” designates rxclk16_32o

±

输出 作

155.52mhz.

这 rxclk16o 和 rxclk16_32o 输出 驱动器 是 设计 至 驱动 一个 50

Ω

传递 线条. 这

传递 线条 能 是 直流 terminated 和 一个 分割-终止 末端 scheme (看 图示 3), 或者 直流 terminated 用

50

Ω

至 v

CC

-2v 在 各自 线条 (看 图示 4). 交流-连接 能 是 达到 用 一个 号码 的 methods. 图示 5

illustrates 一个 交流-连接 方法 为 这 occasion 当 这 downstream 设备 提供 这 偏差 要点 为

交流-连接. 这 分隔-用-16 输出 (rxclk16o) 或者 这 分隔-用-16 或者 -32 输出 (rxclk16_32o) 能

是 使用 至 提供 一个 外部 looptiming 涉及 时钟 (之后 外部 过滤 和 一个 1x refclk pll) 为

这 时钟 multiplication 单位 在 这 vsc8140.

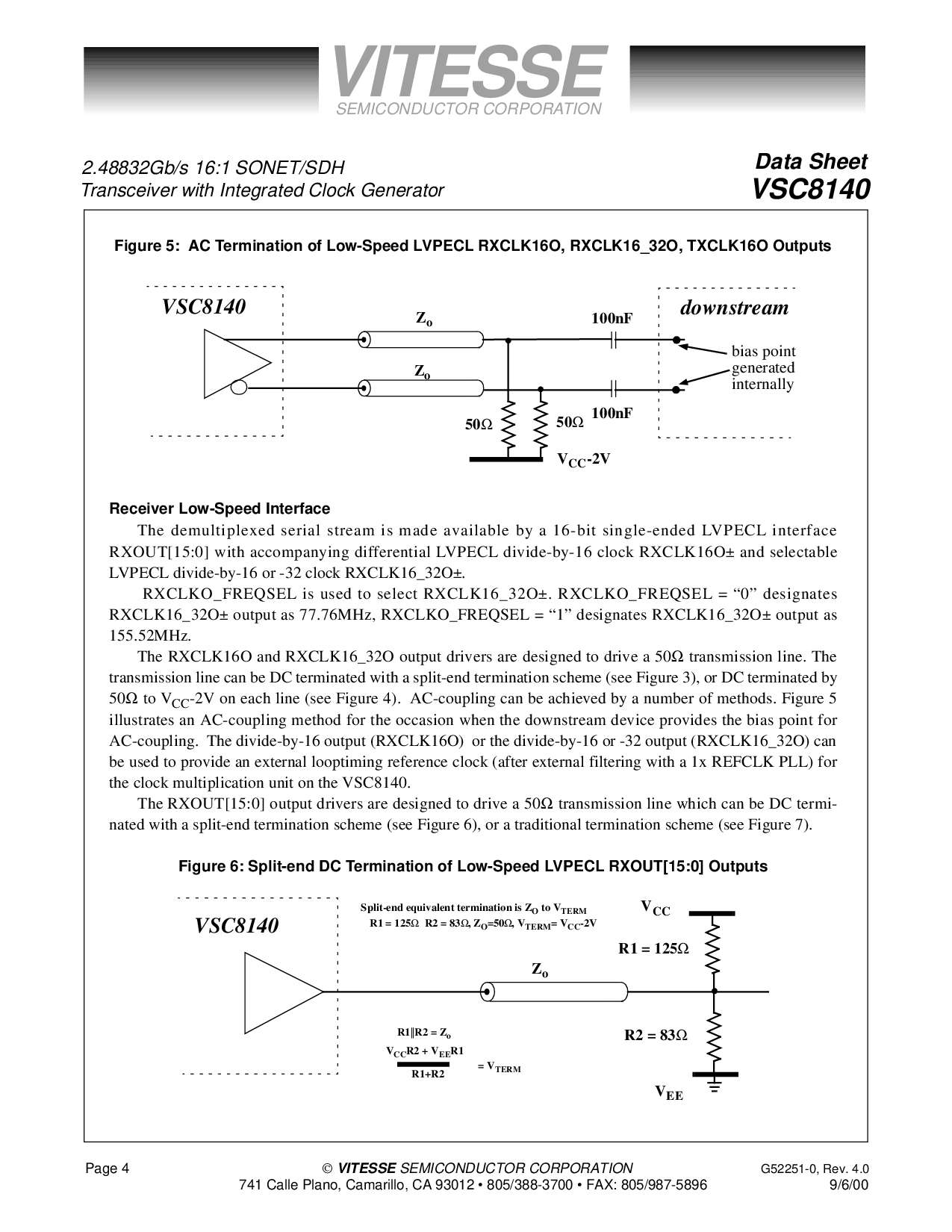

这 rxout[15:0] 输出 驱动器 是 设计 至 驱动 一个 50

Ω

传递 线条 这个 能 是 直流 termi-

nated 和 一个 分割-终止 末端 scheme (看 图示 6), 或者 一个 传统的 末端 scheme (看 图示 7).

图示 6: 分割-终止 直流 末端 的 低-速 lvpecl rxout[15:0] 输出

VSC8140

100nF

50

Ω

50

Ω

Z

o

Z

o

100nF

V

CC

-2v

downstream

偏差 要点

发生

内部

VSC8140

Z

o

r1 = 125

Ω

V

EE

V

CC

r2 = 83

Ω

分割-终止 相等的 末端 是 z

O

至 v

期

r1 = 125

Ω

r2 = 83

Ω

, z

O

=50

Ω

, v

期

= v

CC

-2v

V

CC

r2 + v

EE

R1

R1+R2

= v

期

R1

||

r2 = z

o