K4S161622D cmos sdram

这 k4s161622d 是 16,777,216 位 同步的 高 数据

比率 动态 内存 有组织的 作 2 x 524,288 words 用 16 位,

fabricated 和 samsung

′

s 高 效能 cmos technol-

ogy. 同步的 设计 准许 准确的 循环 控制 和 这

使用 的 系统 时钟 i/o transactions 是 可能 在 每 时钟

循环. 范围 的 运行 发生率, 可编程序的 burst

长度 和 可编程序的 latencies 准许 这 一样 设备 至 是

有用的 为 一个 多样性 的 高 带宽, 高 效能 mem-

ory 系统 产品.

• 3.3v 电源 供应

•lvttl 兼容 和 多路复用 地址

•双 banks 运作

•mrs 循环 和 地址 关键 programs

-. cas latency ( 2 &放大; 3)

-. burst 长度 (1, 2, 4, 8 & 全部 page)

-. burst 类型 (sequential &放大; interleave)

•所有 输入 是 抽样 在 这 积极的 going 边缘 的 这 系统

时钟

• burst 读 单独的-位 写 运作

• dqm 为 masking

• 自动 &放大; 自 refresh

•15.6us refresh 职责 循环 (2k/32ms)

一般 描述特性

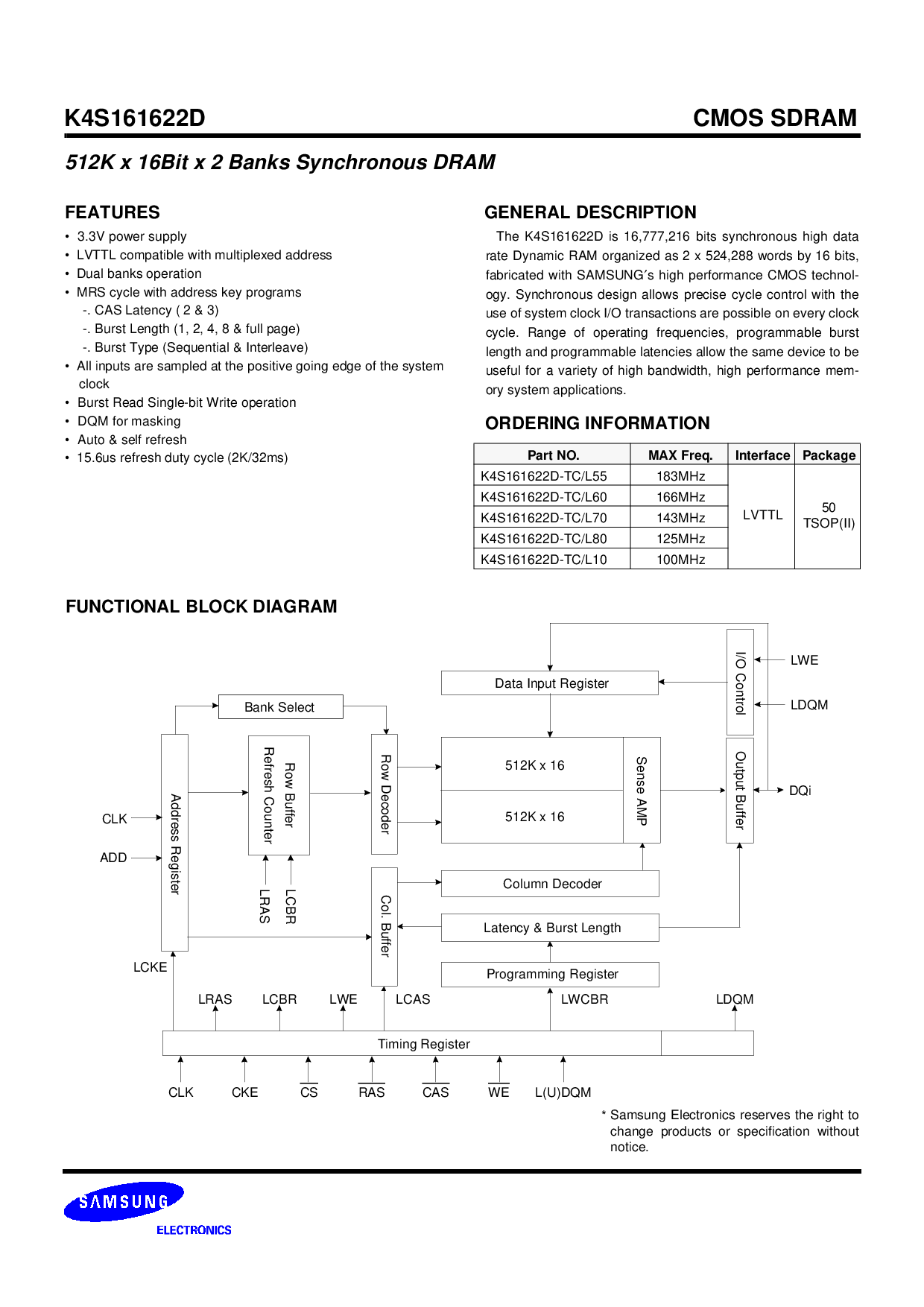

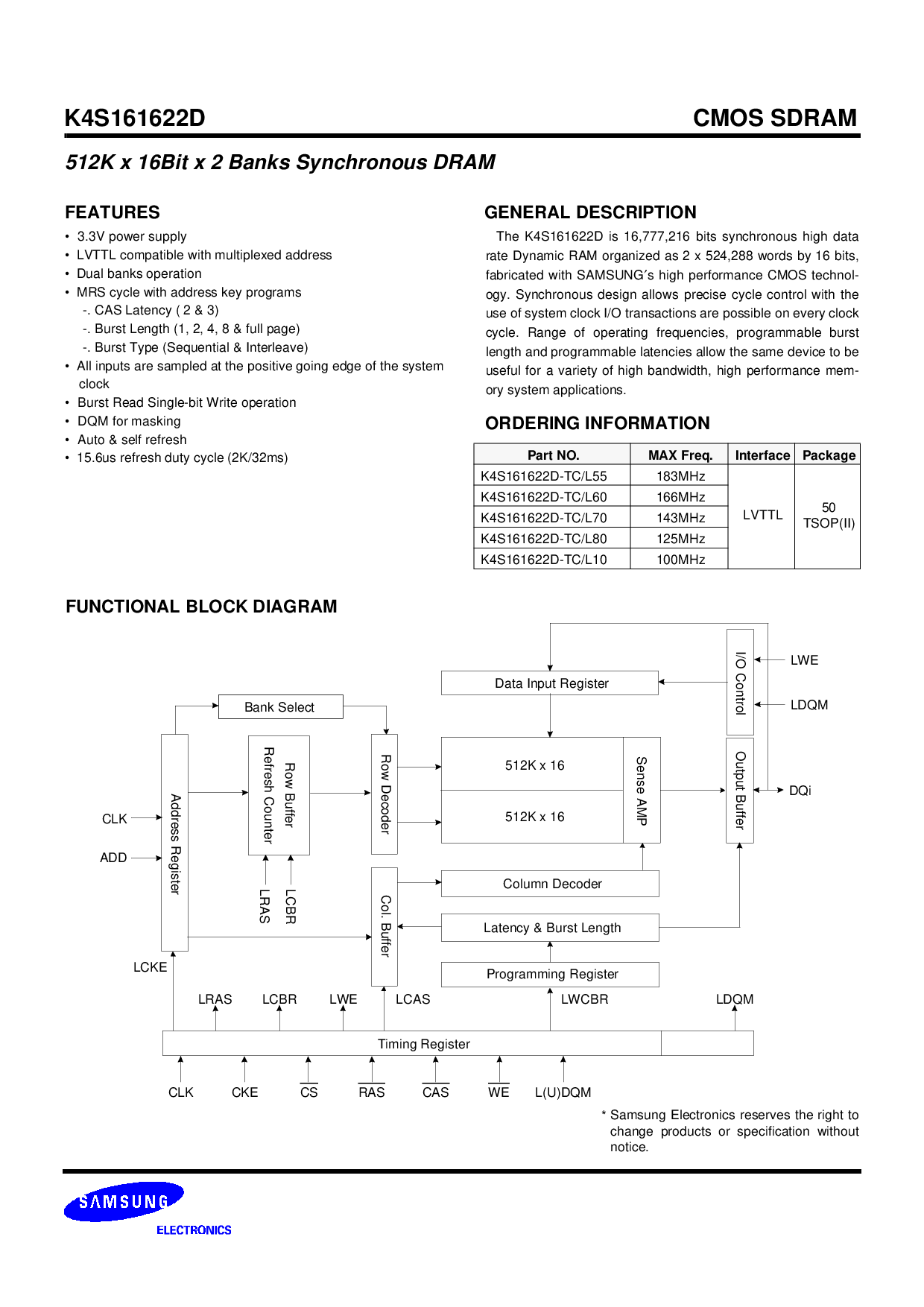

函数的 块 图解

512k x 16bit x 2 banks 同步的 dram

订货 信息

部分 非. 最大值 freq. 接口 包装

k4s161622d-tc/l55 183MHz

LVTTL

50

tsop(ii)

k4s161622d-tc/l60 166MHz

k4s161622d-tc/l70 143MHz

k4s161622d-tc/l80 125MHz

k4s161622d-tc/l10 100MHz

samsung electronics reserves 这 正确的 至

改变 产品 或者 规格 没有

注意.

*

bank 选择

数据 输入 寄存器

512k x 16

512k x 16

sense 放大

输出 bufferi/o 控制

column 解码器

latency &放大; burst 长度

程序编制 寄存器

地址 寄存器

行 缓存区

refresh 计数器

行 解码器 col. 缓存区

LRAS

LCBR

LCKE

LRAS LCBR LWE LDQM

CLK CKE CS RAS CAS 我们 l(u)dqm

LWE

LDQM

DQi

CLK

增加

LCAS LWCBR

定时 寄存器